Изобретение относится к измерительной и вычисл 1тельной технике. Счетчик может быть иснользован в различных автоматнческих, логических и 1И1формационных устройствах.

Известны кольцевые счетчики на токовых перекл)очателях с эмиттерными связями, состоящие из нечетного числа ячеек, у которых базы первых транзисторных ключей всех ячеек соединены вместе и образуют счетный вход схемы.

Рабочая частота известных счетчиков при одних и тех же параметрах транзисторов ключей тем выше, чем больше в допустимых пределах переключаемый ток. Ток через элемент перекрестной связи должен превышать более чем вдвое токи транзисторных ключей. Это приводит к тому, что нрн одинаковых величинах предельных токов транзисторных ключей и элементов перекрестных связей или при одинаковых их предельных мош,ностях, что особенно характерно для транзисторных микроэлектронных компонентов электронных схем, через транзисторы токовых ключей может протекать ток в два раза меньше возможного. Поэтому схема не позволяет повысить быстродействие счетчика за счет увеличения переключаемого тока.

Поскольку напряжение стабилизации на элементах перекрестных связей составляет величину иорядка 5-8 в, а напряжение источника питания схемы должно более чем вдвое превышать напряжепие стабилизации элементов перекрестных связей, на коллекторном сопротивлении транзисторного ключа рассеивается значительная мош.ность.

Как следствие того, что через элемент перекрестной связи ячейки необходимо пропускать ток, нревышаюш,ий более чем вдвое токи транзисторных ключей, известная схема счетчика обладает высоким уровнем напряжения логического нуля, что в ряде случаев затрудняет дешифрацию кода числа, заиисанного в счетчике.

Цель изобретения - уменьшение потребляемой мошности, новышение быстродействия схемы и снижение уровня напряжения логического нуля-достигается тем, что коллектор первого транзистора ключа «-той ячейки предлагаемого счетчика соединен с базой второго транзисторного ключа дайной ячейки через транзистор, включенный по схеме с обш,им коллектором, причем выходами счетчика являются нагрузочные сопротивления ключей.

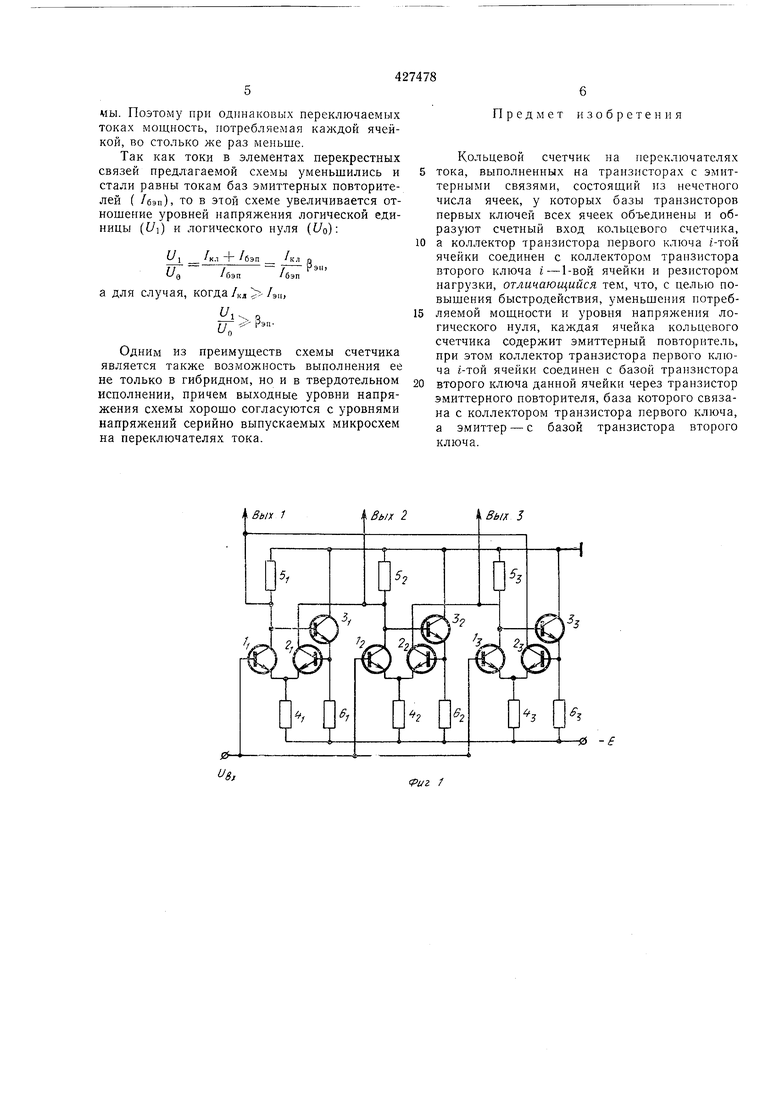

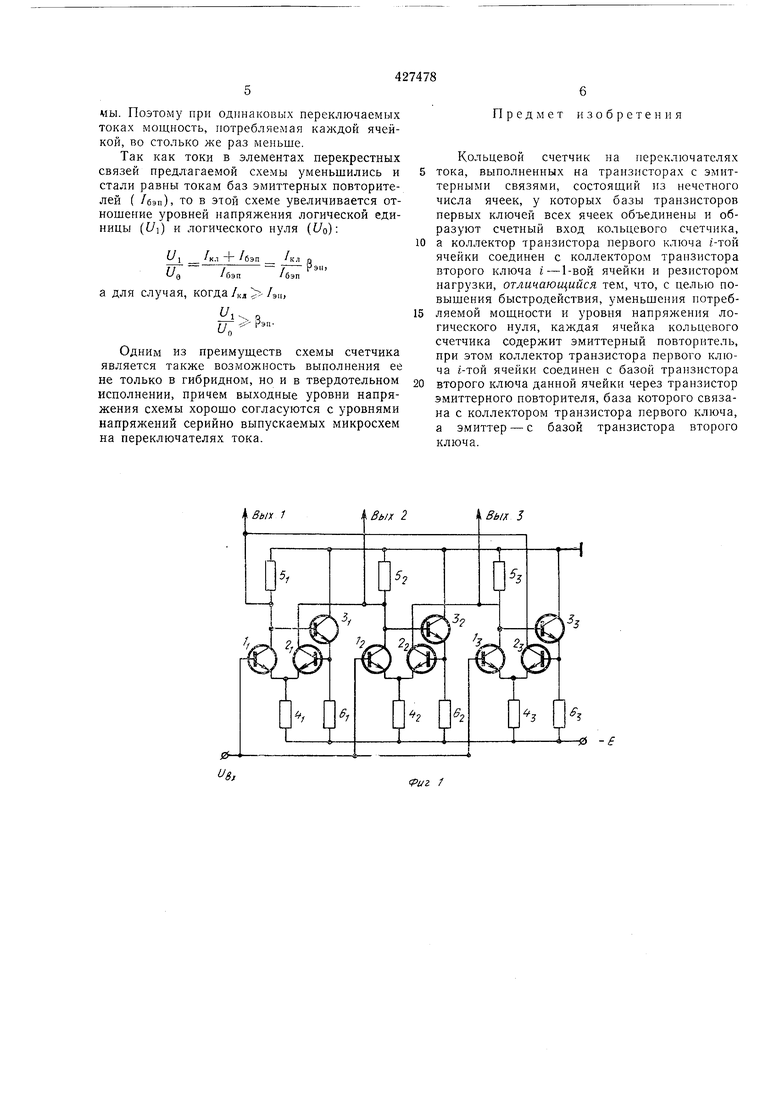

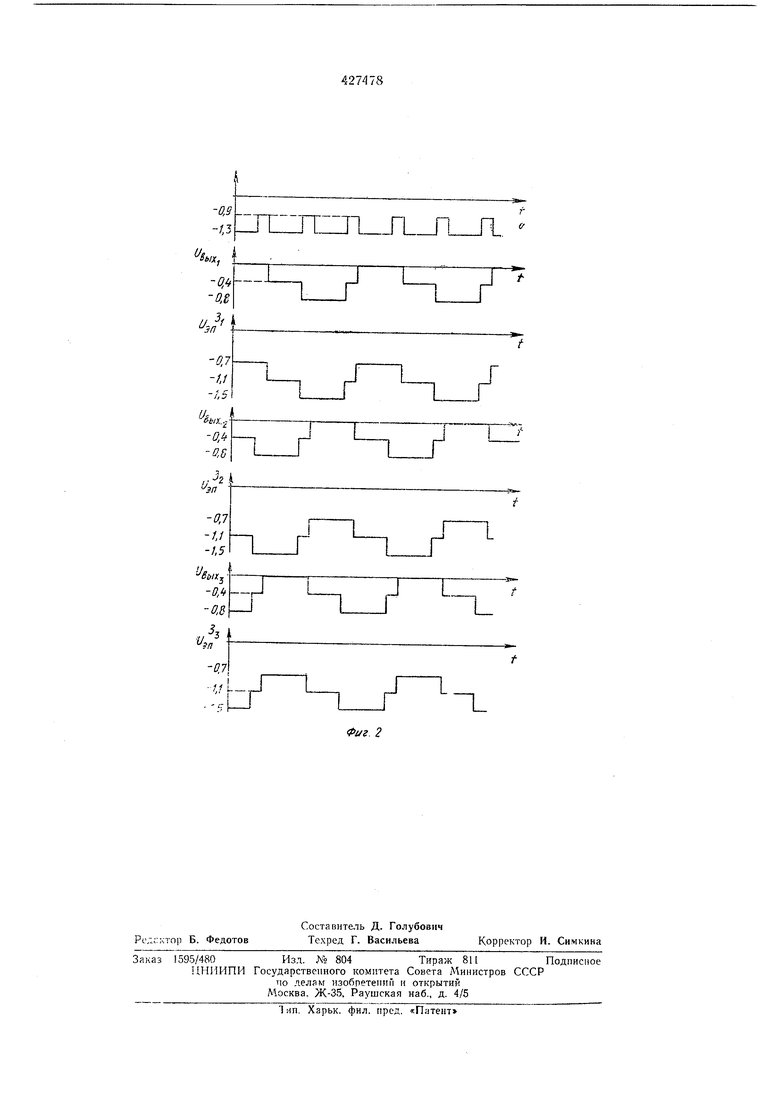

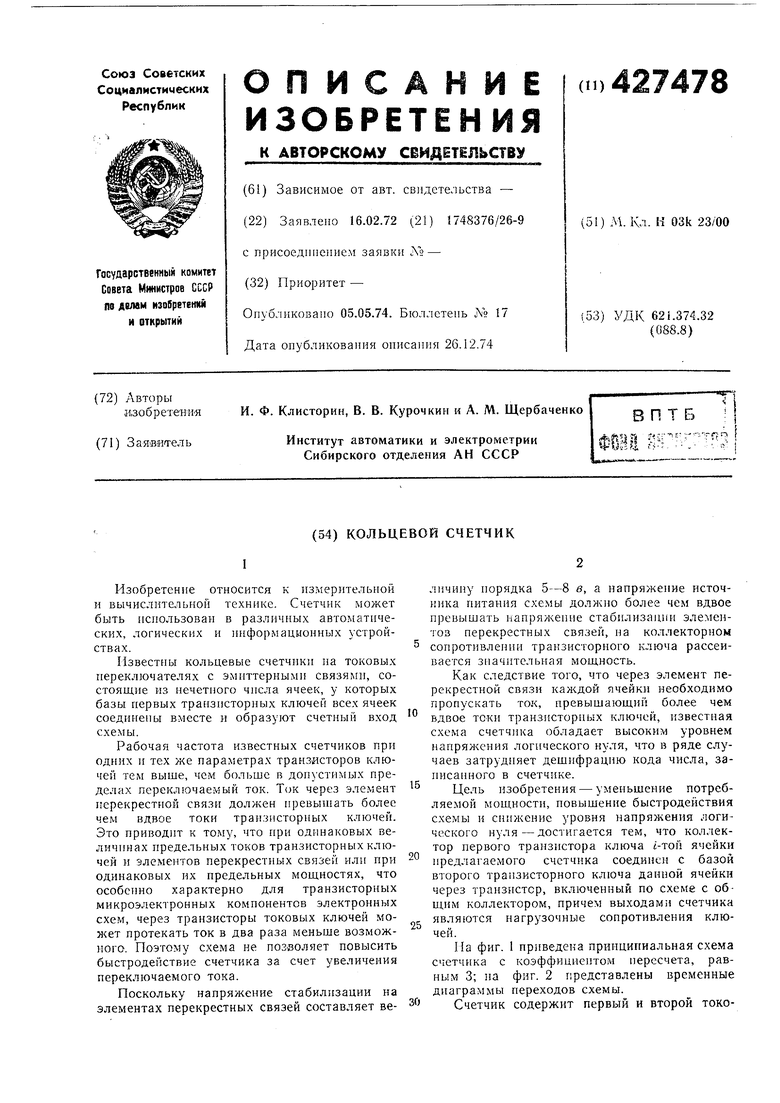

Па фиг. 1 приведена прииципиальная схема счетчика с коэффициентом пересчета, равным 3; па фиг. 2 представлены временные диаграммы переходов схемы.

Счетчик содержит первый и второй токовые ключи /1 и 2i, Iz и , /з и 2 первой, второй и третьей ячеек соответственно; эмиттерные шовторители 3, 3, 3, эмиттер.ные резисторы транзисторных ключей 4i, 4, 4, резисторы нагрузки токовых ключей 5i, 5-, 5з, эмиттерные резисторы эмиттерного повторителя (ь 2, 3.

В исходном состоянии на первом выходе схемы счетчика (фиг. 1) зстанавливается нулевое напряжение, на втором (-0,4) в, на третьем (-0,8) в. Для этого транзисторы 2, 22, h токовых ключей должны быть открыты, транзисторы /1, 1-2, 2z-закрыты. Так как на переходах база - эмиттер кремниевых транзисторов напряжение падает (, в, то на выходах эмиттерных повторителей устанавливают напряжения: (0,7) 0; 2-( -1,1) о; ,2-(-1,5) в. Чтобы сохранилось исходное состояние ячеек схемы, на счетном входе схемы должен быть потенциал -il,5

-1,1 8.

Таким образом, если на счетном входе схемы сохраняется напряжение в,о - 1,3, схема в этом состоянии может находиться сколь угодно долго.

С поступлением первого импульса входное напряжение понижается до -0,9 в. Поэтому напряжение на базе транзистора /а становится меньше, чем на базе транзистора РЗ, а отношение между базовыми напряжениями остальных пар токовых ключей сохраняется прежним. Это приводит к тому, что токовый ключ /2 открывается, а ключ Рг запирается. На первом выходе схемы устанавливается нулевое напряжение, на втором (- 0,8) в, на третьем (-0,4) в, а на выходах эмиттерных повторителей 3i, 3- и 5з соответственно-0,7,-,5 и - 1,1 8. Это состояние схемы сохраняется на всю длительность импульса.

Во время второго полупериода входной частоты напряжение на входе схемы вновь становится равным -1,3 в, а так как напряжение транзистора 2, было -1,1 в, то ключ /i открывается, а ключ 2| запирается. Теперь на первом выходе счетчика устанавливается напряжение (-0,4) в, на втором (-0,8) в, на третьем - нулевое. Напряжения с эмиттерных повторителей, смещающие выходные напряжения схемы в отрицательную область на 0,7 в, удерживают ячейки схемы в этом состоянии до поступления следующего импульса (фиг. 2). Следовательно, при подсчете одного импульса нулевой уровень напряжения в счетчике перемещается с первого выхода на третий, после второго импульса - на второй. После третьего импульса схема возвращается в исходное состояние, когда с первого выхода снимается нулевое напряжение.

В предлагаемой схеме мощность, рассеиваемая элементом перекрестной связи, примерно вдвое меньще мощности, рассеиваемой транзисторными ключами. Это позволяет за счет перераспределения токов, ранее протекавщих через элементы перекрестных связей, увеличить токи, переключаемые транзисторными ключами.

Поэтому предлагаемая схема обладает более высоки.м быстродействием, чем известные схемы. Оценим, во сколько раз возросла предельная частота счетчика.

Известно, что время задержки распространения сигнала на уровне 50% логической единицы для схем на переключателях тока

/. i + (o,7cJ-+0,5C.J--).,

где ty - время задержки, зависящее только от параметров транзисторов;

С, - полная емкость, подключенная к каждому выходу схемы счетчика;

Ci - входная емкость эмиттерного повторителя;

Е - напряжение источника питания;

Vi - размах напряжения логической единицы на выходе схемы;

Pg-мощность, рассеиваемая токовыми ключами;

Ре-мощность, рассеиваемая эмиттерньш повторителем.

Оптимальным между мощностями Pg и Ре является соотнощение . Поэтому выражение для ta можно переписать:

,-/,;+-(0,7 с, i-Q) Еу,.

На основании временных диаграмм на фиг. 2 можно прийти к выводу, что минимальный период входной частоты импульсов который можно подавать на счетчик, равен 2L . Следовательно, максимальную частоту

.мин

входных импульсов предлагаемого счетчика можно определить по формуле

0,5Я

1

прел

-у. - ,

- мипГ,/-,,

ьпрсд -;- (0,7 Cj п- CL)EVI

50 или при t,P,,,,, « (0,7С, -;- CL}EV

,„,,,

/ м а к с

(0,7С, -Ci)fK,

где Рg . - предельная мощность, рассеиваемая токовыми ключами.

Из полученного выражения следует, что рабочая частота счетчика вдвое выще частот счетчика, выполненного по схеме, взятой из прототипа.

В предлагаемой схеме требуется лишь один источник питания, причем напряжение в дватри раза меньще напряжения обоих источников, требующихся для работы известной схемы. Поэтому при одинаковых переключаемых токах мощность, потребляемая каждой ячейкой, во столько же раз меньше.

Так как токи в элементах перекрестных связей предлагаемой схемы уменьшились и стали равны токам баз эмиттерных повторителей ( /бэп), то в этой схеме увеличивается отношение уровней напряжения логической единицы ({/) и логического нуля (f/o):

1 IK.I + /бэп IK.л и

777 7

Q-бэп бэп

а для случая, когда/кл /эп, t/i

и,

Одним из преимуш,еств схемы счетчика является также возможность выполнения ее не только в гибридном, но и в твердотельном исполнении, причем выходные уровни напряжения схемы хорошо согласуются с уровнями напряжений серийно выпускаемых микросхем на переключателях тока.

Предмет изобретения

Кольцевой счетчик на переключателях тока, выполненных на транзисторах с эмиттерными связями, состоящий из нечетного числа ячеек, у которых базы транзисторов первых ключей всех ячеек объединены и образуют счетный вход кольцевого счетчика,

а коллектор транзистора первого ключа г-той ячейки соединен с коллектором транзистора второго ключа i-1-вой ячейки и резистором нагрузки, отличающийся тем, что, с целью повышения быстродействия, уменьшения потребляемой мощности и уровня напряжения логического ну.тя, каждая ячейка кольцевого счетчика содержит эмиттерный повторитель, при этом коллектор транзистора первого ключа j-той ячейки соединен с базой транзистора

второго ключа данной ячейки через транзистор эмиттерного повторителя, база которого связана с коллектором транзистора первого ключа, а эмиттер - с базой транзистора второго ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА БАЗОВОГО МАТРИЧНОГО КРИСТАЛЛА | 1992 |

|

RU2035088C1 |

| Стабилизирующий конвертор напряжения постоянного тока | 1990 |

|

SU1737662A1 |

| Преобразователь логических уровней | 1987 |

|

SU1466004A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| Однотактный транзисторный конвертор | 1986 |

|

SU1394360A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU364029A1 |

| Усилитель мощности | 1987 |

|

SU1532994A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Кольцевой делитель частоты с четным коэффициентом деления | 1972 |

|

SU437228A1 |

{Js

бш 3

0 -е

Риг /

-0,9 -1,3

ш, i

-а« -0.

:J

Даты

1974-05-05—Публикация

1972-02-16—Подача