Изобретение относится к дискретным счетно-решающим устройствам, в частности к пересчетным двоичным устройствам накопительного типа, и может применяться в устройствах программно-временного управления, в устройствах отсчета и регистрации числа импульсов.

Известны накопительные счетчики импульсов с коэффициентом деления К. , содержащие одноразрядный двоичный полусумматор, распределитель импульсов, числовую линейку запоминания для храпения накопленного двоичного кода, ключ перезаписи кода в числовую линейку, при этом счетный вход соединен с одним из входов одноразрядного полусумматора.

Известны также пересчетные схемы на кольцевых регистрах с коэффициентом деления , а также триггерные счетчики с коэффициентом деления /(2.

Недостатком таких пересчетных схем является то, что при необходимости получения коэффициента деления или увеличения коэффициента деления в п раз, требуется последовательное соединение двух счетчиков, одного с коэффициентом деления Ki n к второго-с коэффициентом деления , что связано с усложнением схемы.

Достигается это тем, что в накопительном счетчике импульсов с коэффициентом деления Х 2, содержащем одноразрядный двоичный полусумматор, п-разрядный распределитель, и-разрядную числовую линейку и ключ перезаписи кода в числовую линейку, вход счетчика соединен с тактовой цепью распределителя импульсов и п-ый разряд распределителя соединен с цепью переноса двоичного одноразрядного полусумматора. Такое построение позволяет использовать пересчетные свойства распределителя импульсов и, за счет совмещения в нем функций распределения импульсов и деления, увеличить общий коэффициент

деления счетчика без увеличения числа элементов в п раз, где п - число разрядов распределителя импульсов.

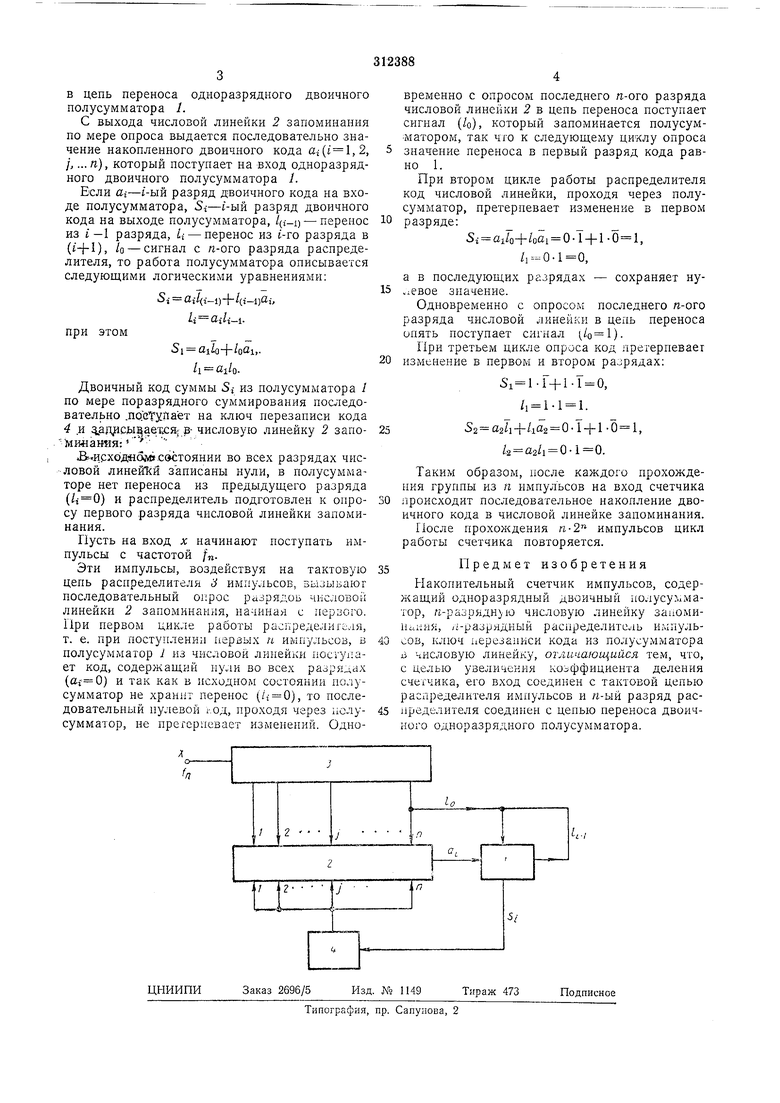

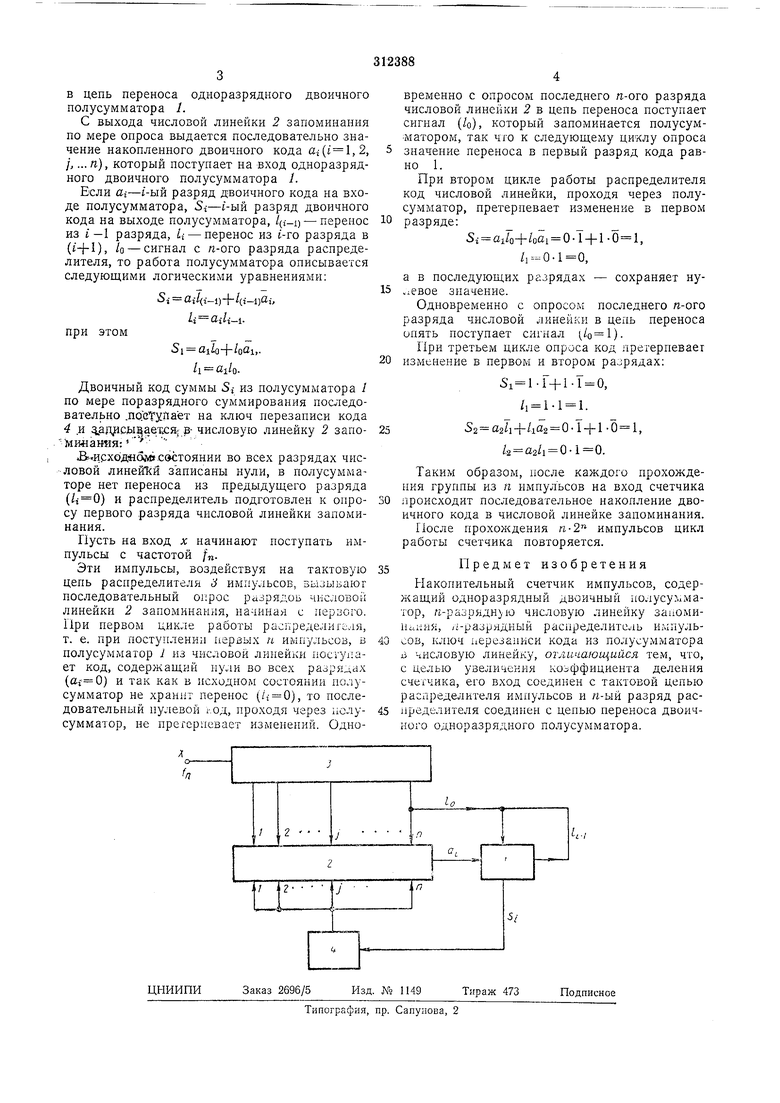

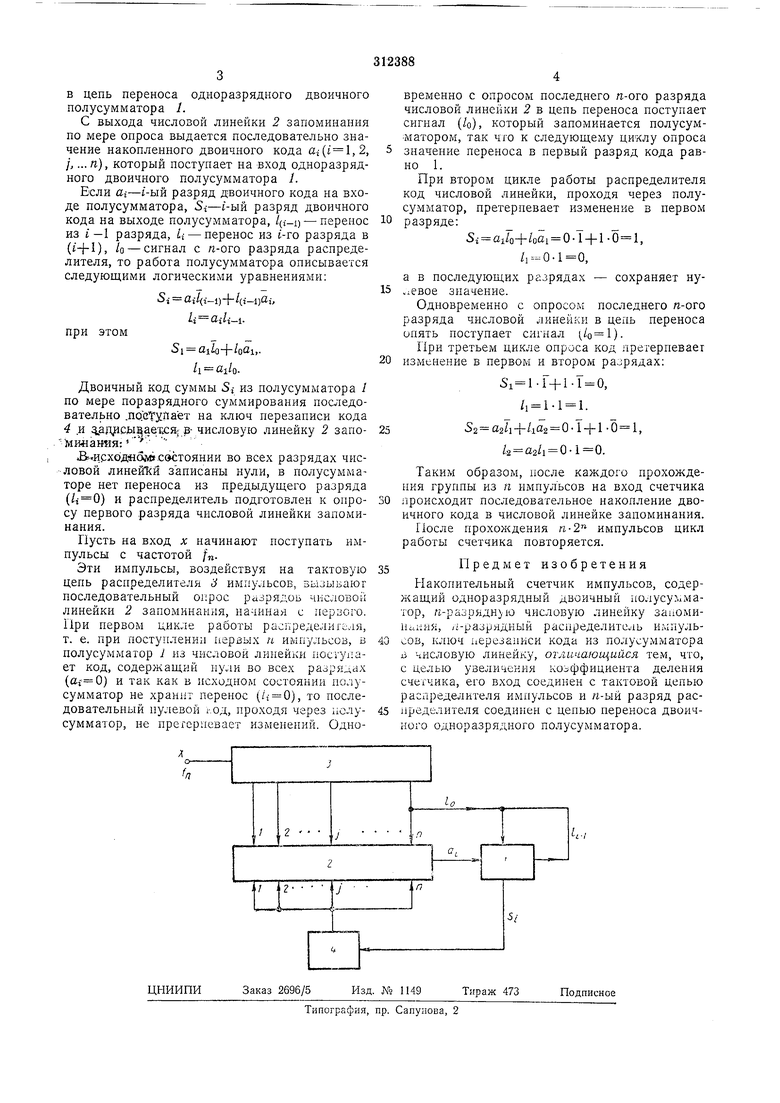

На чертеже изображена функциональная схема предлагаемого счетчика.

Накопительный счетчик импульсов содержит одноразрядный двоичный полусумматор /, га-разрядную числовую линейку 2 запоминания, «-разрядный распределитель 3 импульсов, ключ перезаписи кода 4 в числовую линейку.

Вход X счетчика соединен с тактовой цепью распределителя 3 который осуществляет последовательный опрос разрядов числовой линейки 2. Одновременно с опросом последнего га-ого разряда числовой линейки запоминания

в цепь переноса одноразрядного двоичного полусумматора 1.

С выхода числовой линейки 2 запоминания по мере опроса выдается последовательно значение накопленного двоичного кода aj(i l,2, /,...«), который поступает на вход одноразрядного двоичного полусумматора /.

Если иг-i-ый разряд двоичного кода на входе полусумматора, 5 -t-ый разряд двоичного кода на выходе полусумматора, i(i-i) - перепое из i -1 разряда, k - перенос из i-ro разряда в (i+I), /о - сигнал с п-ого разряда распределителя, то работа полусумматора описывается следующими логическими уравнениями;

Si ail(i-i)(i-i)ai,

/i . при этом

Si ailo-f/oai,. /1 ai/oДвоичный код суммы Si из полусумматора / по мере поразрядного суммирования последовательно .по.сТупает на ключ перезаписи кода 4 и алдисы аает ся; в- числовую линейку 2 запоми«ания:

.исходно состоянии во всех разрядах числовой линейки записаны нули, в полусумматоре нет переноса из предыдущего разряда () и распределитель подготовлен к опросу первого разряда числовой линейки запоминания.

Пусть на вход х начинают поступать импульсы с частотой /„.

Эти импульсы, воздействуя на тактовую цепь распределителя импульсов, зызываюг последовательный опрос разрядов числовой линейки 2 запоминания, начиная с периого. При первом цикле работы расгфеделигсля, т. е. при поступлении первых п импульсов, в полусумматор 1 из числовой линейки nociyjiaет код, содержащий пули во всех разрядах () и так как в исходном состоянии полусумматор не xpahiir перенос (/t 0), то последовательный пулевой i-.од, проходя через полусумматор, не претерпевает изменений. ОдноВременно с опросом последнего п-ого разряда числовой линейки 2 в цепь переноса поступает сигнал (/о), который запоминается полусумчматором, так что к следующему циклу опроса значепие переноса в первый разряд кода равно 1.

При втором цикле работы распределителя код числовой линейки, проходя через полусумматор, претерпевает изменение в первом разряде:

5г аЛ+/оа1 0-1+1 , ,

а в последующих разрядах - сохраняет ну.;евое значение.

Одновременно с опросом последнего п-ого разряда числовой линейки в цепь переноса опять поступает сигнал ).

При третьем цикле опроса код претерпеваег изменение в первом и втором разрядах:

51 1-Г-|-1-Г 0,

/1 1-1 1.

52 a2li+/aa2 0-T+l-0 l,

/,2 а2/1 .

Таким образом, после каждого прохождения группы из п импульсов на вход счетчика происходит последовательное накопление двоичного кода в числовой линейке запоминания.

После прохождения п.-2 импульсов цикл работы счетчика повторяется.

Предмет изобретения

Пакопительный счетчик импульсов, содержащий одноразрядный двоичный полусу:аматор, «-разрядною числовую линейку зааомиИс пия, /j-разрядный распределите 1ь импульсов, ключ аерезаииси кода из полусу.мматора j3 числовую линейку, отличающийся тем, что, с целью увеличения ко:5ффициента деления счетчика, его вход соединен с тактовой цепью распределителя импульсов и п-ый разряд рас11ределителя соединен с цепью переноса двоичного одноразрядного полусумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов | 1980 |

|

SU875640A1 |

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Управляемый делитель частоты следования импульсов | 1984 |

|

SU1221743A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Счетное устройство с контролем | 1985 |

|

SU1298898A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

Даты

1971-01-01—Публикация