Изобретение относится к автоматике и вычислительной технике и может быть использовано для потактового контроля двоичных счетчиков.

Цель изобретения - повышение надежности устройства.

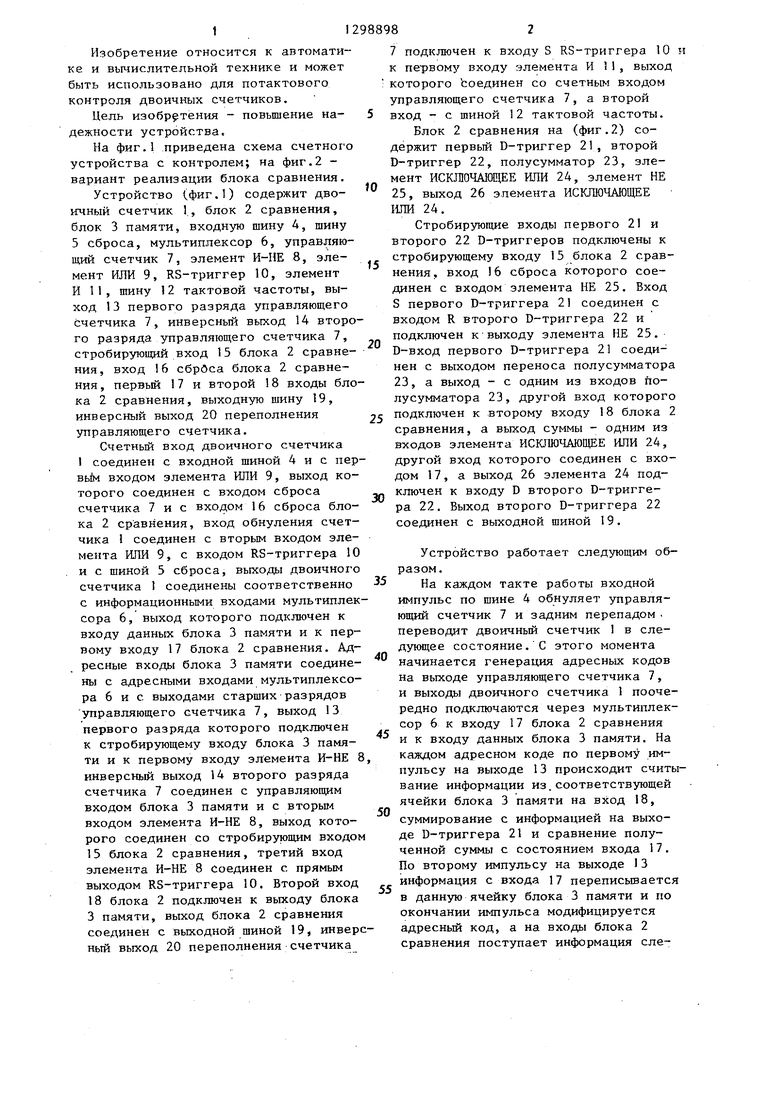

На фиг.1 приведена схема счетного устройства с контролем; на фиг.2 - вариант реализации блока сравнения. Устройство (фиг.1) содержит двоичный счетчик 1, блок 2 сравнения, блок 3 памяти, входную шину 4, шину 5 сброса, мультиплексор 6, управляющий счетчик 7, элемент И-НЕ 8, элемент ИЛИ 9, RS-триггер 10, элемент И 11, шину 12 тактовой частоты, выход 13 первого разряда управляющего счетчика 7, инверсньш выход 14 второго разряда управляющего счетчика 7, стробирующий вход 15 блока 2 сравнения, вход 16 сбрбса блока 2 сравнения, первый 17 и второй 18 входы блока 2 сравнения, выходную шину 19, инверсный выход 20 переполнения управляющего счетчика.

Счетный вход двоичного счетчика I соединен с входной шиной 4 и с пер входом элемента ИЛИ 9, выход которого соединен с входом сброса счетчика 7 и с входом 16 сброса блока 2 сравнения, вход обнуления счетчика 1 соединен с вторым входом элемента ИЛИ 9, с входом RS-триггера 10 и с шиной 5 сброса, выходы двоичного счетчика 1 соединены соответственно с информационными входами мультиплексора 6, выход которого подключен к входу данных блока 3 памяти и к первому входу 17 блока 2 сравнения. Адресные входы блока 3 памяти соединены с адресными входами мультиплексора 6 и с. выходами старших разрядов управляющего счетчика 7, выход 13 первого разряда которого подключен к стробирующему входу блока 3 памяти и к первому входу элемента И-НЕ инверсный выход 14 второго разряда счетчика 7 соединен с управляющим входом блока 3 памяти и с вторьв- входом элемента И-НЕ 8, выход которого соединен со стробирующим входо 15 блока 2 сравнения, третий вход элемента И-НЕ 8 Соединен с прямым выходом RS-триггера 10. Второй вход 18 блока 2 подключен к выходу блока 3 памяти, выход блока 2 сравнения соединен с выходной шиной 19, инверный выход 20 переполнения счетчика

5

0

5

0

5

0

45

50

55

7 подключен к входу S RS-триггера 10 и к первому входу элемента И 51, выход которого Ьоединен со счетным входом управляющего счетчика 7, а второй вход - с шиной 12 тактовой частоты.

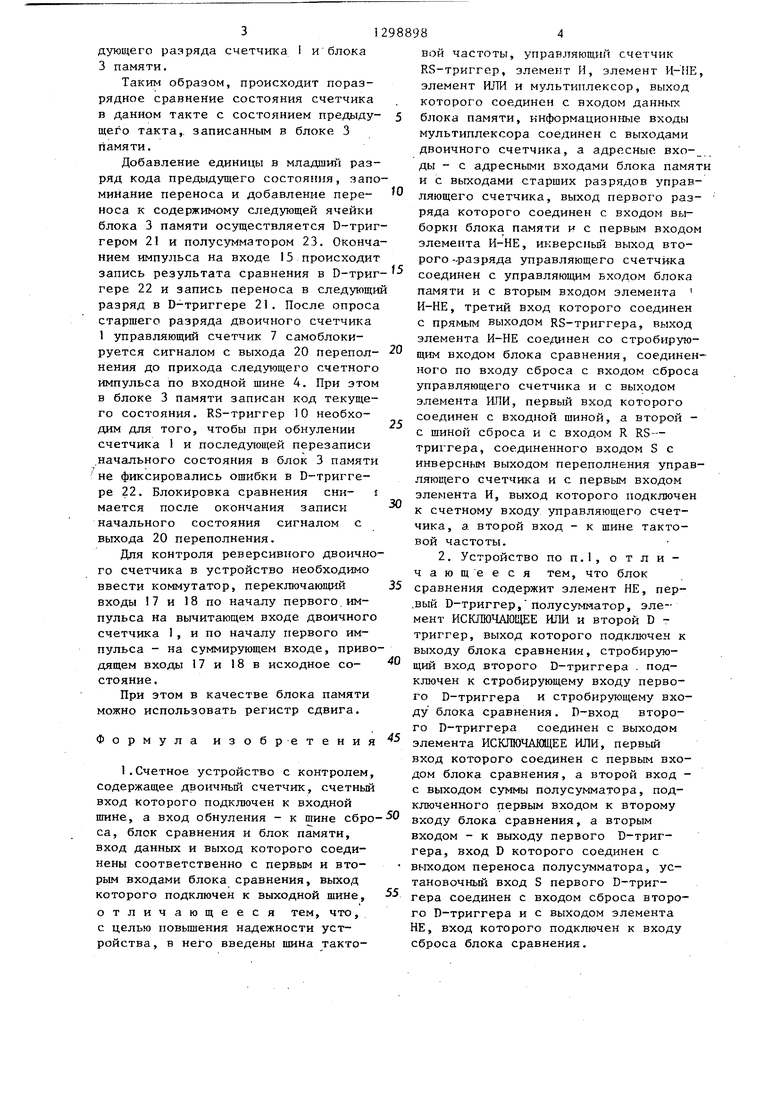

Блок 2 сравнения на (фиг.2) содержит первый D-триггер 21, второй D-триггер 22, полусумматор 23, элемент ИСКЛ10ЧАКЩЕЕ ИЛИ 24, элемент НЕ 25, выход 26 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24.

Стробирующие входы первого 21 и второго 22 D-триггеров подключены к стробирующему входу 15 блока 2 сравнения, вход 16 сброса которого соединен с входом элемента НЕ 25. Вход S первого D-триггера 21 соединен с входом R второго D-триггера 22 и подключен к выходу элемента НЕ 25. D-вход первого D-триггера 21 соединен с выходом переноса полусумматора 23, а выход - с одним из входов полусумматора 23, другой вход которого подключен к второму входу 18 блока 2 сравнения, а выход суммы - одним из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, другой вход которого соединен с входом 17, а выход 26 элемента 24 подключен к входу D второго D-триггера 22. Выход второго D-триггера 22 соединен с выходной шиной I9.

Устройство работает следующим образом.

На каждом такте работы входной импульс по шине 4 обнуляет управляющий счетчик 7 и задним перепадом . переводит двоичный счетчик 1 в следующее состояние. С этого момента начинается генерация адресных кодов на выходе управляющего счетчика 7, и выходы двоичного счетчика 1 поочередно подключаются через мультиплексор 6 к входу 17 блока 2 сравнения и к входу данных блока 3 памяти. На каждом адресном коде по первому импульсу на выходе 13 происходит считывание информации из.соответствующей ячейки блока 3 памяти на вход 18, суммирование с информацией на выходе D-триггера 21 и сравнение полученной суммы с состоянием входа 17. По второму импульсу на выходе 13 информация с входа 17 переписьшается в данную ячейку блока 3 памяти и по окончании импульса модифицируется адресный код, а на входы блока 2 сравнения поступает информация еледующего разряда счетчика I и блока 3 памяти.

Таким образом, происходит поразрядное сравнение состояния счетчика в данном такте с состоянием предыду- щего такта,, записанным в блоке 3 памяти.

Добавление единицы в младший разряд кода предыдущего состояния, запоминание переноса и добавление пере- носа к содержимому следующей ячейки блока 3 памяти осуществляется D-триг гером 21 и полусумматором 23. Окончанием импульса на входе I5 происходит запись результата сравнения в D-триг гере 22 и запись переноса в следующи разряд в D-триггере 21. После опроса старшего разряда двоичного счетчика 1 управляющий счетчик 7 самоблокируется сигналом с выхода 20 перепол- нения до прихода следующего счетного импульса по входной щине 4. При этом в блоке 3 памяти записан код текущего состояния. RS-триггер 10 необходим для того, чтобы при обнулении счетчика 1 и последующей перезаписи .начального состояния в блок 3 памяти не фиксировались ошибки в D-триггере 22. Блокировка сравнения сни- i мается после окончания записи начального состояния сигналом с выхода 20 переполнения.

Для контроля реверсивного двоичного счетчика в устройство необходимо ввести коммутатор, переключающий входы 17 и 18 по началу первого.импульса на вычитающем входе двоичного счетчика 1, и по началу первого импульса - на суммирующем входе, приводящем входы 17 и 18 в исходное со- стояние.

При этом в качестве блока памяти можно использовать регистр сдвига.

Формула изобретения

I.Счетное устройство с контролем, содержащее двоичньш счетчик, счетный вход которого подключен к входной шине, а вход обнуления - к шине сброса, блок сравнения и блок памяти, вход данных и выход которого соединены соответственно с первым и вторым входами блока сравнения, выход которого подключен к выходной шине, отличающееся тем, что, с целью повышения надежности устройства , в него введены шина такто

5

О

5

-5

0

вой частоты, управляющий счетчик RS-триггер, элемент И, элемент Ц-НЕ, элемент ИЛИ и мультиплексор, выход которого соединен с входом данных блока памяти, информационные входы мультиплексора соединен с выходами двоичного счетчика, а адресные вхо- ды - с адресными входами блока памяти и с выходами старших разрядов управляющего счетчика, выход первого разряда которого соединен с входом выборки блока памяти и с первым входом элемента И-НЕ, инверсньш выход второго -разряда управляющего счетчика соединен с управляющим входом блока памяти и с вторым входом элемента И-НЕ, третий вход которого соединен с прямым выходом RS-триггера, выход элемента И-НЕ соединен со стробирую- щим входом блока сравнения, соединенного по входу сброса с входом сброса управляющего счетчика и с выходом элемента ИПИ, первый вход которого соединен с входной шиной, а второй - с шиной сброса и с входом R RS- триггера, соединенного входом S с инверсным выходом переполнения управляющего счетчика и с первым входом элемента И, выход которого подключен к счетному входу управляющего счетчика, а второй вход - к шине тактовой частоты.

2. Устройство по п.1, о т л и - чающееся тем, что блок сравнения содержит элемент НЕ, пер- .вый D-триггер, полусумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и второй D - триггер, выход которого подключен к выходу блока сравнения, стробирую- щий вход второго D-триггера . подключен к стробирующему входу первого D-триггера и стробирующему входу блока сравнения. D-вход второго D-триггера соединен с выходом элемента ИСКПЮЧАЩЕЕ ИЛИ, первый вход которого соединен с первым входом блока сравнения, а второй вход - с выходом суммы полусумматора, подключенного первым входом к второму входу блока сравнения, а вторым входом - к выходу первого D-триггера, вход D которого соединен с выходом переноса полусумматора, установочный вход S первого D-триггера соединен с входом сброса второго D-триггера и с выходом элемента НЕ, вход которого подключен к входу сброса блока сравнения.

18

15

Y

г

17

гцId

гг

19

ь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для циклового программного управления | 1986 |

|

SU1381432A1 |

| Устройство для ввода информации в ЭВМ | 1986 |

|

SU1381525A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1992 |

|

RU2012014C1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для входного контроля изделий | 1989 |

|

SU1619313A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для потактового контроля двоичных счетчиков. Цель изобретения - повышение надежности устройства. Устройство содержит двоичный счетчик 1, блок 2 сравнения, блок 3 памяти. Для достижения поставленной цели в устройство введены мультиплексор 6, управляющий счетчик 7, элемент И-НЕ 8, элемент ИЛИ 9, RS-триггер 10, элемент И П..1 з.п. ф-лы. 2 ил. го со 00 СХ) со 00

W

Редактор А.Козориз

Составитель Ранов Техред М.Ходанич

Заказ 898/59 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. Д/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, А

Фиг. 2

Корректор Л.Патай

Авторы

Даты

1987-03-23—Публикация

1985-11-18—Подача