Изобретение относится к вычислительной технике, а IHMCIHHO к запоминающим устройствам (ЗУ) Электроины.х вычисл1итель1ных маШИН.

Известны ЗУ, в которы,х выполнлются логические и а1рифмехичес1 1ие операции.

В известных ЗУ для .реализации суммирования м ногор-азрядиых ч.исел используется сравпительио мпого оборудования и время сумм1И|рова1Н,ия гораздо больше, чем в обычных а1рифметических устройствах (АУ).

Цель изобретения - упрощение устройства и увел.ичание его быстрадействия.

Это достигается применением алгебраического сложения электродвижуЩИх сил (э.д.С.) сигналов, |на.В01димых -в проводах счнтыва ния при перемагничивании фе-рритовых сердечн.иков (для чего вводится общая обмотка считывания для нескольких числовьгх лииеек, Соединенная с формиравате тем считыва:ния, который 0|беспечивает одио1ВремвН1Ное считы1ва1ние информации с этих числовых ли:пеек), и сигналов, усилвниых усилителями считывания и отстробироваииых стробирующими каскад.ами (для чего вводятся формирователи обратной связи с трансформаторпым выходом, обеспечивающие подачу отстробирова.ниых аигналов щ :провод считывания). Провода считывания ферритового накопителя при этом прощиты ие только через

феррито.вые сердечники Соответ ствующих разрядов этих числовых линеек, но и через ферритовые сердеч:Н, предыдущие- разрядов и сердеч;Н1ики траНСформаторов о-братнон

связи.

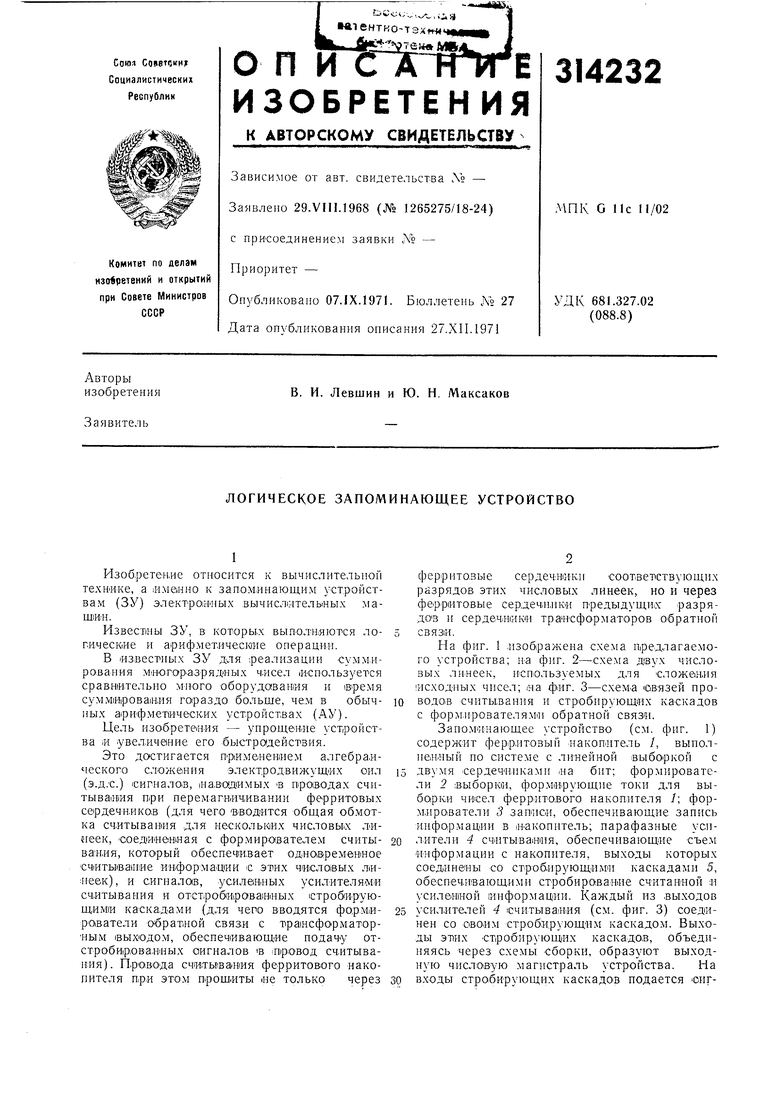

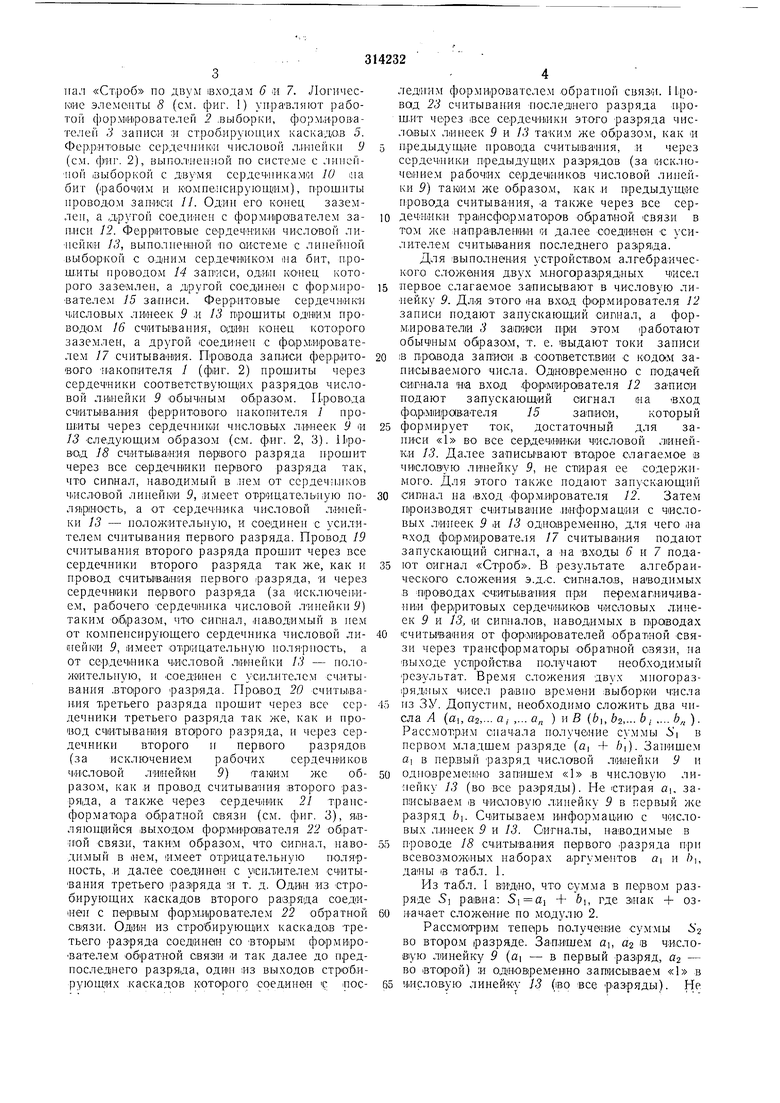

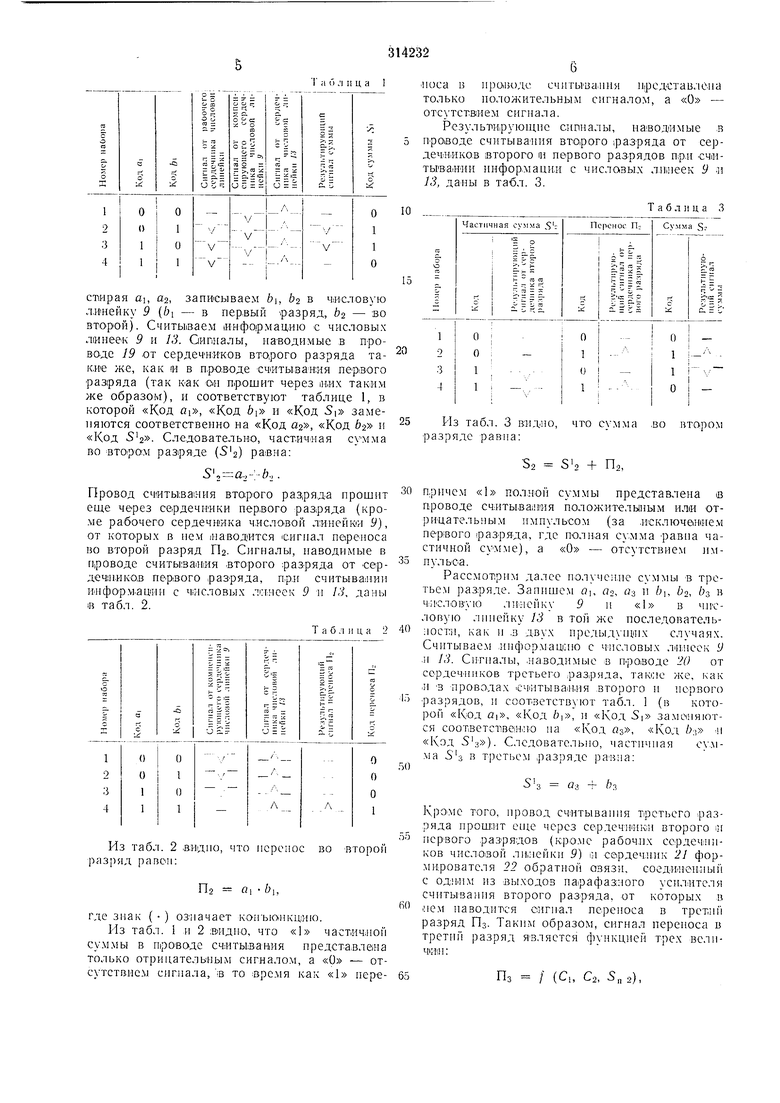

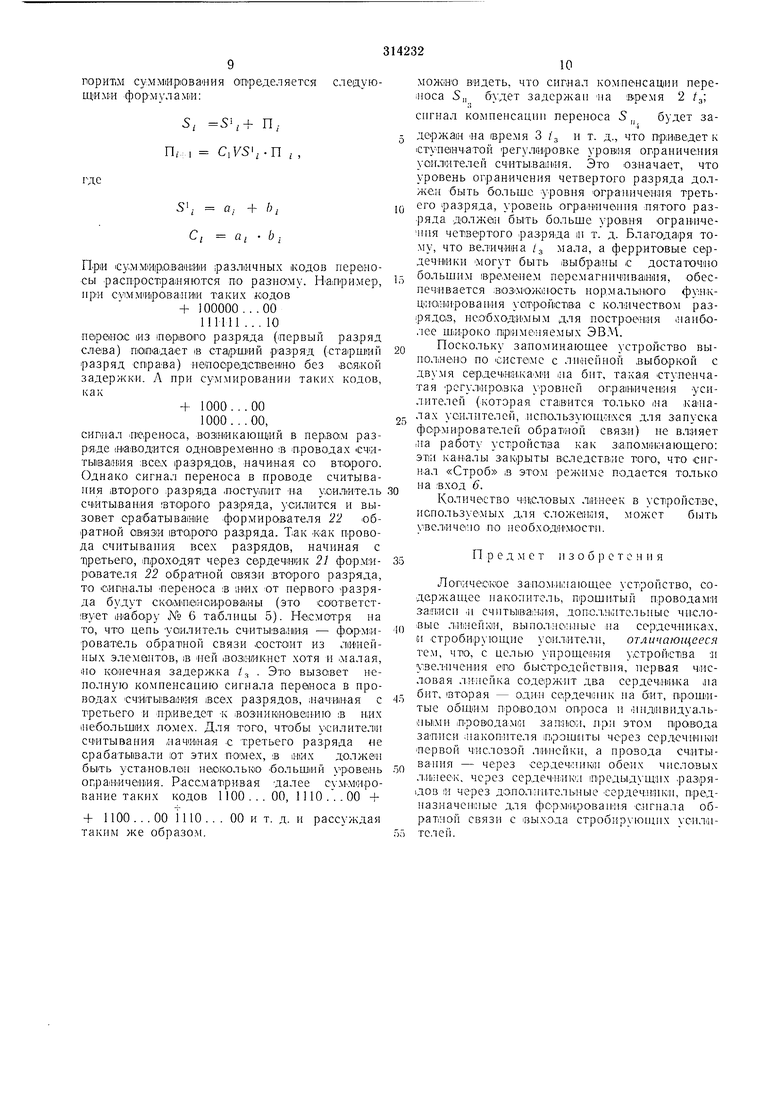

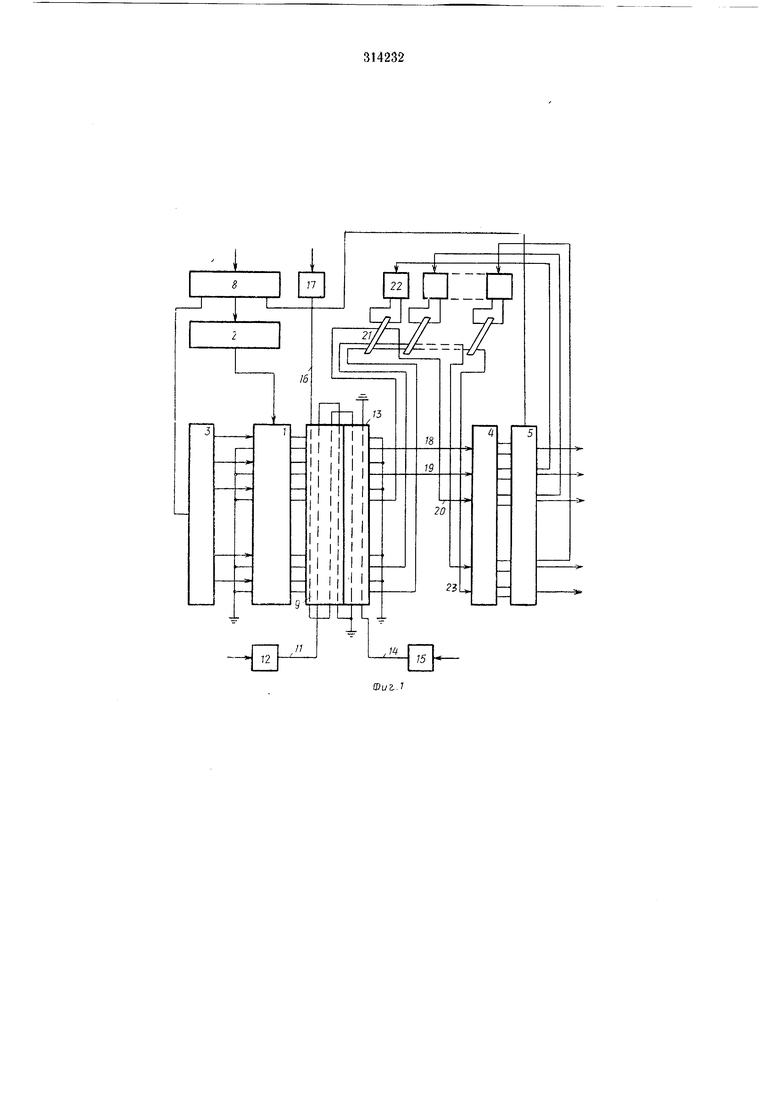

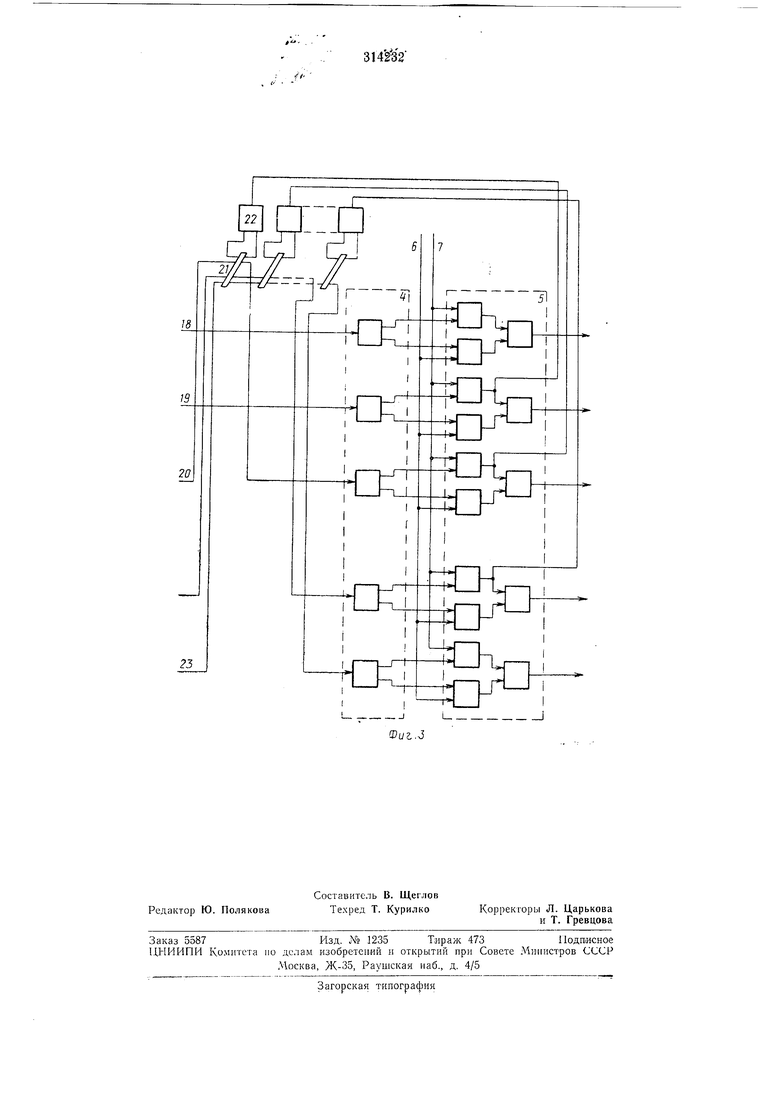

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2-схе.ма явух числовых линеек, исп ользуемых для сложения исходных чисел; на фиг. 3-схемка евязей проводов считывания и стробирующих каскадов с формирователями обратной связи.

Запоминающее устройство (см. фиг. 1) содержит ферр.итовый накоп1птель /, выполпенный по системе с линейной выборкой с

дву.мя сердечникамн на бит; формирователи 2 выборюи, формирующие токи для выборки чисел ферритового накопителя 1; формирователи 3 запаюи, обеспечивающие запись информации в 1Наколптель; парафазные усилители 4 счнтыван1ия, обеснечивающ ие съем информации с накопителя, выходы которых соединены со стробирующими каскадами 5, обеспеч.ивающими стробираван1не считаниой .и усиленной информацаш. Каждый из выходов

усилителей 4 считывания (см. фиг. 3) соединен со своим стробир}ющим каскадом. Вы.ходы ЭТ1ИХ Стробирующих каскадов, объединяясь через схемы сборки, образуют выходн чо числовую магистраль устройства. На входы стробирующих каскадов подается сигнал «Ст.рОб по двум 1в.ходам 6 ai 7. Логические элементы 8 (см. фиг. 1) управляют работой формирователей 2 .выборки, форм.ирователеп 3 записи :и стр.об,иру1опи1х каскадов 5. Фер,р:итавые сердечпиюи числовой лли1ейки 9 (см. фиг. 2), выполиен-юй по системе с линейной выборкой с двумя сердеЧИикам1И 10 i;ia бит (р.абочи.м и компе-нси.рующи.м), прошиты ироводом записи 11. Один его коиец заземлеи, а д,ругой соединен с форм,П1ро вателем записи 12. Ферритовые сердеч Ники числовой линейки 13, выполие1-шюй ПО системе с лппей-иой выбо1р«ой с одиим сердеч1Н1Иком 1иа бит, п.рош,иты проводом 14 , од;И|И коиец которого заземлеп, а другой соединен с формирователем 15 за1писи. Ферр.итовые сердечники .вых лийеек 9 -и 13 паротиты одн1им проводом 16 считывания, остви коиец которого заземлен, а другой соединен с формирователем 17 считывания. Про;вода занлси ферритового н-акопителя / (фиг. 2) прогниты через сердечники соответствующих разрядов числовой л.инейки 9 обыч1ным образом. Провода считывания феррнтового накопителя 1 прошиты через сердечники числовы,х линеек 9 и 13 следуюш,им образом (см. фиг. 2, 3). Провод 18 считывания первого разряда прошит через все сердечники первого разряда так, что силнал, на1водимый в нем от сердечников ч.исловой линейки 9, и.меет отрицательную ноля|р1ность, а от сердеч-пика числовой линейки 13 - положительную, и соединен с усилителем считывания первого разряда. Провод 19 считывания второго разряда прошит через все сердечники второго разряда так же, как и провод считывания первого разряда, и через сердечники первого разряда (за исключением, рабочего сердеч1н,нка числовой линейки 5) таким образом, что сипиал, .наводимый в нем от компенсирующего сердечника числовой литейки 5, имеет отрицательную нолярность, а от сердеч1ника числовой линейки 13 - положительную, и соединен с усил,ителем считывания .второго разряда. Провод 20 считывания третьего разряда прошит через все сердечники третьего разряда так же, как и провод считывания второго разряда, и через сердечники второго и первого разрядов (за исключением рабочих сердечников ЧНСловой ли1нейк1И 9) 1так1им же образом, как и провод считывания второго разряда, а также через сердечник 21 трансформатора обратной связи (см. фиг, 3), являющийся выходом фор .миравателя 22 обратной связ.и, таким образом, что сигнал, иаводимый в нем, имеет отрицательную полярность, ,и далее соединен с усилителем считывания третьего разряда :и т. д. Один из стробирующих каскадов второго разряда соедиiHSH с первым формирователем 22 обратной св1язи. Од1И1Н из стробирующих каскадов третьего разряда соединен со вторым формирователем обратной связи и так далее до предпоследнего разряда, один из выходов стробирующих каскадов которого соединен С носед н:им формирователем обратной связи. Провод 23 считывания последнего разряда и.рощ,ит через iBce сердечники этого разряда числовых линеек 5 и 13 таким же образом, как iH нредыдущие нровода считывания, и через сердеч ники предыдущих раз рядов (за исключеиие.м рабочих сердеч1ников числовой линейки 9) таюим же образом, как и предыдущие провода считывания, & также через все сердечники тра|Нсформатаров обратной связи в том же :направлении и далее соединен с усилителе.м считывания носледнего раз1ряда. Для выполнения устройством алгебраического сложения двух многоразрядных чисел первое слагаемое записывают в числовую линейку 9. Дл,я этого «а вход формирователя 12 записи подают запускающий сипнал, а форМ:ирователи 3 заииси при этом 1работают обычны1М образом, т. е. выдают токи записи iB провода запйои в соответствии с кодом записываемого числа. Одновременно с подачей сигиала на вход формирователя 12 запиои подают запускающий сигнал иа вход фор|Миров:ателя 15 записи, который форчмирует ток, достаточный для заинси «1 во все сердечники числовой линейки 13. Далее за-писывают второе слагаемое е числовую линейку 9, не стирая ее содержимого. Для этого также подают запускающ:ий сипнал на вход формирователя 12. Затем производят считыва1ние информации с числовых лоФнеек 9 и 13 одновременно, для чего на «ход формирователя 17 считываашя подают запускающий сипнал, а на входы 6 к 7 подают сигнал «Строб. В результате алгебраического сложения э.д.с. сигналов, наводимых в нроводах считывания нри пере1.магничивании ферритовых сердечников числовых линеек 9 и 13, 1И сипналов, наводимых в проводах считыВанНЯ от фор-мирователей обратной связи через трансформаторы обратной связи, на выходе устройства получают необходимый результат. Время сложения двух миогораз1рядных чисел равно времени выборки числа из ЗУ. Допустим, пеобходимо сложить два числа Л («1, а2,... а,-,... а„ ) и S (6|, ба,... 6,. ,... 6„ ). Рассмотрим получение суммы il в первом младшем разряде («i -f b. Запишем а в первый разряд числовой линейки 9 и одновременно «1 в числовую линейку 13 (во все разряды). Не стирая а, записываем в числовую линейку 5 в первый же р-азряд Ь. Считываем информацию с числовых липеек 9 н 13. Сигналы, на;водимые в проводе 18 считыва.ния первого разряда всевозможНых наборах аргументов а и , даны в табл. 1. Из табл. I видно, что сумма в нервом разряде 5) равна: 5i ai + 61, где знак -f означ ает сложение но модулю 2. Рассмотрим тенарь получение суммы 62 во втором разряде. За-пишем а, а. в числовую линейку 9 (а - в первый разряд, «2 - во второй) и од1новремен1но записываем «1 в и.нсловую линейку 13 (IBO все р азряды). Не. г а О .4 II ц а 1 спирая Сь 02, записываем bi, 62 в числовую ллнейку 9 (bi - в первый разряд, bz - во второй). Считы1ваем инфОрмацию с числовых линееК 9 и 13. Оилналы, изводимые в прово.де 19 от сердечников второго разряда такие же, как И в ироводе сч1иты.ван;ия nepiBoro разряда (так как прошит через иих таким же образом), и соответствуют таблице 1, в которой «Код Й1, «Код i и «Код 5, заменяются соответствеино на «Код аз, «Код Ь-2 и «Код S2. Следовательно, частичНая сумма во втором разряде (52) равна: S.,-a.,:-b.,. Провод считывания второго разряда прошит еще через сердечн ики первого разряда (кроме рабочего сердечника числовой л:инейюи У), от которых в нем /наводится сигнал переноса во второй разряд П2. Сигналы, наводимые в проводе считывалшя второго разряда от сердеч1ников первого разряда, при считыва;нии Ннформ.ашш с Ч1исловых лсгмеек 9 н /Л, даны 1В табл. 2. Т а б л II ц а 2 Из табл. 2 в:идпо, что перенос во второй разряд равен: П2 «1 bi, где знак ( ) озиачает конъюнкцию. Из табл. 1 и 2 видно, что «1 часТ|ИЧ;НОЙ суммы в нроводе считывания представлана только отрицательным сигналом, а «О - отсутствием сигнала, в то время как «1 переоса в нраводс считыва.нии ирсдстав,1См1а только положительным сигналом, а «О - отсутствием сигнала. Результнруюиию сипналы, наводимые в проводе считывання второго разряда от сердечНиков второго ш первого разрядов пр.п считывании информапи.и с числовых л.ншеек 9 -и 13, даны в табл. 3. Т а б л II ц а 3 Из табл. 3 видно, что схмма во втором разряде равна: S2 Sa + По, причем «1 полной суммы представлена в нроводе сч;итыва11шя положителыпым или отрицательным пмпульсом (за исключвние.м первого разряда, где полная сумма равна частичной сумме), а «О - отсутствием импульса. Рассмотрим далее получение суммы в третьем разряде. Заиише.м 0|, «2- «з и i, 2, з в Ч:исловую линейку 9 п «1 в числовую линейку 13 в той же последовательности, как и .в двух предыдуи11их случая.ч. Счнтывае.м информацию с числовых лииеек 9 и 13. Сигналы, -наводимые в проводе 20 от сердеЧНиков третьего разряда, такие же, как .и 3 проводах считываН,ия второго и первого разрядов, и соответствуют табл. 1 (в которой «Код и, «Код 6|, i «Код S| за.мешяются cooTBeTCTBeiHiio на «Код «з, «Код Ь, и «Код 5з). Следовательно, част1гчиая су.мма 5з в третьем разряде равна: S-з из + /Ъ Кроме того, провод считывання третьего разряда прошит еи;е через сердечн ики второго SH первого разрядов (кро-ме рабочих сердеч.ников числовой ли.нейкн 9) ел сердечник 2 формирователя 22 обратной азязи, соеди.нениый с одним из выходов парафазиого усилителя считывания второго разряда, от которых в мем наводится сигнал переноса в третий разряд Пз. Такп.м o6pa30N, сигнал переноса в третий разряд является функц1 ей трех величин:

где СI - част,ич1ный перенос из первого разряда, причем Ci n2, €2 - часничпый перенос .из второго разряда;

S,,2- сипнал, наводимый s проводе считывания третьего разряда от сердечиика 21 формирователя обратной связи 22.

Оигиалы, наводимые iB проводе считы-вапгая третьего разряда от сардеч инков второго разр.яда, оп ределяются табл. 2, в которой «Код ai, «Код Ь и «Код Пз заменяются соот.ветствен но -на «Код а2, «Код &2 и «Код С2.

Следовательно частичный перенос из второго разряда равен:

Cz Q2 bz

Си.гн1алы, (Н.авод.имые в проводе считывальия третьего раз1р.яда от сердечников первого разряда, определяются также таблицей 2. Следовательно частичный перепое из первого разряда раван:

Ci П2 - «i-fil

Сиппалы, наводимые в проводе считываагия лретьего разряда от сердечника 21 фор.мироВнтеля о6ра:т1ной свйЗ|И 22, являются функцией двух не|р.ембН1ных Ci :И 52, и определяются табл, 4.

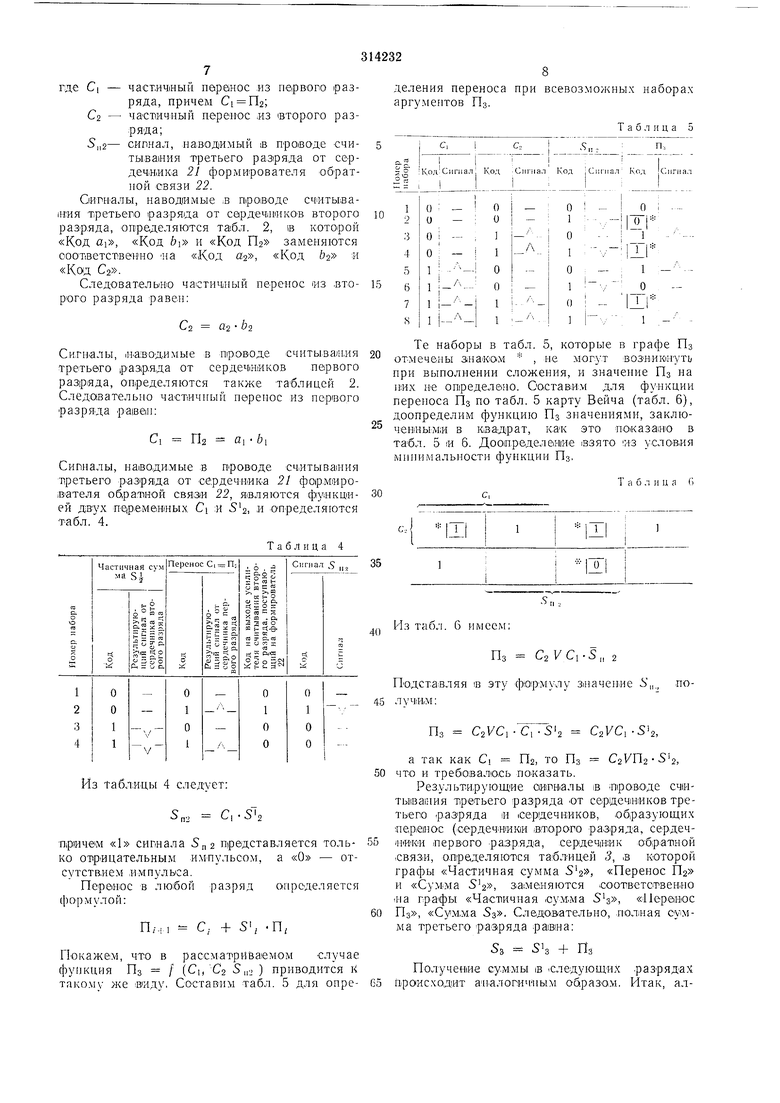

Таблица 4

деления переноса при всевозможных наборах аргуме 1тов Пз.

Таблица 5

Те наборы в табл. 5, которые в графе Пз отмечены знаком , не могут вози икигуть при ВЕзШолнепии сложения, и значение Пз па них ite онределано. Составим для функции перепоса Пз по табл. 5 карту Вейча (табл. 6), доопределим функцию Пз зпачепиями, заключеп1ным;и в К1вадрат, ка-к это пО|Каза1но в табл. 5 и 6. Доопределение взято из условия мн1шмальности функции Пз.

Т а б л и ц а С)

с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| УСТРОЙСТВО ПАМЯТИ и РЕГИСТРАЦИИ | 1968 |

|

SU217463A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU253143A1 |

| Счетчик импульсов | 1980 |

|

SU875640A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНО-п-ИЧНОГО КОДА | 1973 |

|

SU387360A1 |

| МНОГОКАНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU224589A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Запоминающее устройство | 1973 |

|

SU481938A1 |

Из таблицы 4 следует;

С,-Ss

5пз

причем «1 сигнала представляется только отрицательным импульсом, а «О - отсутств.ием импульса.

Перенос в любой разряд

определяется фОрмулой:

П/Н1 - С. + 5, -П;

Из таб.1. 6 имеем;

Пз C.VCi-S

1 1 2

Подставляя IB эту формулу 3|Начеп1ие i,,., получи,м:

Пз C2VCi- 2 СгУС, S2,

а так как Ci П, то Пз С2УП2-52, что и требовалось показать.

Результирующие си гвалы в сч1итывас-шя третьего разряда от сердечников третьего р.азряда и (Сердечников, образующих nepeiHOc (сердечииии второго разряда, сердеч/НИКИ .первого разряда, сердечник обр:атной свяЗ;И, олределяются таблицей 3, в которой графы «Частичная сумма 52, «Перенос П2 и «СуММа 52, 3|а(ме:няются соотвстотвен.но iHa графы «Частичная сум.ма Ss, «Перенос Пз, «Сум.ма 5з. Следовательно, пол:ная сумма третьего р азряда paiBiHa:

5з - + Пз

nopHTiM суммировзния определяется следующими формулами:

S, 5,+ П, П,-,, ;, где

5; и; + I},

С; а, Ь.

При icy.MMiHipiOiBaiHHiH ;разл1ичных кодов пераыосы расп:рост:ра:няются по разному. Н ал ример, при су1мм1И|рО|Ва;ни1И таких кодов + 100000 . . .00

пареиас 1из inepiBOiPO разряда {первый разряд слева) гю1П1ада«т IB ста(рш1ий разряд (старший разряд спра:ва) непосредственно без воякой задержки. А ири су.гмироваиин таких кодов, как

+ 1000...00

Hiepeiroca, возникающий в nepiBOM разр яде 1№аводится одновременно в проводах счиTbiiBaiHiHH :все;Х разрядов, начин.ая со второго. Однако сигнал переноса в проводе считывания iBTOporo разряда .поступит н.а усилитель считывания (второго разряда, усилится и вызовет орабатыва1Н1ие формирователя 22 обр атной связи iBTOporo разряда. Так к-ак провода считывания всех разрядов, начиная с претьего, проходят через сердечник 21 форм;ирователя 22 обратной авяЗИ второго разряда, то сипн1алы Переноса в 1них от первого разряда будут скодипеноироваиы (это саответст1вует набору № 6 таблицы 5). Не;смо1тря на то, что цепь уоилитель считывалвия - форлгирователь обратной связи .состоит из линейных элементов, IB ией 1воз1нгикнет хотя и |Малая, iHO конечная задержка /,, . Это вызо1вет неполную компенсацию сигнала переноса в проводах €чИ ТЫ1ва1Ния iBcex разрядов, ;начиная с третьего и приведет -к |Воэник1НО1вению ;в них небольших .помех. Для того, чтобы усилители считывания /нач1И1на|Я .с третьего разряда ие cpa6aTbiiBavin от этих помел, :в 1них долже н быть установлен насколько больший уровень ограатчеиия. Расс.матривая далее су.м-мирование таких кодов 1100 . . . 00, 1110 .. . 00 +

+ 1100 ... 00 i 110 ... 00 и т. д. и рассуждая таким же образом.

видеть, что сигнал комненсащии переiHOca S,, будет задержан на 2 /з

сигнал компенсации переноса S будет задержа|н на время 3 /з и т. д., что пр;И1ведет к ступенчатой регулировке урокн.я ограничения уоилнтелей считыва1ния. Это означает, что уровень ограничения четвертого разряда должен быть больше уровня огран.ичення третьего разряда, уровень ограничения пятого разряда долже( быть больше уровня огран1иченпя четвертого разряда и т. д. Благодаря тому, что величина /з мала, а ферритовые сердечники МОгут быть Bbi6paiHbi с достаточно большим вре,менем нере.магничивания, обеспеч:ивается :воЗМОЖ|Ность нормального фу:нкцион1НроваНИя уотройстеа с кол;ичеством разрядов, необход;и1мым для построен;ня (Наиболее широко приме.:1яемых ЭВМ.

Поскольку запоминающее устройство вынол1нен10 по системе с линейной выборкой с дву.мя сердечни.каМИ на бит, такая ступенчатая регул1ировка уровней огран1ичен1ия усилителей (которая ставИтся только на ка-налах усилителей, нспользуюЩИ1 ся для запуска формирователей обратной связи) не влияет на работу устройст1за как запоминающего: эти закрыты вследствие того, что сигнал «Строб в этом реЖИме подается только на вход 6.

Количество ч исловых линеек в устройстве, иснользуе мых для сложения, может быт1 увеличено по 11еобход имости.

Предмет изобретения

Лопичеюкое за:П,ом.Н1нающее устройство, содержащее накопитель, прошитый проводами записи н счнты1ва|На1 Я, ДОПОЛЛЬИТСЛЬНЬЕС числовые линейк1и, выполне:1ные на сердечиикал, 51 стробирующие усилители, отличающееся тем, что, с целью упрощения устроЙ1Ства -и увеличения его быстродействня, первая чагсловая линейка содержит два сердеЧ|Н«ы а на бит, вторая - один сердечичик на бит, прошитые обЩ|НМ проводом опроса и имднвидуальны1ми пров1одами зан:Н1о:-1, при этом записи лшкопителя прошиты через ссрдечннкш первой числовой линейки, а провода считывания - через сердеч.ники обеих числовых ллснееК, через сердечлшюл И|редыдущих разря1ДОВ и через дапол::1ительные сердеч;никп, П1редназначс111ные для фсрм нрования сигнала обратной связи с 1выхода стробирующих усилль телей.

5

У/Ю

:±

/31

75

i-Z

-М

7/

nJ: /7

2J

V

ЛЛ

W

UP

н:

UP

UP

Даты

1971-01-01—Публикация