1

Изобретение оiносится к вычислительной технике, в частности, к запоминающим устройствам.

Известно запоминающее устройство (ЗУ), содержащее накопитель на числовых ферритовых линейках с отверстиями записи и опроса, прошитыми соответственно щинами считывания, разрядного TOjva запрета и опро-са, причем каждая шина опроса прошита че- рез отверстия опроса в прямом направлении ;по каждому адресу в отдельности, формирователи адресных и разрядных токов и уси.пители считывания, подключенные к соот- ; ветствуюшим обмоткам, и селектирующие диоды.

Цель изобретения - расширение функциональных возможностей устройства.

Для осуществления устройство содержит формирователи младшего разряда адреса, формирователи первого и второго операндов, нодключенные соответственно к началам шин первого и второго операндов; нажкал шииа ; опроса прошита дополиител1 но через отверстля записи в обратном направлении по каждому адресу в отдельности; начала шин J

опроса через селектирующие диоды, соеди1нены. с соответствующими формирователями младшего разряда адреса, а концы шин опроса подключены к формирователю старшего разряда адреса; шины первого и второго операндов прошиты, сиответственно через отверстия записи и отверстия опроса всех ЧИСЛОВЫ.Х феррйтовых линеек по каждому адресу в отделглности, причем концы этих шин через селектирующие диоды соединены . С соответствующими формирователями млад- шего разряда адреса.

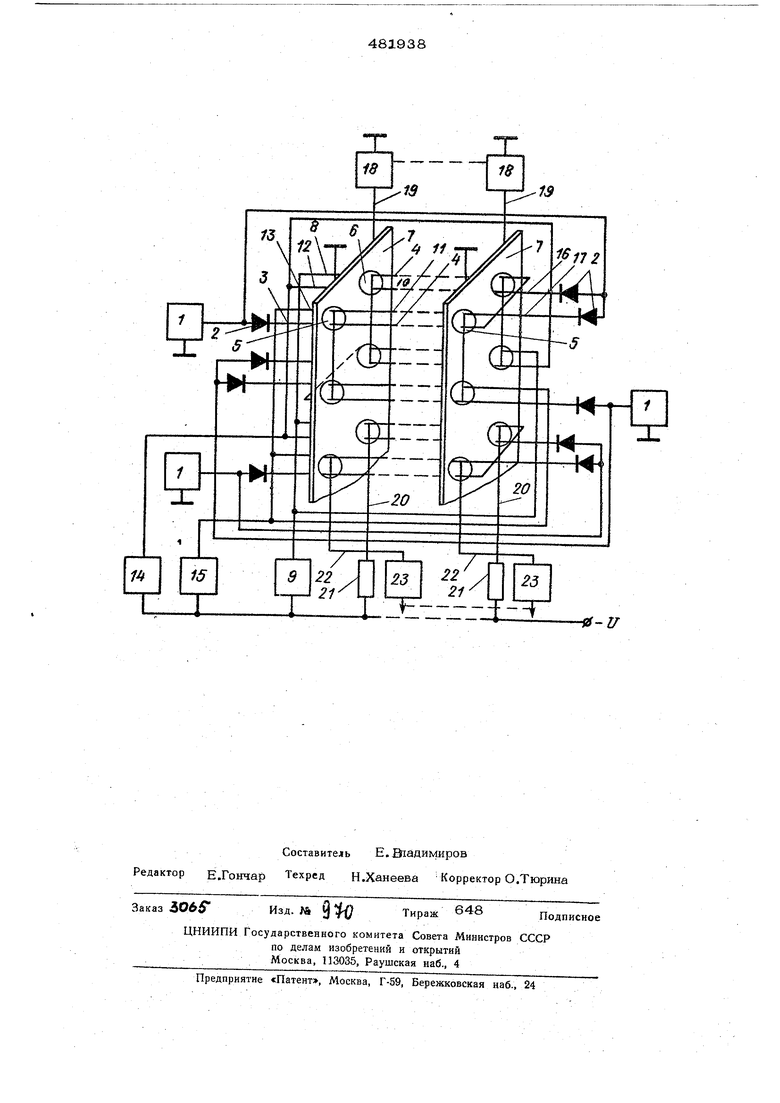

I На чертеже изображено запоминающее j устройство емкостью три ft -разрядных слова.

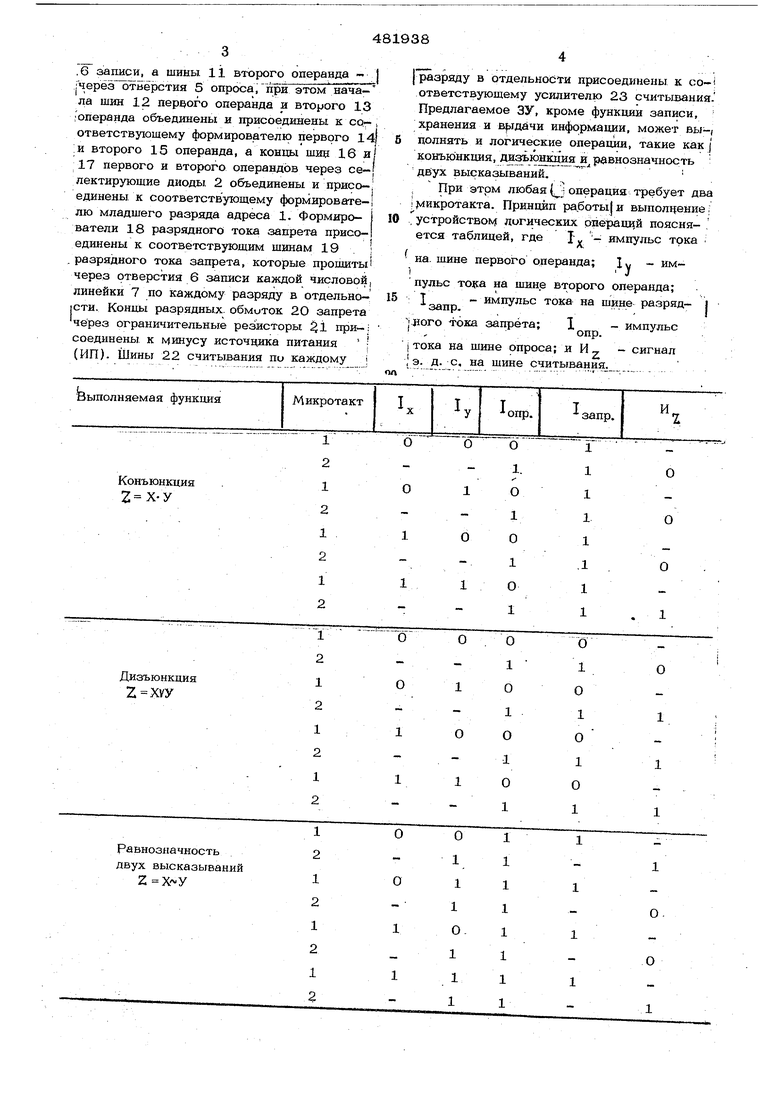

Формирователи 1 младшего разряда ад- реса через селектирующие диоды 2 соединены с началами шин 3 опроса. Шины 4 опроса иропушены через отверстия 5 онроса и встречно через отверстия 6 записи вухотверстных числовых ферритопых линеек 7, при этом концы uiHH 8 опроса объед; нены в группу и присоединен. к формироваелю 9 старшего разряда а/уресгч. Шины 1C) первого операнда прошиты Ч1;;рес) оч Bopci-iiM i , В качестве примера рассмотрил/ вьшол нение ЗУ операции конъюнкции, при этом сигнал на шине примем за Д., а его отсутствие за О. а. Пусть в микротакте t , i 0, При данных усло (запр.) ВИЯХ участок ферромагнитного материала вокруг отверстия записи будет перемагничен по направлению против часовой стрелки. В следующий микротакт t- + 1 I 1и ,в результате опр. запр. которых участок вокруг отверстия опроса также будет перемагничен по направлению против часовой стрелки р сигнала э.д.с. 1.на шине считывания не будет т. е. ,-Лб.. При t; когда залр. нитные потоки oi импульса тока любого операнда и от разрядного тока запрета взаимоскомпенсируются и в следующем микротакте t; сигнала э.д.с. на шине (И2. 0). считывания, не будет в. При 1 магнитные потоки от разрядно;о тока запрета и одного операнда взаимокомиенсируются, а импульс тока другого операн да (допустим первого) создаст магнитны поток, который перемагнитит участок вок руг отверстия записи по направлению час вой стрелки. В следующий микротакт t.; 1.4-1 7 1 магнитный перемагнитит участок вокруг отверстия опроса по направлению против часовой стрелки. В результате этого появится си И, -I- М на шине считывании э.д.с. па шипе win 1х.иэс11 1л п ИМ образом будет выполнена опоряция Х-У. Предмет изобретения Запоминающее устройство, содер.н а1иее накопитель на числовых ферритовых ли11ейках с отверстиями записи и опроса, прошитыми соответственно ,шинами считывании, разрядного тока запрета и опроса, причем каждая шина .огфоса проши-.га через оаверстин опроса в прямом направлении по каждому адресу в отдельности, формирователи адресных и разрядных токов и усилители считывания, подключенные к соответствующим обмоткам, и селектирующие диоды, отличающееся тем, что, с целью расширения функциональных возможнс т стей, оно содер 1шт формирова гели младшего разряда адреса, формирователь старшего разряда адреса и формирователи первого и второго операндов, под1и1ючеиные соответственно к началам шин первого и второго операндов; каждая шина опроса npoiuuTa дополнительно через отверстия записи в обратном направлении по каждому адресу и отдельности, начала шин опроса через селектирующие диоды соединены с соответ- j ствующим.и формирователями млади./е1Ю разряда адреса, а концы шин опроса подключены к формирователю старшего разргща адреса; шщ1Ь1 первого и второго операндов прошиты соответственно через отвё}х::тия записи и отверстия опроса всех числовых ферритовых линеек по каждому адресу в отдельности, причем концы этих шин через селектирующие диоды соединены с соответствутощими формиро1 телями мдадшего раз-, ряда адреса. и

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое полноточное запоминающее устройство | 1974 |

|

SU470861A1 |

| Накопитель | 1973 |

|

SU474846A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| Запоминающее устройство | 1973 |

|

SU444239A1 |

| О ПЛТЕНТИО--<^TE]'liH4^C"Ai] | 1973 |

|

SU374604A1 |

| Управляемый вероятностный двоичный элемент | 1973 |

|

SU465631A1 |

| Накопитель магнитного оперативного запоминающего устройства | 1974 |

|

SU498647A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Логическое запоминающее устройство | 1980 |

|

SU942152A1 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

Авторы

Даты

1975-08-25—Публикация

1973-09-14—Подача