t

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах с общей памятью..

По основному авт. св. 458828 известно устройство приоритета для блочной памяти, содержащее блок анализа состояния блоков памяти, блок анализа внутригруппового приоритета, блок, анёшиза приоритета 4ежду группак« и блок формирбвания сигнала начала работа блоков пгиляти lij .

Недостатком известного устройства является то, что при неисправности какого-либо блока памяти процессор, обратившийся к этому блоку памяти и не получив ответа, может войти в состояние зависания.

Цель изобретения - расширение функциональных возможностей устройства за счёт обеспечения вывода про-, цёссоров из состояния зависания при неисправности какого-либо модуля памяти.

Поставленная цель достигается тем, что в устройство для приоритетно го обращения процессоров к памяти введены п блоков вывода процессоров из состояния зависания (п равно числу модул ей памяти), при-

чем каждый блок вывода процессоров из состояния зависания содержит два триггера, элемент И и три элемента И-НЕ, причем нулевой вход первого триггера соединен с выходом первого элемента И-НЕ, единичный вход первого триггера соединен с выходом элемента. И, нулевой выход триггера соединен с единичным входом

to второгчз триггера,единичный выход первого триггера соединен с соответствующим дополнительным управляющим входом блока анализа состояния модулей памяти и с первым входом

15 второго элемента И-НЕ, выход которого соединен с нулевым входом второго триггера, первые входы элемента И и первого элемента И-НЕ соединены с сигнальным входом устройства, пер20вый и второй дополнительные входы устройства соединены соответственно с тактовым входом второго триггера и с первым входом третьего элемента И-НЕ каждого блока вывода процессо25ров из состояния зависания, единичный выход в.торого триггера соединен со вторым входом третьего элемента И-НЕ, эыход которого соединен со вторыми входами первого, второго элв(.ментов И-НЕ, элемента И и с соот30

ветствуюишм выходом сбоя занятости устройства.

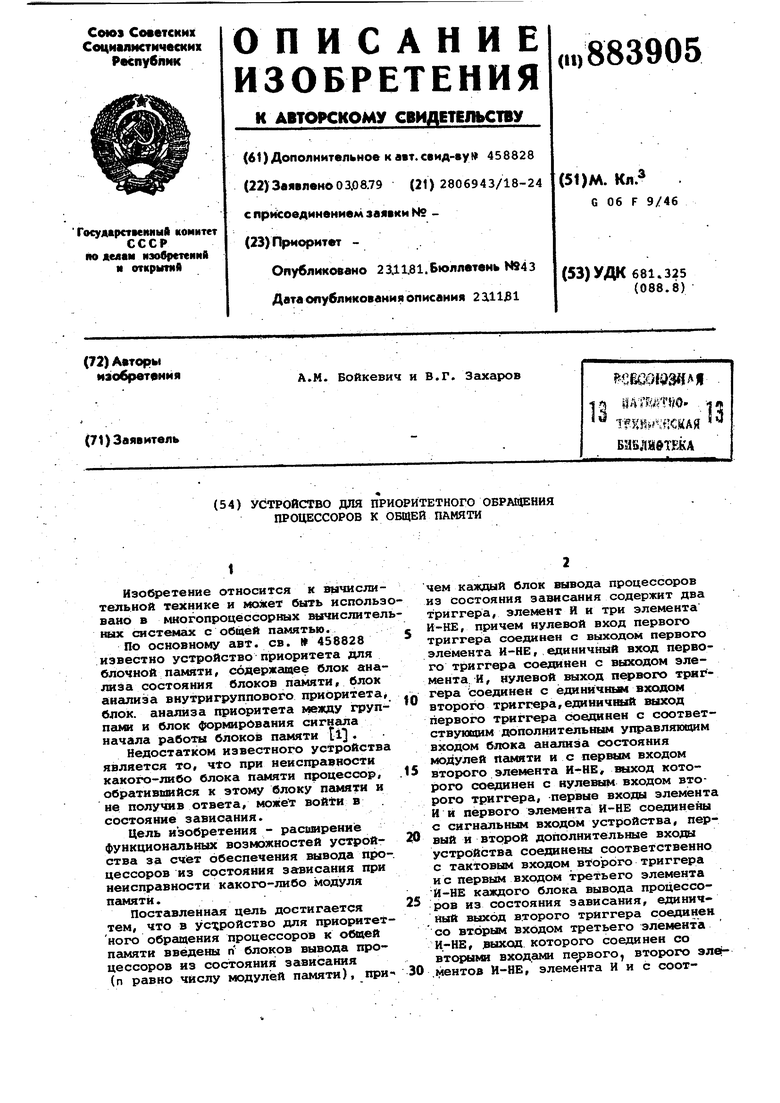

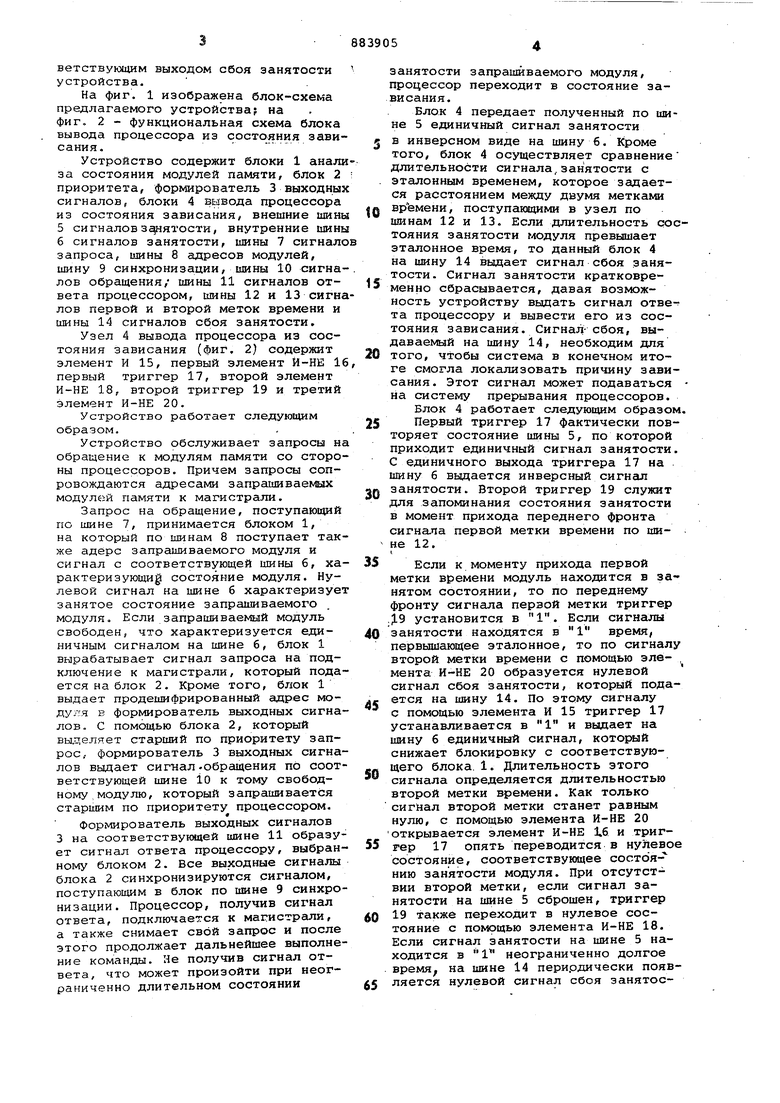

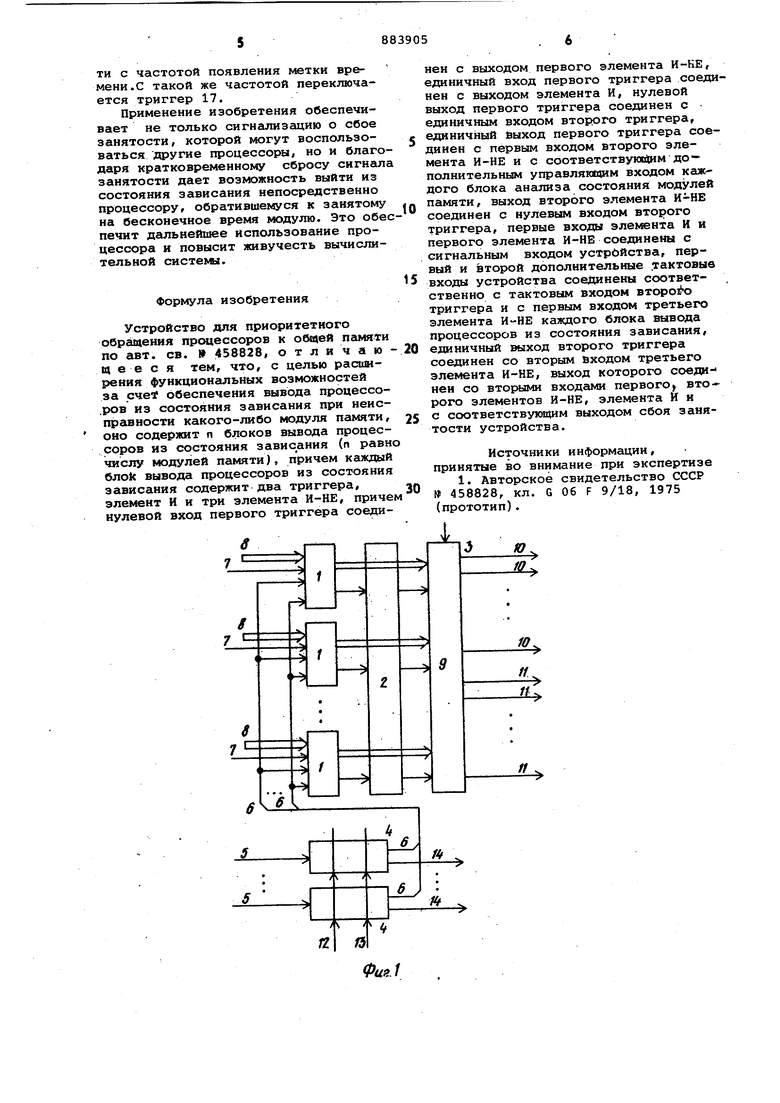

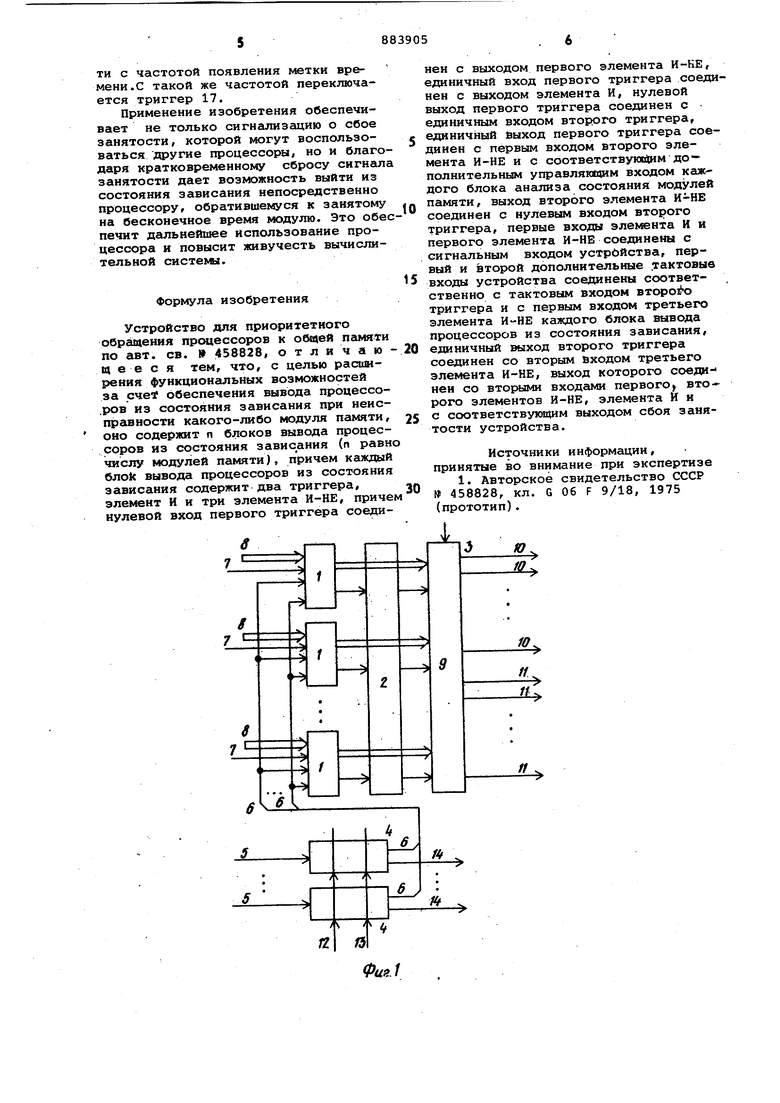

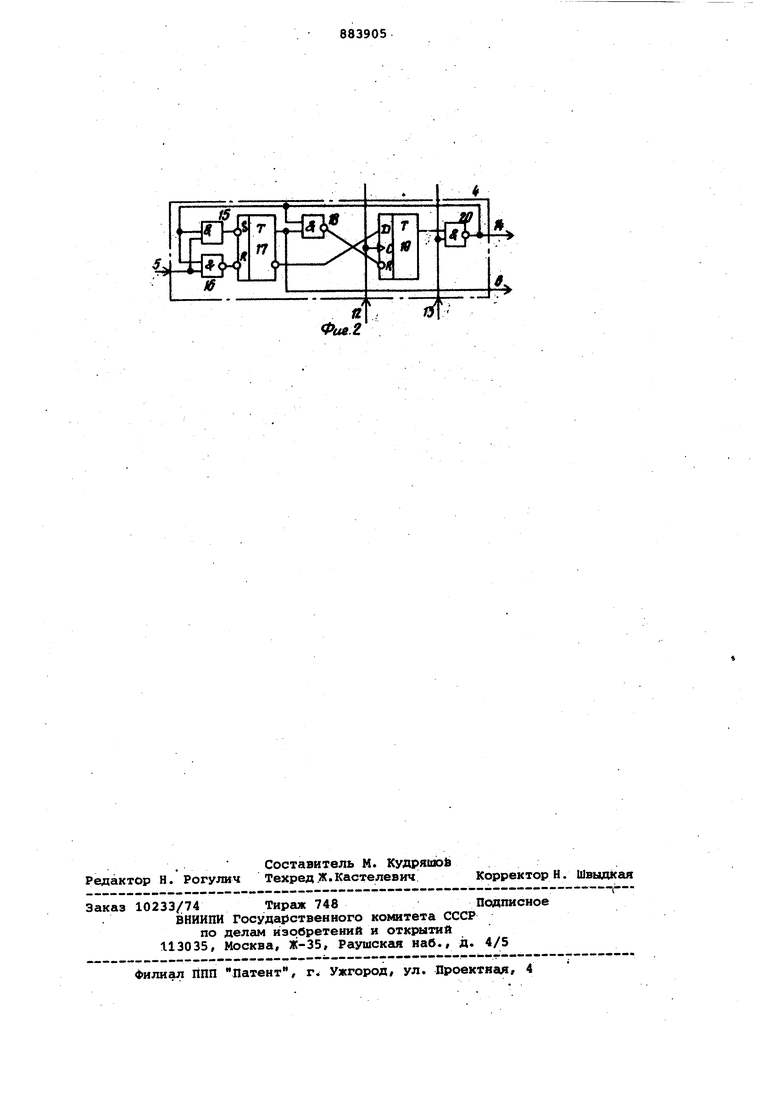

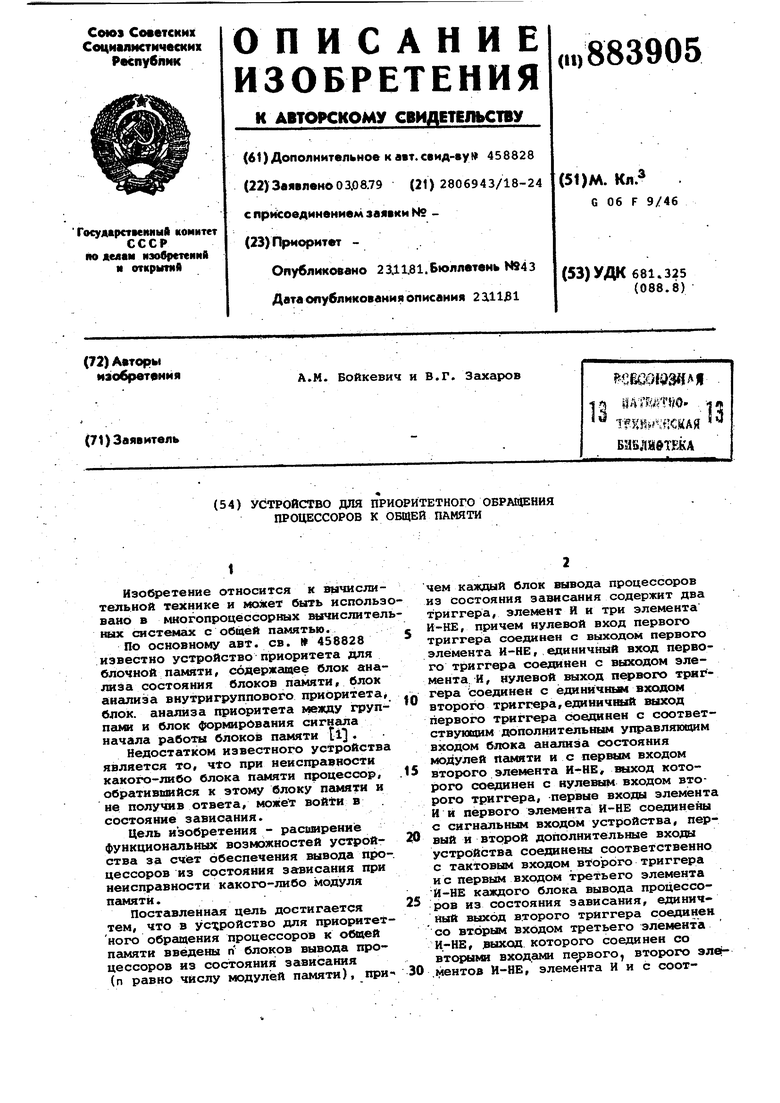

На фиг. 1 изображена блок-схема предлагаемого устройства на фиг. 2 - функциональная схема блока вывода процессора из состояния зависания.

Устройство содержит блоки 1 анализа состояния модулей памяти, блок 2 приоритета, формирователь 3 выходных сигналов, блоки 4 вывода процессора из состояния зависания, внешние шины

5сигналов з ятости, внутренние шины

6сигналов занятости, шины 7 сигнало запроса, шины 8 адресов модулей, шину 9 синхронизации, шины 10 сигналов обращения/ шины 11 сигналов ответа процессором, шины 12 и 13 сигналов первой и второй меток времени и шины 14 сигналов сбоя занятости.

Узел 4 вывода процессора из состояния зависания (фиг, 2) содержит элемент И 15, первый элемент Й-НЕ 16 первый триггер 17, второй элемент И-НЕ 18, второй триггер 19 и третий элемент И-НЕ 20.

Устройство работает следукяцим образом.

Устройство обслуживает запросы на обращение к модулям памяти со стороны процессоров. Причем запросы сопровождаются адресами запрашиваемых модулей памяти к магистрали.

Запрос на обращение, поступающий по шине 7, принимается блоком 1, на который по шинам 8 поступает также адерс запрашиваемого модуля и сигнал с соответствующей шины 6, характеризующи| состояние модуля. Нулевой сигнал на шине б характеризует занятое состояние запрашиваемого модуля. Если запрашиваемый модуль свободен, что характеризуется единичным сигналом на шине б, блок 1 вырабатывает сигнал запроса на подключение к магистрали, который подается на блок 2. Кроме того, блок 1 выдает продешифрированный сщрес модуля в формирователь выходных сигналов. С помощью блока 2, который вы,целяет старший по приоритету запрос, формирователь 3 выходных сигналов выдает сигнал-обращения по соответствующей шине 1о к тому свободному модулю, который запрашивается старшим по приоритету процессором.

Формирователь выходных сигналов 3 на соответствующей шине 11 образует сигнал ответа процессору, выбранному блоком 2. Все выходные сигналы блока 2 синхронизируются сигналом, поступающим в блок по шине 9 синхронизации. Процессор, получив сигнал ответа, подключается к магистрали, а также снимает свой запрос и после этого продолжает дальнейшее выполнение команды. Не получив сигнал ответа, что может произойти при неограниченно длительном состоянии

занятости запрашиваемого модуля, процессор переходит в состояние зависания.

Блок 4 передает полученный по шине 5 единичный сигнал занятости в инверсном виде на шину б. Кроме того, блок 4 осуществляет сравнение Длительности сигнала,занятости с эталонным временем, которое задается расстоянием между двумя метками времени, поступакицими в узел по шинам 12 и 13. Если длительность состояния занятости модуля превышает эталонное время, то данный блок 4 на шину 14 выдает сигнал сбоя занятости. Сигнал занятости кратковременно сбрасывается, давая возможность устройству выдать сигнал отве- та процессору и вывести его из состояния зависания. Сигнал- сбоя, выдаваемый на шину 14, необходим для того, чтобы система в конечном итоге смогла локализовать причину зависания. Этот сигнал может подаваться на систему прерывания процессоров.

Блок 4 работает следующим образом.

Первый триггер 17 фактически повторяет состояние шины 5/ по которой приходит единичный сигнал занятости. С единичного выхода триггера 17 на шину б выдается инверсный сигнал занятости. Второй триггер 19 служит для запоминания состояния занятости в момент прихода переднего фронта сигнала первой метки времени по шине 12.

Если к моменту прихода первой метки времени модуль находится в занятом состоянии, то по переднему фронту сигнала первой метки триггер ,j.9 установится в 1. Если сигналы

0 занятости находятся в 1 время, первышающее эталонное, то по сигналу второй метки времени с помощью элемента И-НЕ 20 образуется нулевой сигнал сбоя занятости, который подается на шину 14. По этому сигналу с помощью элемента И 15 триггер 17 устанавливается в 1 и выдает на шину 6 единичный сигнал, которлй снижает блокировку с соответствующего блока 1. Длительность этого сигнала определяется длительностью второй метки времени. Как только сигнал второй метки станет равным нулю, с помощью элемента И-НЕ 20 открывается элемент И-НЕ 1,6 и триггер 17 опять переводится в нулевое состояние, соответствующее состоянию занятости модуля. При отсутствии второй метки, если сигнал занятости на шине 5 сброшен, триггер 19 также переходит в нулевое состояние с помощью элемента И-НЕ 18. Если сигнал занятости на шине 5 находится в 1 неограниченно долгое . время, на шине 14 перирдически появляется нулевой сигнал сбоя занятости с частотой появления метки времени.С такой же частотой переключается триггер 17. Применение изобретения обеспечивает не только сигнализацию о сбое занятости, которой могут воспользоваться другие процессоры, но и благо даря кратковременному сбросу сигнал занятости дает возможность выйти из состояния зависания непосредственно процессору, обратившемуся к занятому на бесконечное время модулю. Это обе печит дгшьнейшее использование процессора и повысит живучесть вычислительной cиcтe ad. Формула изобретения Устройство для приоритетного обращения прсздессоров к общей пгиляти по авт. св. 458828, о т л и ч а ю щ е е с я тем, что, с целью расимремия функциональных возможностей за счеФ обеспечения вывода процессо.ров из состояния зависания при неиспргшности какого-либо модуля памяти, оно содержит п блоков вывода процессоров из состояния завис ания (п равн числу модулей памяти), причем каж}ЗкЛ блок вывода процессоров из состояния зависания содержит два триггера, элемент И и три элемента И-НЕ, приче кулевой вход первого триггера соединен с выходом первого элемента И-КЕ, единичный вход первого триггера соединен с выходом элемента И, нулевой выход первого триггера соединен с единичным входом второго триггера, единичный выход первого триггера соединен с первым входом второго элемента И-НЕ и с соответствукхДим дополнительным управляющим входом каж дого блока анализа состояния модулей памяти, выход второго элемента И-НВ соединен с нулевым входом второго триггера, первые входы элемента И и первого элеглета И-НЕ соединены с сигнальным входом устройства, первый и второй дополнительные .тактовые входы устройства сое1и1нены соответственно с тактовым входом BTOpoiho триггера и с первым входом третьего элемента И-НЕ каждого блока вывода процессоров из состояния зависания, единичный выход второго триггера соединен со вторым входом третьего элемента И-НЕ, выход которого соединен со вторыми входами первогоj второго элементов И-НЕ, элемента И и с соответствующим выходом сбоя занятости устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 458828, кл. G Об F 9/18, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1979 |

|

SU840905A1 |

| Сбоеустойчивое микропрограммное устройство управления | 1982 |

|

SU1101823A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для приоритетного обращения к общей памяти | 1986 |

|

SU1425669A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1444770A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство для диагностики ошибок ЭВМ | 1980 |

|

SU1012260A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

Авторы

Даты

1981-11-23—Публикация

1979-08-03—Подача