предзарядного транзистора, затвор которого подключен к затвору первого предзарядного транзистора, сток шестого разрядного транзистора подключен к затвору второго зарядного транзистора и истоку четвертого предзарядного транзистора, затвор которого подключен к затвору второго предзарядного транзистора, исток первого зарядного транзистора подключен к стоку седьмого зарядного транзистора и является одним выходом усилителя, исток второго зарядного транзистора подключен к стоку восьмого зарядного транзистора и явля:ется другим выходом усилителя, стоки первого и второго зарядных тран зисторов, третьего и четвертого презарядных транзисторов подключены к другой шине питания, сток адресного транзистора подключен к стоку первого нагрузочного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

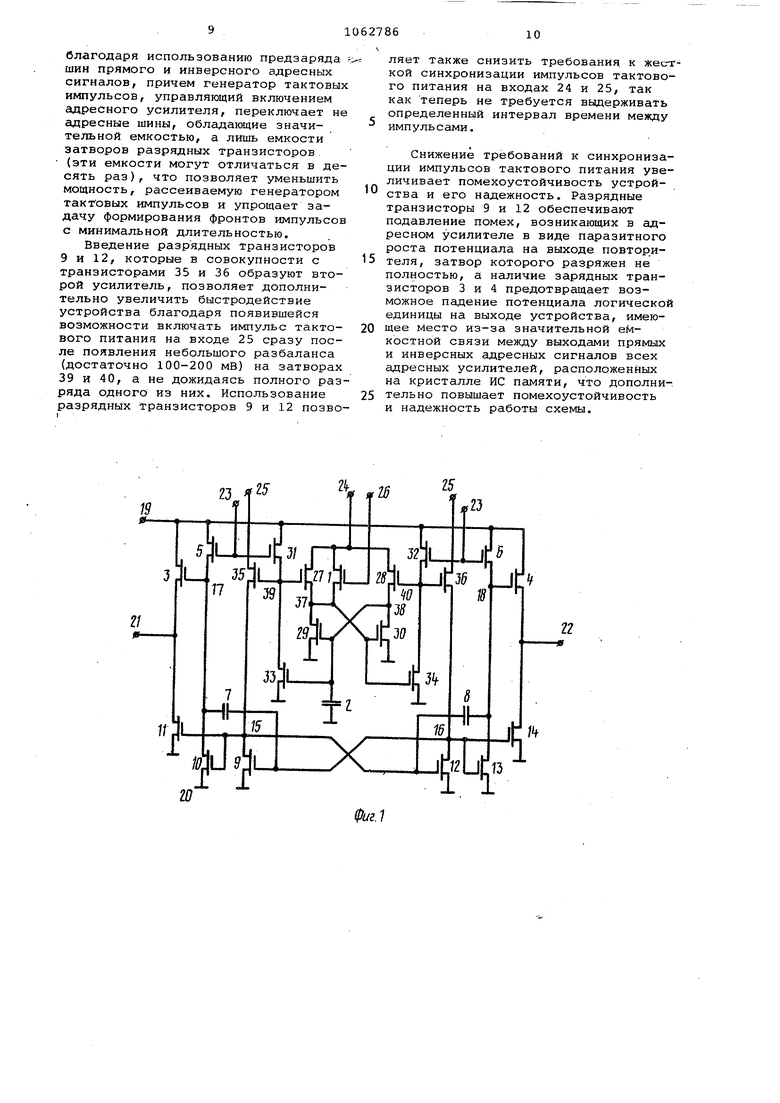

АДРЕСНЫЙ УСИЛИТЕЛЬ, содержащий ключевые транзисторы, истоки которых подключены к одной шине питания, сток первого ключевого транзистора подключен к истоку первого нагрузочного транзистора, к затвору второго ключевого транзистора и к истоку адресного транзистора, сток второго ключевого транзистора подключен к истоку второго нагрузочного транзистора и к затвору первого ключевого транзистора, разрядные транзисторы, истоки которых подключены к одной шине питания, затворы первого и второго разрядных транзисторов подключены к затворам соответствующих ключевых транзисторов,сток первого разрядного транзистора подключен к затвору первого нагрузочного транзистора, к истоку первого предзарядногр транзистора и к затвору первого повторяющего транзистора, сток второго разрядного транзистора подключен к затвору второго нагрузочного транзистора, к истоку второго предзарядного транзистора и к затвору второго повторяющего транзистора, затвор первого предзарядного транзистора подключен к затвору второго предзарядного транзистора и является первым тактовым входом усилителя, сток первого повторяющего Tpaj зистора подключен к стоку второго пoвтqpяющeгo транзистора и является вторым тактовым входом усилителя, сток первого нагрузочного транзистора подключен к стоку второго нагрузочного транзистора и является третьим тактовым входом усилителя, стоки первого и второго нагрузочного транзисторов подключены к другой шине питания, затвор адресного транзистора является первым управляющим входом усилителя, о тличающийся тем, что, с целью повышения быстродействия усилителя, он содержит третий, четвертый, пятый,шестой седьмой и восьмой раз(Л рядные транзисторы,первый и второй зарядные транзисторы,третий и четвер тый предзарядные транзисторы и конденсаторы, первый из которых включен между стоком и затвором первого разрядного транзистора и одной шиной питания, второй конденсатор включен .между затвором третьего разрядного транзистора и стоком четвертого разрядного транзистора, третий конденсатор включен между затвором пятого разрядного транзистора и стоком шестого разрядного транзистора, сток третьего разрядного транзистора подключен к истоку первого повторяющего транзистора и к затворам четвертого, пятого и седьмого разрядных транзисторов, сток пятого разрядного транзистора подключен к истоку второго повторяющего транзистора и к затворам третьего, шестого и восьмого разрядных транзисторов, истоки третьего, четвертого, пятого, шестого, седьмого и восьмого разрядных транзисторов подключены к одной шине питания, сток четвертого разрядного транзистора под.ключен к затвору первого зарядного транзистора и к стоку третьего

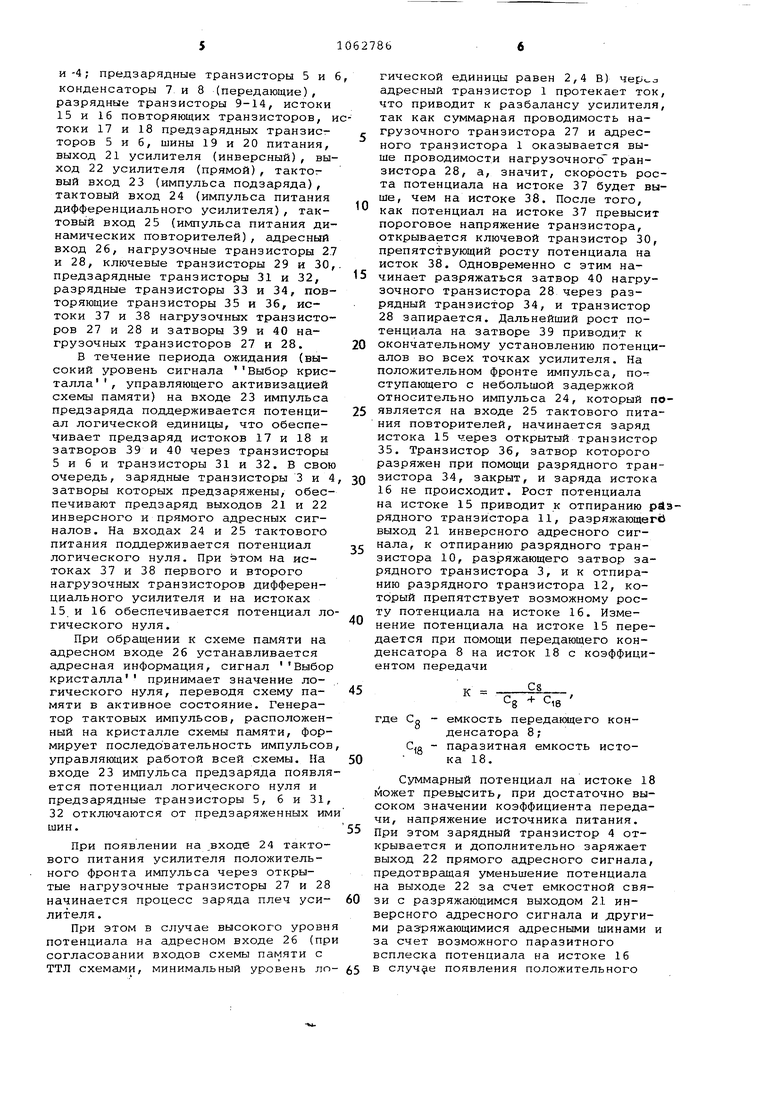

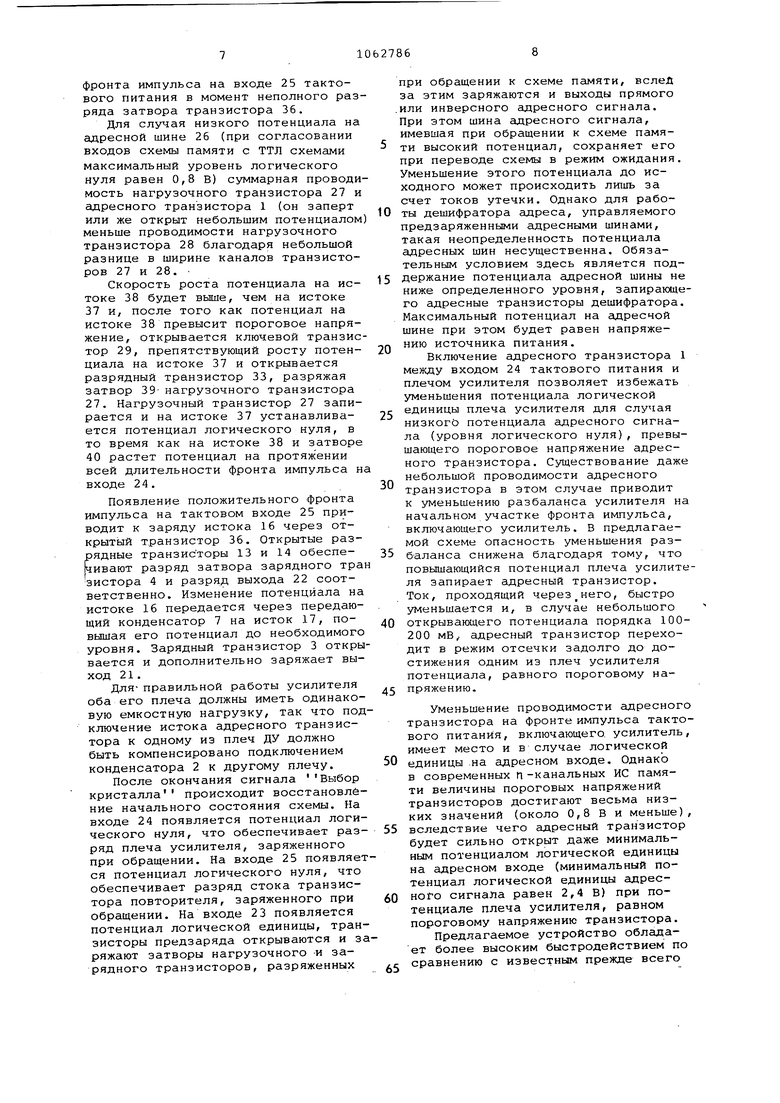

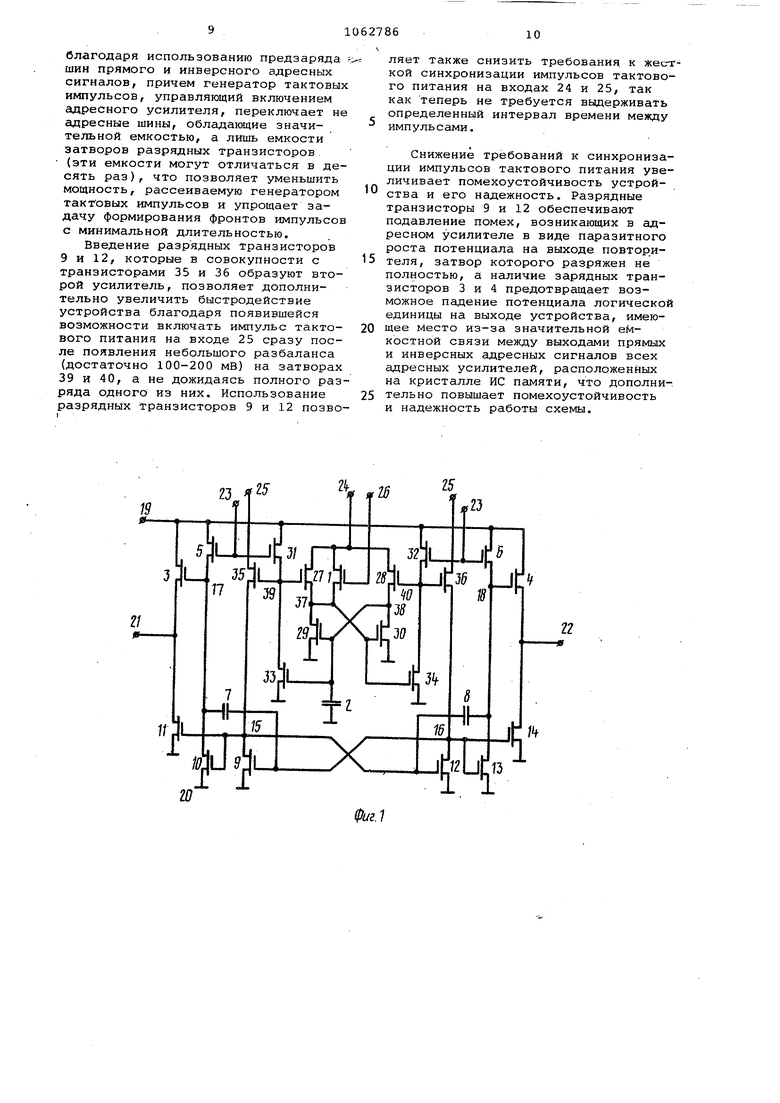

Изобретение относится к микроэлектронике и может быть использовано в микросхемах памяти на МДП транзисторах. В интегральных схемах памяти на МДП транзисторах в качестве адрес|Ных буферов, служащих для согласо|вания входов схемы памяти с ТТЛ схе мами, приема адреса и формирования прямых и инверсных адресных сигналов, обычно используются простые ст тические схемы, в которых формирование адресных сигналов осуществляется при помощи инверторов, бутстрепных каскадов и парафазных каскадов. Использование статических схем приводит к высокому потреблению мощности при сравнительно низком быстродействии схем адресных буфеИзвестны устройства, в которых с целью увеличения быстродействия и уменьшения потребляемой мощности считывание адресной информации стали осуществлять при помощи дифферен циальных усилителей, а формирование прямых и инверсных адресных сигналов - при помощи динамических повторителей, подключенных к каждому и плеч усилителей l . Использование дифференциальных усилителей позволяет с высокой скоростью формировать на затворах тран зисторов повторителей прямой и инверсный адресные сигналы, а использование повторителей позволяет без потерь мощности в адресном буфере установить информацию на адресных шинах. Недостатком данных устройств является низкое быстродействие. Наиболее близким техническим решением к изобретению является ащресный усилитель, содержащий два кл чевых транзистора, стоки каждого из которых подключены к истоку соответ ствующего нагрузочного транзистора и к затвору другого ключевого транзистора. Затвор каждого из нагрузочных транзисторов объединен с затвором соответствующего выходного повторяющего транзистора и подключен к истоку соответствующего предзаряжающего транзистора 2 . Благодаря минимальной емкостной нагрузке плеч дифференциального усилителя обеспечивается высокая чувствительность схемы, а нагрузочные транзисторы одновременно выполняют роль динамических повторителей (ДП), что обеспечивает высокую скорость заряда плеча. Однако в известном усилителе схемы адресных буферов, в которых использованы ДП для формирования адресных сигналов, обладают меньшим быстродействием по сравнению со схемами, использующими принцип предзаряда. Вследствие того, что суммарная емкость адресных шин, заряжаемая генератором тактовых импульсов, достигает величины 40-50 пФ при емкости адресной шины, равной 4-5 пФ, длительность фронта импульса при заряде адресных шин может в 2-3 раза превысить длительность фронта разряда суммарной емкости адресных шин. При использовании дифференциального повторителя шина прямого или инвёрс ного. адресного сигнала,не меняющая бвой потенциал при активации адресного буфера,оказывается отключенной от остальной части схемы. При этом, вследствие значительной емкостной связи между адресными шинами, расположенными на кристалле с максимальной плотностью, изменение потенциала части адресных шин передается с некоторым коэффициентом передачи на адресные шины, отключенные от остальной части схемы. Изменение потенциала адресных шин, вызванное емкостной связью между шинами, может пp вecти к сбою в работе дешифратора адреса, управляемого адресньоми сигналами. , Адресные транзисторы, включенные между плечом усилителя и общей шино источника питания, в случае низких пороговых напряжений могут, при адр ном сигнале, равном логическому нулю, быть открыты и обладать значительной проводимостью, что приводит к уменьшению чувствительности и помехоустойчивости дифференциального усилителя и к пониженному потенциалу логической единицы в одном из плеч усилителя. Кроме того; использование источника опорного напряжения, смещающего один из входов дифференциального усилителя, усложняет схему адресного буфера и для случая низких пороговых напряжений ограничивает возможность использования входных транзисторов с высокой проводимостью вследствие значительного снижения уровня логической единицы в плече усилителя. Цель изобретения - повышение быстроде.йствия адресного усилителя Цель достигается тем, что .в адресный усилитель, содержащий ключевые транзисторы, истоки которых под ключены к одной шине питания, сток первого ключевого транзистора подключен к истоку первого нагрузочного транзистора, к затвору второго ключевого транзистора и к истоку адресного транзистора, сток второго ключевого транзистора подключен к истоку второго нагрузочного транзистора и к затвору первого ключево го транзистора, разрядные транзисторы, истоки которых подключены к одной шине питания, затворы первого и второго разрядных транзисторов подключены к затворам соответствующих ключевых транзисторов, сток первого разрядного транзистора подключен к затвору первого нагрузочно транзистора, к истоку первого предзарядного транзистора и к затвору первого повторяющего транзистора, сток второго разрядного транзистор подключен к затвору второго нагрузочного транзистора, к истоку второго предзарядного транзистора и к затвору второго повторяющего транзистора, затвор первого предзарядного транзистора подключен к затвору второго предзарядного транзис тора и является nepBtJM тактовым вхо дом усилителя, сток первого повторяющего транзистора подключен к сто ку второго повторяющего транзистор и является вторым тактовым входом усилителя, сток первого нагрузочного транзистора подключен к стоку второго нагрузочного транзистора и является третьим тактовьам входом усилителя, стоки первого и второго нагрузочного транзисторов подключены к другой шине питания, затвор адресного транзистора является первым управляющим входом усилителя, дополнительно введены третий, четвертый, пятый, шестой{седьмой и восьмой разрядные транзисторы, первый и второй зарядные транзисторы, третий и четвертый предзарядные транзисторы и конденсаторы, первый из которых включен между стоком и затвором первого разрядного транзистора и одной шиной питания, второй конденсатор включен между затвором третьего разрядного транзистора и стоком Четвертого разрядного транзистора, третий конденсатор включен между затвором пятого разрядного транзистора и стоком шестого разрядного транзистора, сток третьего разрядного транзистора подключен к истоку первого повторяющего транзистора и к затворам четвертого, пятого и седьмого разрядных транзисторов, сток пятого разрядного транзистора подключен к истоку второго повторяющего транзистора и к затворам третьего, шестого и восьмого разрядных транзисторов, истоки третьего, четвертого, пятого, шестого, седьмого и восьMol7O разрядных транзисторов подключены к одной шине питания, сток четвертого разрядного транзистора подключен к затвору первого зарядного транзистора и к истоку третьего предзарядного транзистора, затвор которого подключен к затвору первого предзарядного транзистора, сток шестого разрядного транзистора подключен к затвору второго зарядного транзистора и истоку четвертого предзарядного транзистора, затвор которого подключен к затвору второго предзарядного транзистора, исток первого зарядного транзистора подключен к стоку седьмого зарядного транзистора и является одним выходом усилителя, исток второго зарядного транзистора подключен к стоку восьмого зарядного транзистора и является другим выходом усилителя, стоки первого и второго зарядных транзисторов, третьего и четвертого предзарядных транзисторов подключены к другой шине питания, сток адресного транзистора подключен к стоку первого нагрузочного транзистора. На фиг. 1 представлена схема предложенного адресного усилителя; на фиг. 2 - временная диаграмма его работы. Адресный усилитель содержит адресный транзистор 1, конденсатор 2 (балансный), зарядные транзисторы 3 и -4; предзарядные транзисторы 5 и конденсаторы 7 и 8 (передающие), разрядные транзисторы 9-14, истоки 15 и 16 повторяющих транзисторов, токи 17 и 18 предзарядных транзисторов 5 и б, шины 19 и 20 питания, выход 21 усилителя (инверсный), вы ход 22 усилителя (прямой) , тактогвый вход 23 (импульса подзаряда), тактовый вход 24 (импульса питания дифференциального усилителя), тактовый вход 25 (импульса питания динамических повторителей), адресный вход 26, нагрузочные транзисторы 27 и 28, ключевые транзисторы 29 и 30 предзарядные транзисторы 31 и 32, разрядные транзисторы 33 и 34, повторяющие транзисторы 35 и 36, истоки 37 и 38 нагрузочных транзисторов 21 и 28 и затворы 39 и 40 нагрузочных транзисторов 27 и 28. В течение периода ожидания (высокий уровень сигнала Выбор кристалла, управляющего активизацией схемы памяти) на входе 23 импульса предзаряда поддерживается потенциал логической единицы, что обеспечивает предзаряд истоков 17 и 18 и затворов 39 и 40 через транзисторы 5 и 6 и транзисторы 31 и 32. В свою очередь, зарядные транзисторы 3 и 4 затворы которых предзаряжены, обеспечивают предзаряд выходов 21 и 22 инверсного и прямого адресных сигналов. На входах 24 и 25 тактового питания поддерживается потенциал логического нуля. При этом на истоках 37 и 38 первого и второго нагрузочных транзисторов дифференциального усилителя и на истоках 15 и 16 обеспечивается потенциал ло гического нуля. При обращении к схеме памяти на адресном входе 26 устанавливается адресная информация, сигнал Выбор кристалла принимает значение логического нуля, переводя схему памяти в активное состояние. Генератор тактовых импульсов, расположенный на кристалле схемы памяти, формирует последовательность импульсов управляющих работой всей схемы. На входе 23 импульса предзаряда появля ется потенциал логич.еского нуля и предзарядные транзисторы 5, 6 и 31, 32 отключаются от предзаряженных им шин. При появлении на .входе 24 тактового питания усилителя положительного фронта импульса через открытые нагрузочные транзисторы 27 и 28 начинается процесс заряда плеч усилителя. При этом в случае высокого уровн потенциала на адресном входе 26 (пр согласовании входов схемы памяти с ТТЛ схемами, минимальный уровень ло гической единицы равен 2,4 В) чер1...э адресный транзистор 1 протекает ток, что приводит к разбалансу усилителя, так как суммарная проводимость нагрузочного транзистора 27 и адресного транзистора 1 оказывается выше проводимости нагрузочногсГ транзистора 28, а, значит, скорость роста потенциала на истоке 37 будет выше, чем на истоке 38. После того, как потенциал на истоке 37 превысит пороговое напряжение транзистора, открывается ключевой транзистор 30, препятствующий росту потенциала на исток 38. Одновременно с этим начинает разряжаться затвор 40 нагрузочного транзистора 28 через разрядный транзистор 34, и транзистор 28 запирается. Дальнейший рост потенциала на затворе 39 приводит к окончательному установлению потенциалов во всех точках усилителя. На положительном фронте импульса, по-г ступающего с небольшой задержкой относительно импульса 24, который появляется на входе 25 тактового питания повторителей, начинается заряд истока 15 через открытый транзистор 35. Транзистор 36, затвор которого разряжен при помощи разрядного транзистора 34, закрыт, и заряда истока 16 не происходит. Рост потенциала на истоке 15 приводит к отпиранию разрядного транзистора 11, разряжающегй выход 21 инверсного адресного сигнала, к отпиранию разрядного транзистора 10, разряжающего затвор зарядного транзистора 3, и к отпиранию разрядного транзистора 12, который препятствует возможному росту потенциала на истоке 16. Изменение потенциала на истоке 15 передается при помощи передающего конденсатора 8 на исток 18 с коэффициентом передачи где С,, - емкость передающего конденсатора 8; - паразитная емкость истока 18. Суммарный потенциал на истоке 18 может превысить, при достаточно высоком значении коэффициента передачи, напряжение источника питания. При этом зарядный транзистор 4 открывается и дополнительно заряжает выход 22 прямого адресного сигнала, предотвращая уменьшение потенциала на выходе 22 за счет емкостной связи с разряжающимся выходом 21 инверсного адресного сигнала и другими разряжающимися адресными шинами и за счет возможного паразитного всплеска потенциала на истоке 16 в случае появления положительного

фронта импульса на входе 25 тактового питания в момент неполного разряда затвора транзистора 36.

Для случая низкого потенциала на адресной шине 26 (при согласовании входов схемы памяти с ТТЛ схемами максимальный уровень логического нуля равен 0,8 В) суммарная проводимость нагрузочного транзистора 27 и адресного транзистора 1 (он заперт или же открыт небольшим потенциалом меньше проводимости нагрузочного транзистора 28 благодаря небольшой разнице в ширине каналов транзисторов 27 и 28.

Скорость роста потенциала на истоке 38 будет выше, чем на истоке 37 и, после того как потенциал на истоке 38 превысит пороговое напряжение, открывается ключевой транзистор 29, препятствующий росту потенциала на истоке 37 и открывается разрядный транзистор 33, разряжая затвор 39- нагрузочного транзистора 27. Нагрузочный транзистор 27 запирается и на истоке 37 устанавливается потенциал логического нуля, в то время как на истоке 38 и затворе 40 растет потенциал на протяжении всей длительности фронта импульса н входе 24.

Появление положительного фронта импульса на тактовом входе 25 приводит к заряду истока 16 через открытый транзистор 36. Открытые разрядные транзисторы 13 и 14 обеспечивают разряд затвора зарядного тра зистора 4 и разряд выхода 22 соответственно. Изменение потенциала на истоке 16 передается через передающий конденсатор 7 на исток 17, повышая его потенциал до необходимого уровня. Зарядный транзистор 3 открывается и дополнительно заряжает выход 21.

Для-правильной работы усилителя оба его плеча должны иметь одинаковую емкостную нагрузку, так что подключение истока адресного транзистора к одному из плеч ДУ должно быть компенсировано подключением конденсатора 2 к другому плечу.

После окончания сигнала Выбор кристалла происходит восстановление начального состояния схемы. На входе 24 появляется потенциал логического нуля, что обеспечивает разряд плеча усилителя, заряженного при обращении. На входе 25 появляется потенциал логического нуля, что обеспечивает разряд стока транзистора повторителя, заряженного при обращении. На входе 23 появляется потенциал логической единицы, транзисторы предзаряда открываются и заряжают затворы нагрузочного и зарядного транзисторов, разряженных

при обращении к схеме памяти, вслед за этим заряжаются и выходы прямого .или инверсного адресного сигнала. При этом шина адресного сигнала, имевшая при обращении к схеме памяти высокий потенциал, сохраняет его при переводе схемы в режим ожидания. Уменьшение этого потенциала до исходного может происходить лишь за счет токов утечки. Однако для работы дешифратора адреса, управляемого предзаряженными адресными шинами, такая неопределенность потенциала адресных шин несущественна. Обязательным условием здесь является поддержание потенциала адресной шины не ниже определенного уровня, запирающего адресные транзисторы дешифратора. Максимальный потенциал на адресной шине при этом будет равен напряжению источника питания.

Включение адресного транзистора 1 между входом 24 тактового питания и плечом усилителя позволяет избежать уменьшения потенциала логической единицы плеча усилителя для случая низкого потенциала адресного сигнала (уровня логического нуля), превышающего пороговое напряжение адресного транзистора. Существование даже небольшой проводимости адресного транзистора в этом случае приводит к уменьшению разбаланса усилителя на начальном участке фронта импульса, включающего усилитель. В предлагаемой схеме опасность уменьшения разбаланса снижена благодаря тому, что повышающийся потенциал плеча усилителя запирает адресный транзистор. Ток, проходящий через него, быстро уменьшается и, в случае небольшого открывающего потенциала порядка 100200 мВ адресный транзистор переходит в режим отсечки задолго до достижения одним из плеч усилителя потенциала, равного пороговому напряжению.

Уменьшение проводимости адресного транзистора на фронте импульса тактового питания, включающего, усилитель имеет место и в случае логической единицы -на адресном входе. Однако в современных П-канальных ИС памяти величины пороговых напряжений транзисторов достигают весьма низких значений (около 0,8 В и меньше) вследствие чего адресный транзистор будет сильно открыт даже минимальным потенциалом логической единицы на адресном входе (минимальный потенциал логической единицы адресного сигнала равен 2,4 В) при потенциале плеча усилителя, равном пороговому напряжению транзистора.

Предлагаемое устройство обладает более высоким быстродействием по сравнению с известным прежде всего

благодаря использованию предзаряда шин прямого и инверсного адресных сигналов, причем генератор тактовых импульсов, управляющий включением адресного усилителя, переключает не адресные шины, обладающие значительной емкостью, а лишь емкости затворов разрядных транзисторов (эти емкости могут отличаться в десять раз), что позволяет уменьшить мощность, рассеиваемую генератором тактовых импульсов и упрощает задачу формирования фронтов импульсов с минимальной длительностью.

Введение разрядных транзисторов 9 и 12, которые в совокупности с транзисторами 35 и 36 образуют втоой усилитель, позволяет дополнительно увеличить быстродействие устройства благодаря появившейся возможности включать импульс тактового питания на входе 25 сразу после появления небольшого разбаланса (достаточно 100-200 мВ) на затворах 39 и 40, а не дожидаясь полного разряда одного из них. Использование разрядных транзисторов 9 и 12 позволяет также снизить требования, к жес-гкой синхронизации импульсов тактового питания на входах 24 и 25, так как теперь не требуется выдерживать определенный интервал времени между импульсами.

Снижение требований к синхронизации импульсов тактового питания увеличивает помехоустойчивость устройства и его надежность. Разрядные транзисторы 9 и 12 обеспечивают подавление помех, возникающих в адресном усилителе в виде паразитного роста потенциала на выходе повторителя, затвор которого разряжен не полностью, а наличие зарядных транзисторов 3 и 4 предотвращает возможное падение потенциала логической единицы на выходе устройства, имеющее место из-за значительной емкостной связи между выходами прямых и инверсных адресных сигналов всех адресных усилителей, расположенных на кристалле ИС памяти, что дополни5 тельно повышает помехоустойчивость и надежность работы схемы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4146862, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Уилсон Д | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Электроника, 1978, 7, с.32-37 (прототип). | |||

Авторы

Даты

1983-12-23—Публикация

1982-05-13—Подача