Известны десятичные счетчики на двухтактных ферротранзисторных элементах, содержашие триггеры со счетны.-л входом и сдвиговые регистры.

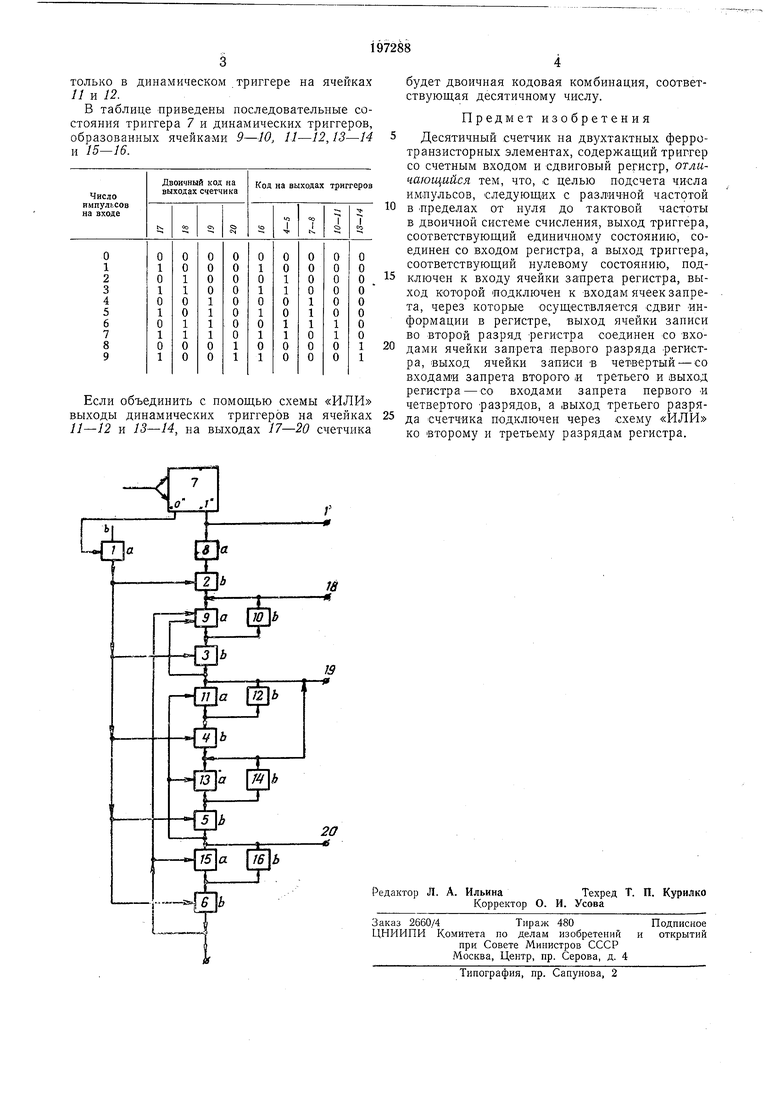

Предлагаемый счетчик отличается от известных тем, что выход триггера, соответствующий единичному состоянию, соединен со входом регистра, а выход, соответствующий нулевому состоянию - со входом ячейки запрета регистра, выход которсш подключен ко входам ячеек запрета, через которые осуществляется сдвиг информации в 11егистре. Выход ячейки записи во второй разряд регистра подсоединен ко входам ячейки запрета первого разряда регистра, выход ячейки записи в четвертый--ко входам запрета второго и третьего и выход регистра- ко входам запрета первого и четвертого разрядов. Выход третьего разряда счетчика подключен через схему «ИЛИ ко второму и третьему разрядам регистра.

Это позволяв г считать импульсы, следующие с различной частотой в пределах от нуля до тактовой в двоичной системе счисления.

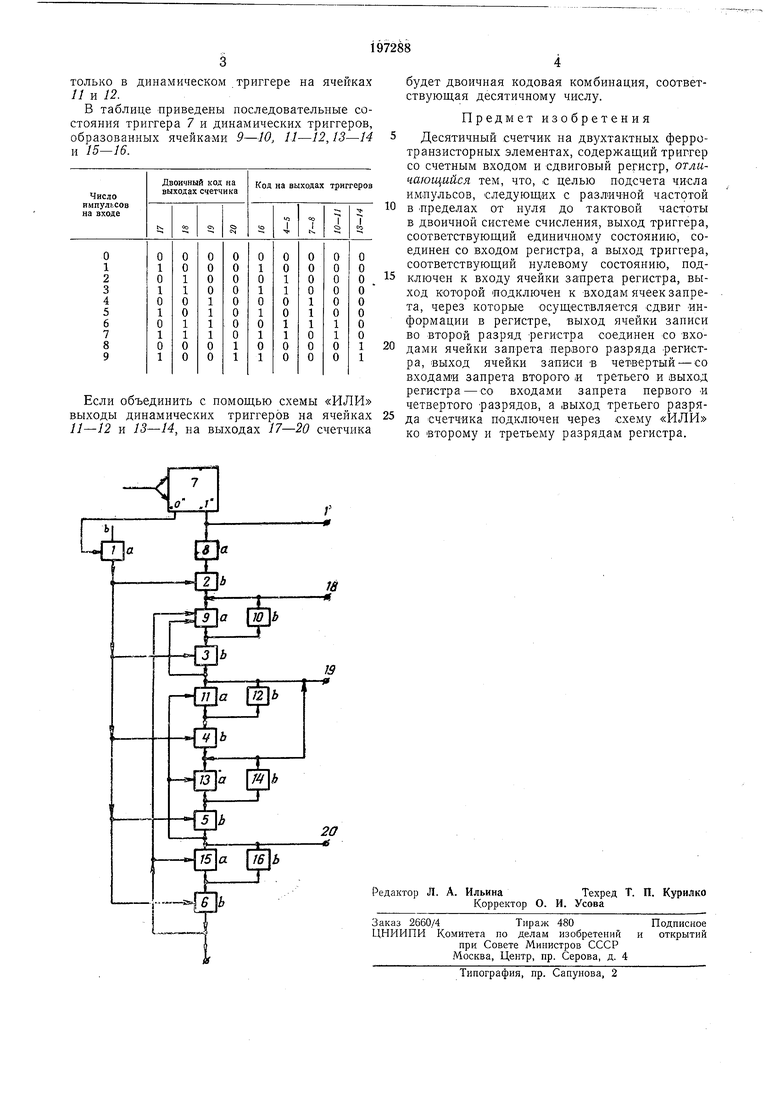

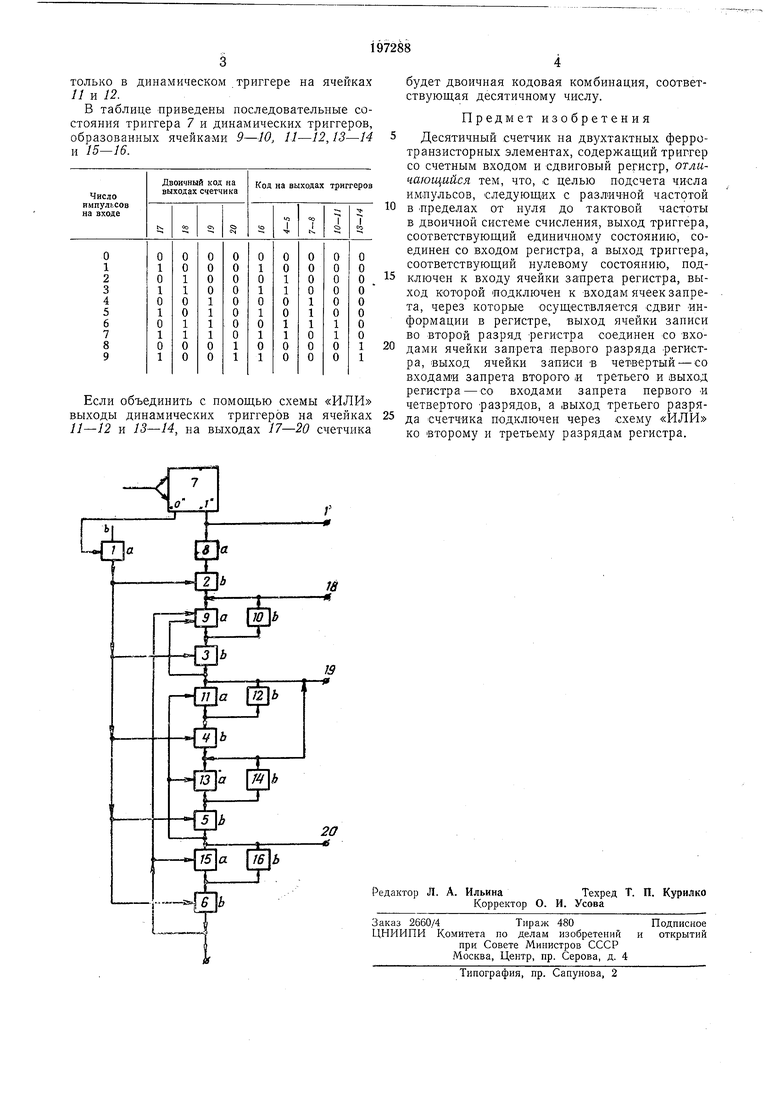

На чертеже представлена логическая схема счетчика.

Ферротранзясторные ячейки управляются фазами такто-юй частоты (а и 6). В исходном состоянии на выходе всех элементов, за исключением ячейки 1, сигналы отсутствуют.

Поскольку Б ячейку 1 непрерывно записываются импульсы такта Ь, в такт с его выхода будут все время .поступать сигналы запрета на ячейки 2-6. После подачи на выход триггера 7 импульса с его выхода «1 на ячейку 8 начнут поступать импульсы с тактовой частотой. Но с выхода ячейки 5 эти импульсы в ячейку 2 записываться не могут из-за сигналов запрета ячейки /.

Если на вход схемы подается второй импульс, триггер 7 переходит в исходное состояние, а с его выхода «О поступает импульс переноса, запрещающий выходной сигнал с ячейки 1. В такт а снимается запрет с ячейки 2 и в нее будет записана единица с ячейки 8. Далее в такт b единица из ячейки 2 перепишется Б ячейку /. Таким образом, из ячейки 9 единица может переписываться только в ячейку 10, так как ячейка 1 вновь выдает импульсы запрета. До следующего сигнала переноса с триггера 7 эта единица циркулирует в динамичеоком триггере, образованном ячейками 9 и 10.

Сигнал переноса, поступивщий после четвертого импульса на вход счетчика, разрешает перепись единицы из ячейки 8 в ячейку 2 и из ячейки 9 в ячейку 5. В такт b единица из ячейки 3 переписывается в ячейку 11, дает запрет в ячейку 9 и циркулирует благодаря этому

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1973 |

|

SU385397A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Двоично-десятичный счетчик | 1977 |

|

SU702530A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Устройство для оперативного контроля в системах автоматизированного управления | 1984 |

|

SU1183986A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

Авторы

Даты

1967-01-01—Публикация