Изобретение относится к области вычислительной техники и предназначено для умножения двух чисел, представленных последовательностями имну.льсов.

Известные схемные реализации устройств умножения чисел, представленных последовательностями импульсов, основаны на предварительном нреобразозании носледовательиостей в двоичные коды с последующим умножением кодов. Если операция преобразования кодов производится без фактической затраты времени, то сам процесс умножения кодов развертывается во времени. Ускореиие производства операции умножения чисел, представленных двоичными кодами достигается за счет значительного усложнения устройства. Однако известные методы ускоренного умножения несущественно сокращают время умножения. В то же время для ряда дискретных устройств, на входы которых поступают последовательнести импульсов, время их перемножения имеет существенное значение. Сведение этого времени к минимуму зпачительио новышает возможности этих устройств.

Целью изобретения является повышение скорости умножения.

Это достигается в предложенном устройстве за счет того, что оно содержит одноразрядный сумматор, входы которого соединены с входными зажима1ми устройства, выход нереноса

сумматора соединен с одним из входов квадратора и со счетным входом двончного счетчика, а выход суммы подключен к управляющему входу группы вентилей, информационные входы которых соединены с выходами соответствующих разрядов счетчика, выходы групны вентилей соединены с другими входами квадратора.

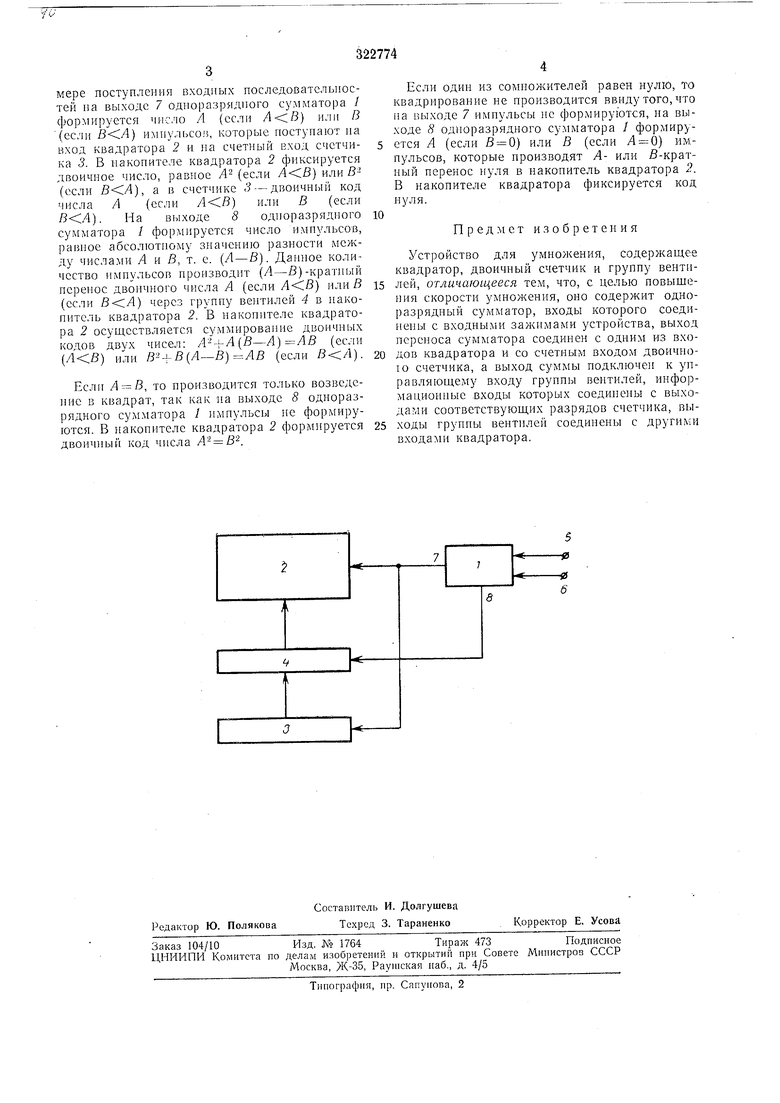

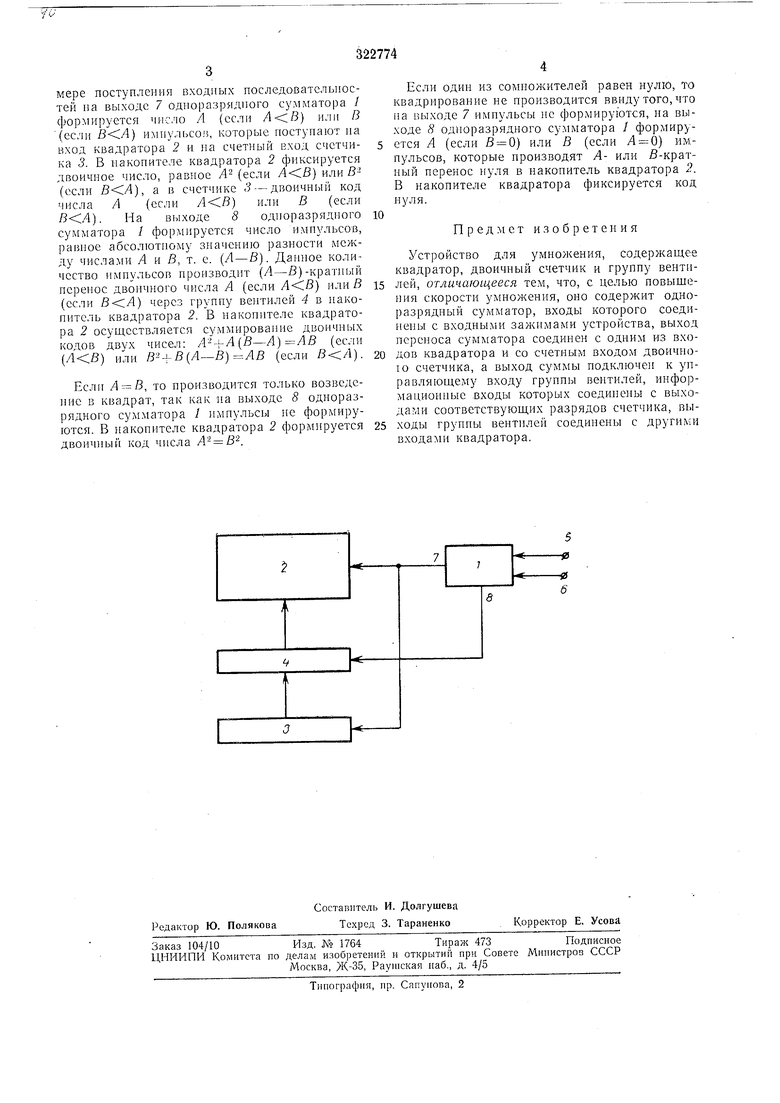

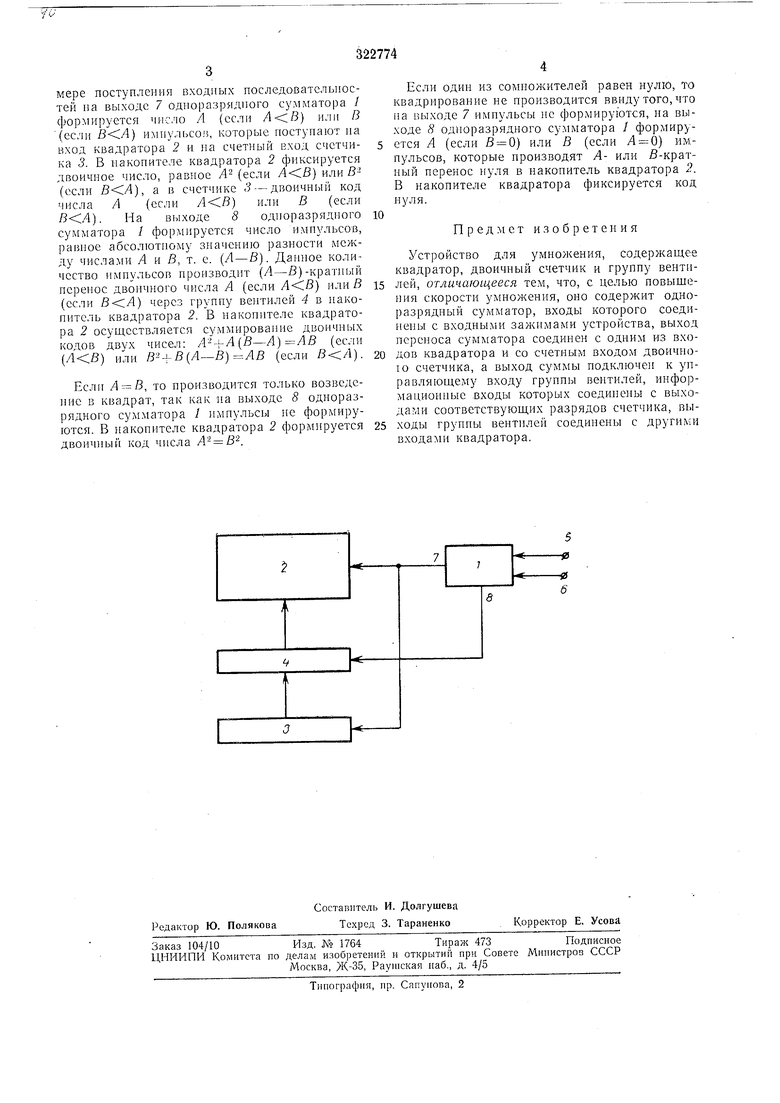

На чертеже показана 6;ioJC-cxeMa предлагаемого устройства для улиюжеиия.

Оно содержит одпораз)ядпы1 1 сумматор / на два входа, квадратор 2 чисел, иредставленН1 1Х в число-импульсном коде, /г-разрядп1,1Й двоичный счетчик 3 и -)унпу п вентилей 4. Вхсздные зажимы 5 п 6 подключены норозпь к входам одноразрядного сумматора У, выход 7 нереноса которого связан с входом квадратора 2 п со счстны.м входом счетчика 3, норазрядпо связанного со входами группы венти.чей 4. Имиульспый вход группы вентилей 4 связан с выходом 8 суммы одноразрядного суммато1)а У, а выходы группы вентилем 4 подключены к входам соответствующих разрядов накоп)ггеля квадратора 2. В исходном состоянии накона тель квадратора 2 а счетчик 3 установлешл в нуль.

Устройство работает следующим образом Иа входные зажимы 5 и 6 нодаются синхронно норозиь две последовательности пмнульсов, чнсло которых соответственно равно А и В. По

мере поступления входных последовательностей па выходе 7 одноразрядного сумматора / формируется число /1 (если ) или В (если ) имиульсо, которые поступают па вход квадратора 2 и па счетный вход счетчика 3. В накопителе квадратора 2 фнксируется двоичное число, равное Л (если )илиВ(сслн ), а в счетчике 3 - двоичный код числа Л (если ) илн В (если ). На выходе 8 одноразрядного сумматора / формируется число импульсов, равпое абсолютпому значению разпости между числами А и В, т. с. (А-В). Даиное количество импульсов производит (Л-В)-кратный перенос двоичного числа А (если ) или В (если ) через группу вентнлей 4 в накопитель квадратора 2. В накопителе квадратора 2 осуществляется суммирование двоичных кодов двух чисел: Л- + Л(5-А)АВ (если () или (Л-5)ЛВ (если ).

Если Л В, то производится только возведепис в квадрат, так как на выходе 8 одноразрядного сумматора / импульсы не формируются. В накопителе квадратора 2 формируется двоичный код числа А В,

Если один из сомножителей равен нулю, то квадрированне не производится ввиду того,что на выходе 7 имнульсы не формируются, на выходе 8 одноразрядного сумматора У формируется Л (если В 0) или В (если ) импульсов, которые производят Л- или В-кратный перенос нуля в накопитель квадратора 2. В накопителе квадратора фиксируется код нуля.

Предмет изобретения

Устройство для умножения, содержащее квадратор, двоичный счетчик и группу вент 1лей, отличающееся тем, что, с целью повышения скорости умножения, оно содержит одноразрядный еумматор, входы которого соединены с входными зажимами устройства, выход переноса сумматора соединен е одним из входов квадратора и со счетным входом двоично10 счетчика, а выход суммы подключен к управляющему входу группы вентилей, ннформационпые входы которых соединогы с выходами соответствующих разрядов счетчика, выходы группы вептплей соединены с другими входами квадратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стохастический интегратор | 1978 |

|

SU744607A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Устройство для возведения в квадрат число-импульсного кода | 1985 |

|

SU1246093A1 |

| Генератор случайных чисел | 1985 |

|

SU1302275A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1977 |

|

SU739523A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Устройство для формирования информативных признаков при распознавании изображений | 1986 |

|

SU1361591A1 |

| Адаптивный цифровой измеритель параметров сигнала | 1981 |

|

SU1013867A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Устройство для вычисления суммы квадратов К числоимпульсных величин | 1982 |

|

SU1092500A1 |

Авторы

Даты

1971-01-01—Публикация