I

Изобретение касается автоматики и цифровой вычислительной техники и может быть использовано в вычислительных машинах, системах автоматизации и в устройствах числового программного управления.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, одноразродный сумматор, первый и второй блоки двоичных эквивалентов, блок умножения, схему сравнения и выходной регистр Недостатком этого устройства является его относительно большая сложность, связанная с одновременным формированием десяти двоичных элвивалентов и определением ближайшего двоичного эквивалента.

Наиболее близким по технической сущности к предложенному является универсальный преобразователь, содержащий клю приема двоичного числа, сдвиговый регистр, элемент И/1И, коммутатор слага- емого, одноразрядный сумматор, триггер

переполнения, блок хранения двоичных эквивалентов, регистр двоично-десятичного числа, выходной регистр и счетчик десятичных разрядов, выходы которого соединены с входами регистра двоично-десятичного числа и блока хранения двоичных эквивалентов, выходы элемента И ЛИ и коммутатора слагаемого соединены с первым и вторым входами одноразрядного сумматора соответственно, информационный выход одноразрядного сумматора, соединен с входом сдвигового регистра, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом ключа приема двоичного числа, выход переполнения одноразрядного сумматора соединен с входом триггера переполнения, первый вход ключа приема двоичного числа соеданен с выходом первого разряда счетчика десятичных разрядов. Кроме то- го устройство содержит счетчик результата, блок управления и блок индикации 2

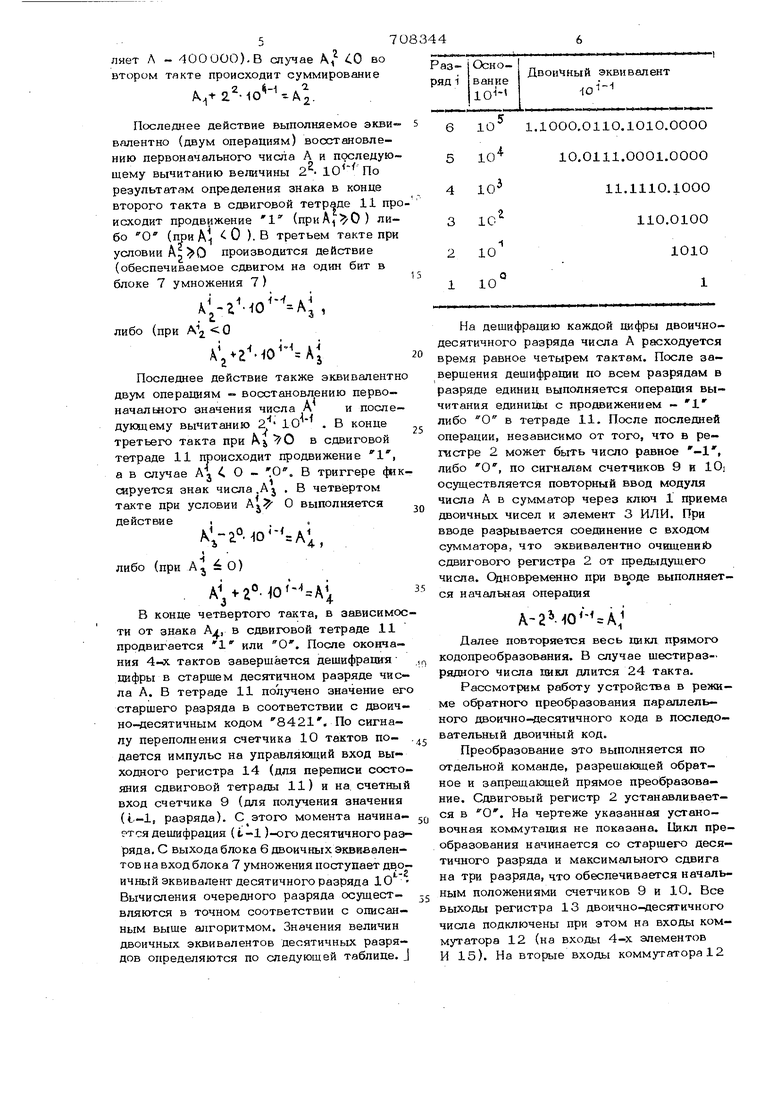

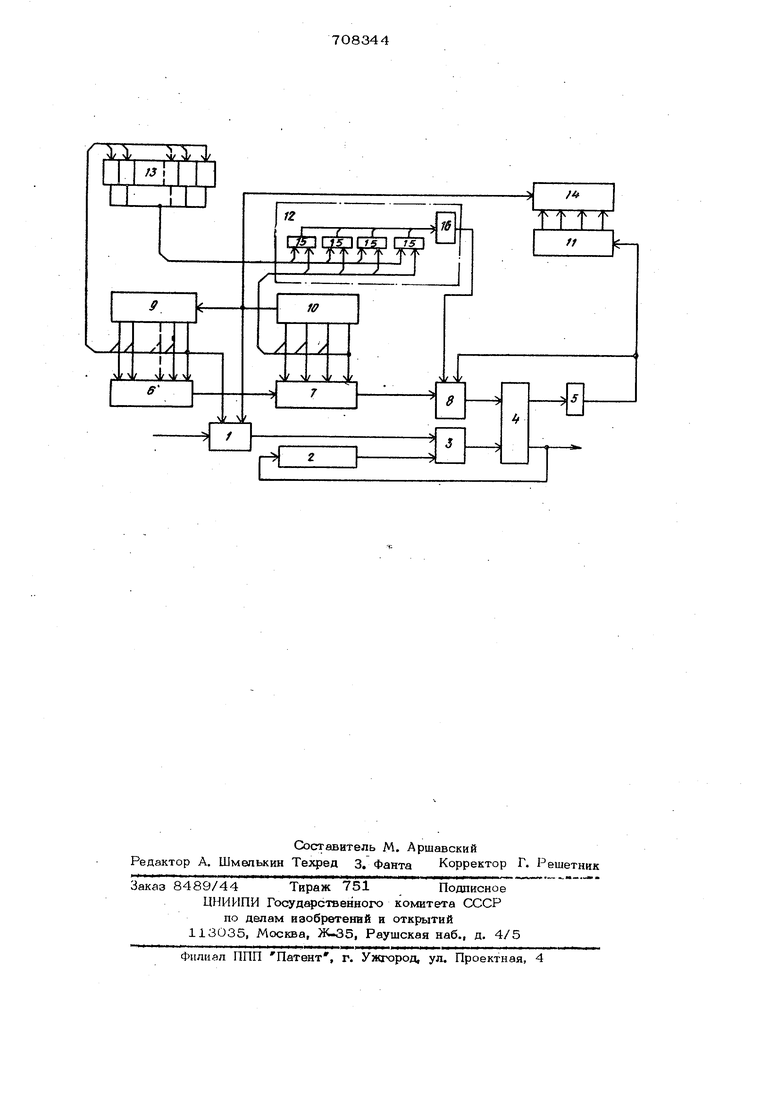

Недостатком этого преобразователя является относительно низкое быстродейст- Бие, связанное с последовательным определением значения дпоично-десятичнозх разряда, для чего может понадобиться девять операций вычитания многоразрядных чисел. Цель изобретения - повышение быстродействия работы преобразователей. Это достигается тем, что предложенны преобразователь дополШ1тельно содержит блок умножения, счетчик тактов, сдвиговую тетраду и коммутатор двоично-десятичных разрядов, первая группа входов которого соединена с выходами регистра двоично-десятичного числа, вторая группа входов - с выходами счетчика тактов и первой группой входов блока умножения, а выход - с первым входом коммутатора слагаемого, второй вход которого соединен с выходом блока умножения, а третий вход - с выходом триггера переполнения и входом сдвиговой автрады. Второй вход блока умножения соединен с выходом блока хранения двоичных эквивален тов. Выход переполнения счетчика тактов соединен с входом счетчика десятичных разрядов, управляющим входом выходного регистра и с вторым входом блока приема двоичного числа, выходы сдвиговой те трады соединены с информационными входами выходного регистра. На чертеже изображена структурная схема предложенного преобразователя. Преобразователь содержит ключ 1 приема, двоичных чисел, сдвиговый регистр 2, элемент 3 ИЛИ, одноразрядный сумматор 4, который имеет три входа, два слагаемых и перенос (не показан), триггер 5 переполнения, блок 6 хранения двоичных эквивалентов, который формирует дво ичные числа соответствукяцие значениям десятичных разрядов от до Ю , где -1 - число разрядов десятичного числа, блок 7 умножения, коммутатор 8 слагаемого, счетчик 9 десятичных разрядов, счетчик 10 тактов, сдвиговую тетраду 11 коммутатор 12 двоично-десятичных разря дов, регистр 13 двоично-десятичного числа. Выходной регистр 14. Коммутатор 12 состоит, например, из четырех элементов И 15 и элемента ИЛИ 16. . Устройство работает следующим образом. Рассмотрим сначала работу устройства в режиме прямого кодопреобразования последовательного двоичного кода в паралиельный двоично-десятичный код8421 Во внешних регистрах числа представленкт В дополнительном коде. В преобразователь вводится модуль числа А, знак которого определяется отдельным блоком и на работу преобразователя не влияет. Ввод числа производится в начальный момент, который фиксируется переполнением в счетчике тактов 10 и начальным состоянием в счетчике десятичных разрядов 9. Через элемент 3 ИЛИ в такте ввода-исходное двоичное число поступает на вход одноразрядного сумматора 4, После завершения ввода во всех дальнейших тактах преобразования на вход сумматора 4 через элемент 3 ИЛИ поступают числа с выхода сдвигового регистра 2. Преобразование производится последовательно, начиная с ЦИФР старшего разряда. В такте ввода одновременно осуществляется алгебрическое вычитание из вводимого числа двоичнодесятичного эквивалента десятичного разряда Ю . Для получения соответствующих двоично-десятичных эквивалентов производятся сдвиги влево (так как числа в регистре 2 идут младшими разрядами вперед) двоичных чисел 1О . Каждый из сдвигов фиксируется счетчиком 10 тактов, который управляет разрядными сдвигами в блоке 7 умножения. При начальном состоянии счетчика 10 блок 7 умножения реализует сдвиг на три разряда, что соответствует умножению на 8. Таким образом, при вводе от модуля числа А вычитается число 10 2 (для шестиразрядного числа это составляет А-8ООООО). Резульлгат Вычитания после окончания начального такта ввода записывается в регистр 2. Здесь и далее промежуточные значения чисел в регистре 2 обозначаются с индексом десятичного разряда и номера такта, следующим образом А-2 10 ,где Я - номер такта. Одновременно с определением числового значения разности в конце 1-го такта происходит определение знака разности А 0„ Если Л ;Q,To подается соответствующий сягвал выхода триггера 5 на вход коммутатора слагаемого 8, а в сдвиговую тетраду 11 записывается единица. Если , то отрицательный знак разности фиксируется во втором логическом блоке 8, а в сдвиговую тетраду засылается Q. Во втором такте при условии О происходит следующее вычитание от результата хран5 шегося в регистре 2 А,г о-и; (для щестиразрядного числа это составляет Л - 4000ОО).В случае k 0 во втором такте происходит суммирование . Последнее действие выполняемое экви- валентно (двум операциям) восстановлению первоначального числа А и последующему вычитанию величины 2 По результатам определения знака в конце второго такта в сдвиговой тетраде 11 про исходит продвижение 1 () либо О (при А О ). В третьем такте при условии Ар производится действие (обеспечиваемое сдвигом на один бит в блоке 7 умножения 7) (оНА;, либо (при А2 0 .оКА; Последнее действие также эквивалентн двум операциям - восстановлению первоначального значения числа А дующему вычитанию 2 10 третьего такта при А О в сдвиговой тетраде 11 происходит продвижение 1, а в случае Aj 4 О - О. В триггере фик сируется знак числа.АJ , В четвёртом такте при условии Aj О выполняется действие Al-i., либо (при А 0) . VJ -a° o- Ai в конце четвертого такта, в зависимос ти от знака А, в сдвиговой тетраде 11 продвигается I или О. После окончания 4-л тактов завершается дешифрация цифры в старшем десятичном разряде числа А. В тетраде 11 получено значение ег старшего разряда в соответствии с двоично-десятичным кодом 8421. По сигналу переполнения счетчика 10 тактов подается импульс на управлякяций вход выходного регистра 14 (для переписи состо яния сдвиговой тетрады 11) и на. счетный вход счетчика 9 (для получения значения (t-1, разряда). С этого момента начинартся дешифрация (ь-1 )-ого десятичного разряда. С выхода блока 6 двоичных эквивалентов на вход блока 7 умножения поступает двоичный эквивалент десятичного разряда Вычисления очередного разряда осуществляются в точном соответствии с описанным выше Ш1ГОРИТМОМ. Значения величин двоичных эквивалентов десятичных разрядов определяются по следующей таблице. J 7 и после- 4 На дешифрацию каждой 1шфры двоичнодесятичного разряда числа А расходуется время равное четырем тактам. После завершения дешифрации по всем разрядам в разряде единиц выполняется операшя вычитания единицы с пpo шижeниeм - I либо О в тетраде 11. После последней операции, независимо от того, что в регистре 2 может быть число равное -1, либо О, по сигналам счетчиков 9 и 10; осуществляется повторный ввод модуля числа А в сумматор через ключ 1 приема двоичных чисел и элемент 3 ИЛИ. При вводе разрывается соединение с входом сумматора, что эквивалентно очищений сдвигового регистра 2 от предыдущего числа. Одновременно при выполняется начальная операция Далее повторяе11ся весь цикл прямого кодопреобразования. В случае шестиразРЯДНОГО числа хшвл длится 24 такта. Рассмотрим работу устройства в режиме обратного преобразования параллельного двоично-десятичного кода в последовательный двоичный код. Преобразование это выполняется по отдельной команде, разрешакяцей обратное и запрещающей прямое преобразование. Сдвиговый регистр 2 устанавливается в О. На чертеже указанная установочная коммутахщя не показана. Шкл преобразования начинается со старшего десятичного разряда и максимального сдвига на три разряда, что обеспечивается начальным положениями счетчиков 9 и 10. Все Выходы регистра 13 двоично-десятичного числа подключены при этом на входы коммутатора 12 (на входы 4-х элементов И 15). На вторые входы коммутатора 12 .7 (на входы аяементов И 15) последовательно подаются единичные выходы разрядов счетчика тактов. Выходы всех элемен тов И 15 через элемент ИЛИ 16 управля ют работой коммутатора 8 слагаемого, разрешая либо запрещая прохождение соответствующих значений двоичных эквивалентов на сумматор 4. Если в очередном такте, например начальном, когда в блоке умножения 7 реализуется сдвиг на три разряда, а на выходе коммутатора 12 имеется единичный сигнал, то на вход сумматора проходит число 2 10 с выхода сумматора 4, которое накапливает ся в регистре 2. Если же с элемента ИЛИ 16 поступает нулевой сигнал, то коммута тор 8 не пропускает двоичный эквивалент числа 2 на вход сумматора 4. Цикл обратного преобразования так же вы полняется за 4 такта. Поступающее с.ре- гвсягра 13 число А(о) в двоично-десятичном коде накапливается в регистре 2 в двоичном коде А По завершении цикла преобразования результат с выхода сумматора 4 передается в выходной регистр. С выходного регистра число ) при необ ходамости передается на вход ключа 1 приема для выполнения прямого преобразования. Предложенный преобразователь требует четырех .тактов для получения одного двоично-десятичного разряда. При преобра зованав шестиразрядных десятичных чисел предложенное устройство работает в три раза быстрее (24 такта вместо 72) чем известный преобразователь (прототип). Формула изобретения Преобразователь двоичного кода в двоичво-4}есятичный и обратно, содержащий ключ приема двоичного числа, сдвиговый регистр, элемент ИЛИ, коммутатор слагаемого, одноразрядный сумматор, триггер переполнш1ия, блок хранения двоичных эквивалентов, регистр двоично-десятичного числа, выходной регистр и счетчик десятичных разрядов, выходы которого сое448динены с входами регистра двоично есятичного числа и блока хранения двоичных эквивалентов, выходы элемента ИЛИ и коммутатора слагаемого соединены с первым и вторым входами одноразрядного сумматора соответственно, информационный выход одноразрядного сумматора соединен с входом сдвигового регистра, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен., с выходом ключа приема двоичного числа, выход переполнения одноразрядного сумматора соединен с входом триггера переполнения, первый вход ключа приема двоичного числа соединен с выходом первого разряда счетчика десятичных разрядов, отличающийс я тем, что, с целью повышения быстродействия преобразователя, он дополнительно содержит блок умножения, счетчик тактов, сдвиговую тетраду и коммутатор двоично-десятичных разрядов, первая группа входов которО1Ю соединена с выходами регистра двоично..десятичного числа, вторая группа входов - с выходами счетчика тактов и первой группой входов блока умножения, а выход - с первым входом коммутатора слагаемого второй вход которого соединен с выходом блока умножения, а третий вход - с выходом триггера переполнения и входом сдвиговой тетрады, второй вход блока умножения соединен с Выходом блоха хранения двоичных эквивалентов, выход переполнения счетчика тактов соединен с входом счетчика десятичных разрядов, управляющим входом выходного регистра и с вторым входом блока приема двоичного числа, выходы сдвиговой тетрады соединены с информашонными входами выходного регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР М 473173, кл. Q 06 F 5/02, 1973. 2.Песчанский Б. И. и др. Устройства цифровой индикации перемещений в АСПУ В сб. Агрегатное построение унифиодрованных систем программного управления машинами. М., Наука, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1977 |

|

SU739523A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

Авторы

Даты

1980-01-05—Публикация

1975-04-10—Подача