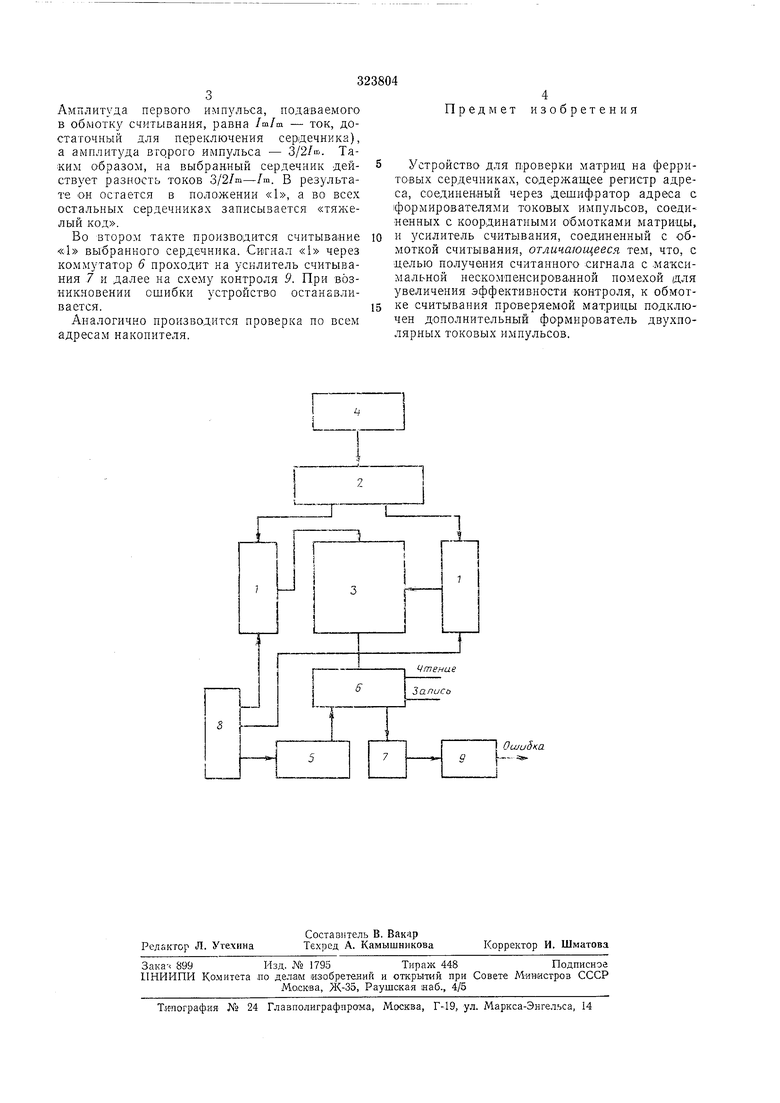

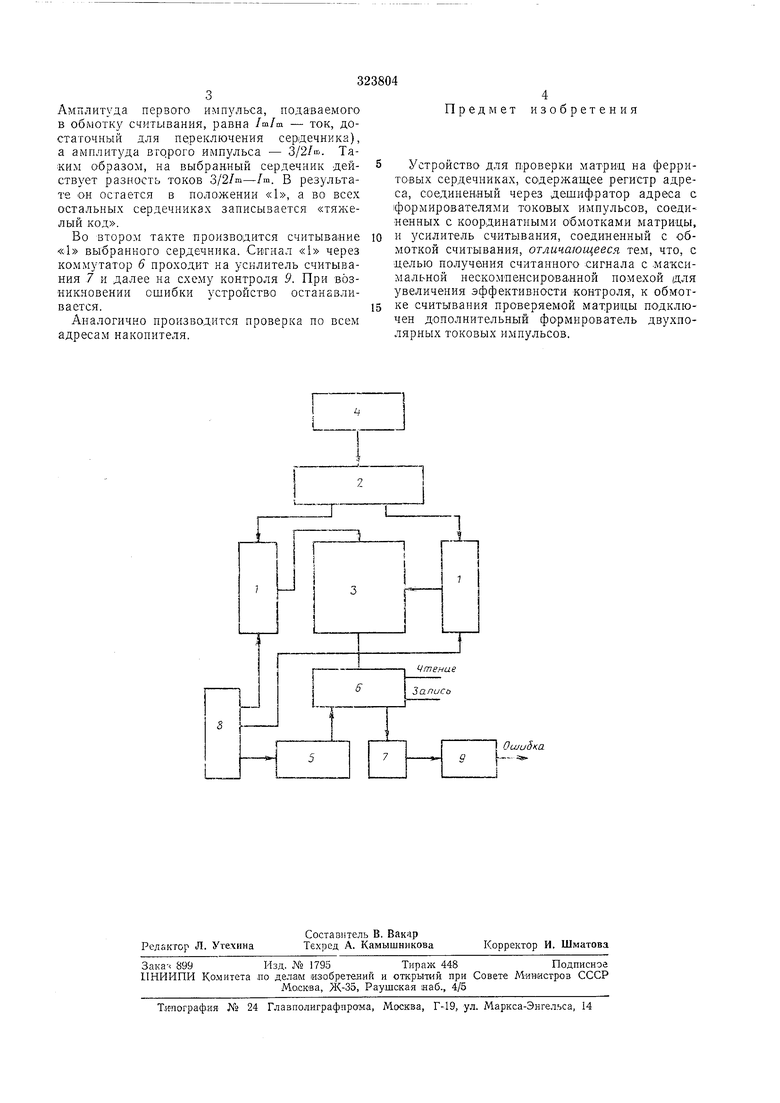

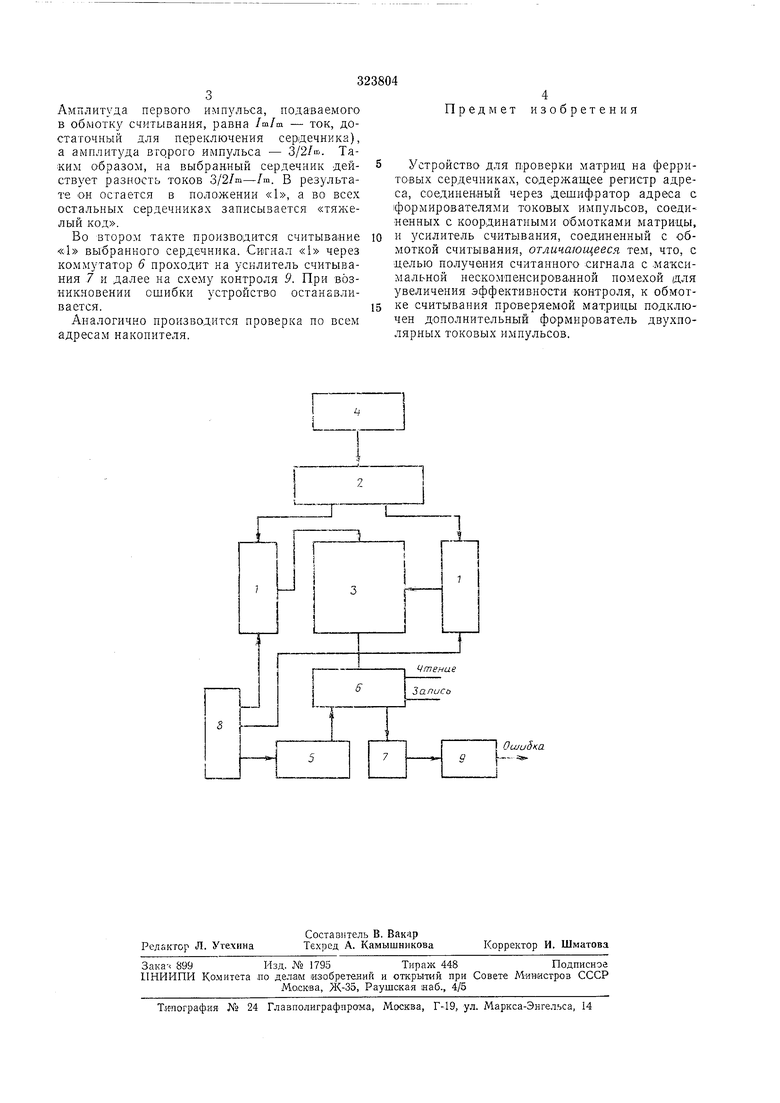

Предлагаемое устройство может быть лспользовано для проверки ферритовых матриц накопителя. Известны устройства, осуществляющие проверку матриц при помощи «тяжелого кода. ЗапИСЬ «тяжелого кода в них производится либо поадресно через специальные логические схгмы, либо подачей в провод считывания проверяемой матрицы тока, достаточного для перемагничивания сердечников. Однако эти устройства не обеспечивают достаточной эффективности контроля, так как осуществляют проверку ферритовых матриц при помощи обычного теста «тяжелый код. При этом полярность импульса суммарной помехи совпадает с полярностью сигнала считанной «I, т. е. с увеличением помехи при считывании имеет место увеличения сигнала. Цель изобретения - обеспечить наибольшую эффективность контроля матриц на ферритоеых сердечниках при помощи «тяжелого кода, в котором по одному из адресов вместо «О записывается «1, и при считывании инфор1маци.и по этому адресу суммарная помеха вычитается из сигнала «1, образуя, таким образом, наименьшую считанную «1. ряемой матрицы, работающего одновременно с формирователями выборки. Схема устройства приведена на чертеже. Формирователи 1, управляемые дешифраторами 2, соединены с координатными обмотками проверяемой матрицы 5 и служат для подачи полутоков «чтения и «записи согласно адресу, установленному в регистре адреса 4. Формирователь 5 соединен с обмоткой считывания матрицы через коммутатор 6, отключающий при записи усилитель считывания 7, и предназначен для подачи в матрицу двухполярных токовых импульсов. Полярность этих импульсов выбирается в зависимости от адреса схемой управления 8, которая обеспечивает также синхронность работы элементов устройства. Схема контроля 9 устройства останавливает устройство для возникновения ошибки. Работа устройства для каледого адреса осуществляется в два такта. В первом такте в проверяемую матрицу записывается «тяжелый код. Для этого по адресу, установленному в регистре адреса 4, в соответствующие координатные обмотки матрицы 3 из формирователей / подаются полутоки «чтение и «запись и одновременно из формирователя 5 подаются два разнополярных токовых импульса, полярность которых выбирается схемой управления 8 таким образом, чтобы скомпенсировать ток считывания.

Амплитуда первого импульса, подаваемого в обмотку считывания, равна /m/m - ток, достаточный для переключения сердечника), а амплитуда вто.рого импульса - 3/2/ш. Таким Образом, на выбранный сердечник действует разность токов З/2/m-/ш. В результате ОН остается в положении «1, а во всех остальных сердечниках записывается «тяжелый код.

Во втором такте производится считываиие «1 выбранного сердечника. Ситнал «1 через коммутатор 6 проходит на усилитель считывания 7 и далее на схему контроля 9. При возникновении ошибки устройство останавливается.

Аналогично производится проверка по всем адресам накопителя.

Предмет изобретения

Устройство для проверки матриц на ферритовых сердечниках, содержащее регистр адреса, соединенный через дешифратор адреса с |формирователями токовых импульсов, соеди ненных с координатными обмотками матрицы, и усилитель считывания, соединенный с обмоткой считывания, отличающееся тем, что, с целью получения считанного сигнала с .максимальной нескомпенсированной помехой для увеличения эффективности контроля, к обмотке считывания проверяемой матрицы подключен дополнительный фо-рмирователь двухполярных токовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРОВЕРКИ МАТРИЦ НА ФЕРРИТОВЫХ СЕРДЕЧНИКАХ | 1971 |

|

SU318998A1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU658601A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Устройство для обучения записи информации в память ЭВМ | 1983 |

|

SU1153340A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройсто для проверки ферритовых матриц | 1974 |

|

SU548893A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ БЫСТРОДЕЙСТВУЮЩЕЙ МНОГОСИМВОЛЬНОЙ МНОГОРАЗРЯДНОЙ ПЕЧАТЬЮ | 1965 |

|

SU172133A1 |

I Оши5к.а. L- зя

Авторы

Даты

1972-01-01—Публикация