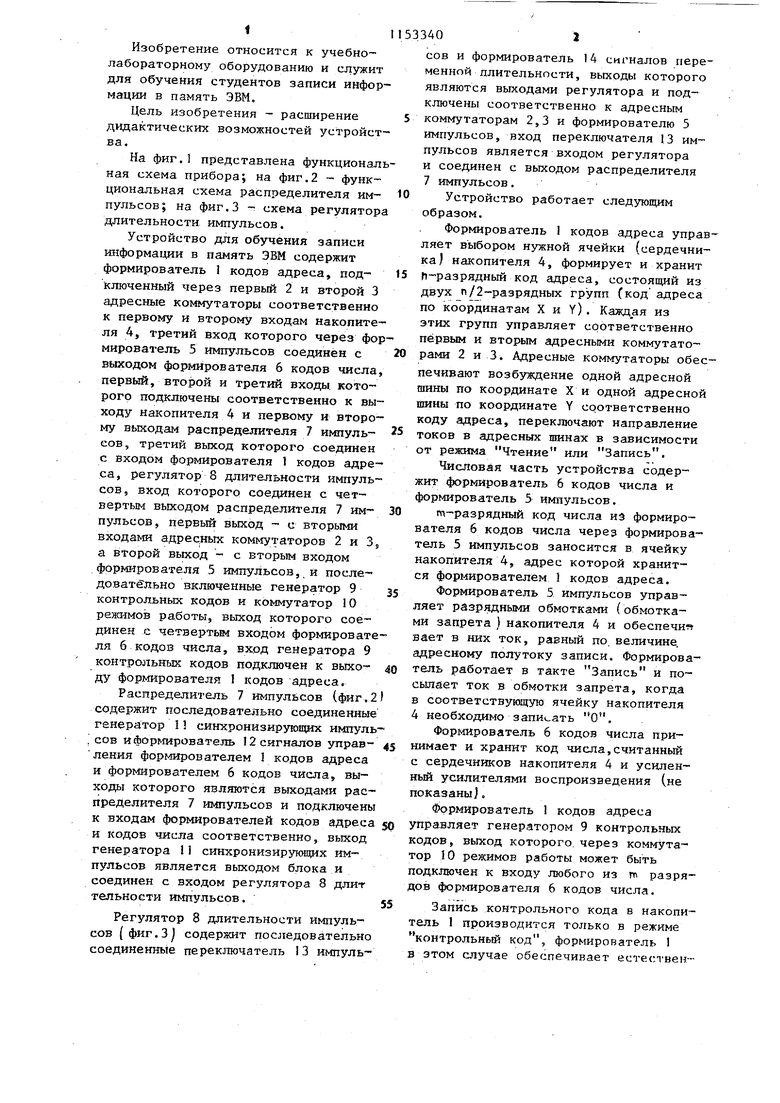

Изобретение относится к учебнолабораторному оборудованию и служит для обучения студентов записи информации в память ЭВМ. Цель изобретения - расширение дидактических возможностей устройства. На фиг.1 представлена функциональ ная схема прибора; на фиг.2 - функциональная схема распределителя импульсов; на фиг.З - схема регулятора длительности импульсов. Устройство для обучения записи информации в память ЭВМ содержит формирователь 1 кодов адреса, подключенный через первый 2 и второй 3 адресные коммутаторы соответственно к первому и второму входам накопителя 4, третий вход которого через фор мирователь 5 импульсов соединен с выходом формирователя 6 кодов числа, первый, второй и третий входы, которого подключены соответственно к выходу накопителя 4 и первому и второму выходам распределителя 7 импульсов, третий выход которого соединен с входом формирователя 1 кодов адреса, регулятор 8 длительности импульсов, вход которого соединен с четвертым выходом распределителя 7 импульсов, первый выход - с вторыми входами адрес.ных коммутаторов 2 и 3, а второй выход - с вторым входом формнрователя 5 импульсов,, и последовательно включенные генератор 9 контрольных Кодов и коммутатор 10 режимов работы, выход которого соединен с четвертьи входом формировате ля б кодов числа, вход генератора 9 контрольных кодов подключен к выходу формирователя кодов адреса. Распределитель 7 импульсов (фиг.2 содержит последовательно соединенные генератор I1 синхронизирующих импуль , сов и формирователь 12 сигналов управления формирователем 1 кодов адреса и формирователем 6 кодов числа, выходы которого являются выходами распределителя 7 импульсов и подключены к входам формирователей кодов адреса 59

и кодов числа соответственно, выход генератора II синхронизируннцих импульсов является выходом блока и соединен с входом регулятора 8 длит тельности ш-тульсов.

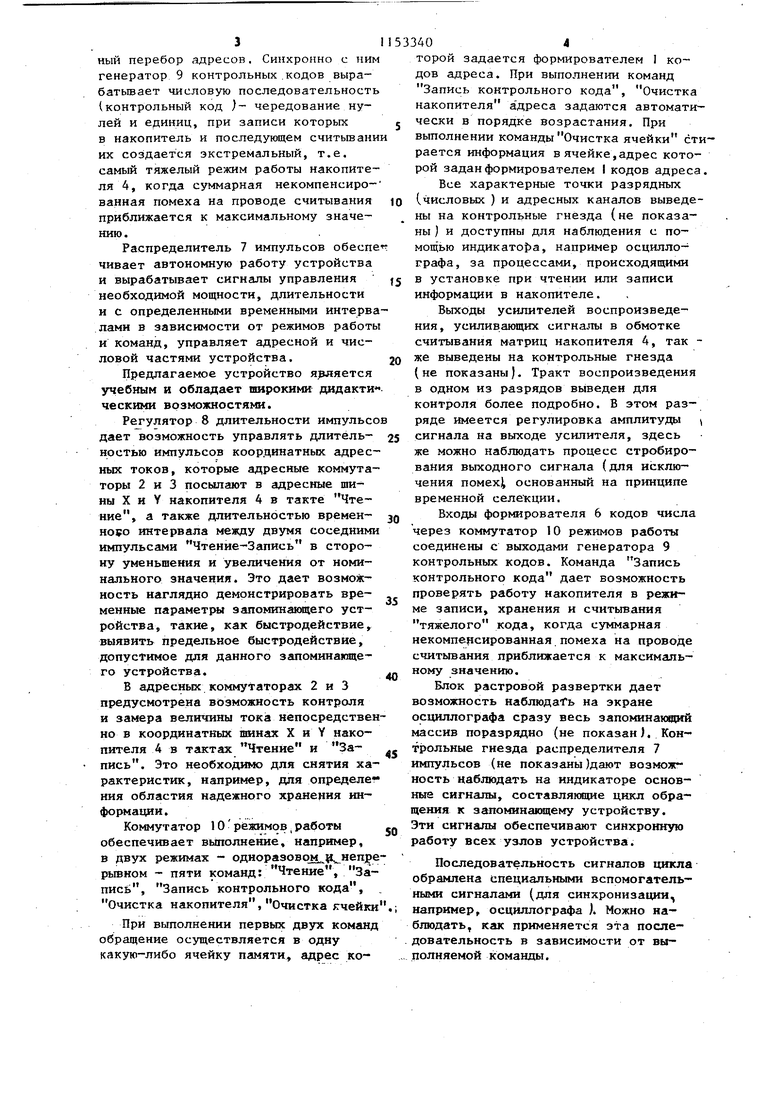

Регулятор 8 длительности импульсов (фиг.З содержит последовательно соединенные переключатель 3 импулькодов, выход которого, через коммутатор 0 режимов работы может быть подключен к входу любого из гг разрядов формирователя 6 кодов числа.

Запись контрольного кода в накопитель 1 производится только в режиме контрольный код, формирователь 1 в этом случае обеспечивает естествен- 402 сов и формирователь 14 сигналов переменной длительности, выходы которого являются выходами регулятора и подключены соответственно к адресным коммутаторам 2,3 и формирователю 5 импульсов, вход переключателя 13 импульсов является входом регулятора и соединен с выходом распределителя 7 импульсов. Устройство работает следующим образом. Формирователь 1 кодов адреса управляет выбором нужной ячейки (сердечника) накопителя 4, формирует и хранит fi-разрядный код адреса, состоящий из двух п/ 2-разрядных групп (код адреса по координатам X и Y) . Кажд.ая из этих групп управляет соответственно первым и вторым адресными коммутаторами 2 и 3. Адресные коммутаторы обеспечивают возбуждение одной адресной шины по координате X и одной адресной шины по координате У срответственно коду адреса, переключают направление токов в адресных шинах в зависимости от режима Чтение или Запись. Числовая часть устройства содержит формирователь 6 кодов числа и формирователь 5 импульсов. т-разрядный код числа из формирователя 6 кодов числа через формирователь 5 импульсов заносится в ячейку накопителя 4, адрес которой хранится формирователем 1 кодов адреса. Формирователь 5 импульсов управляет разрядными обмотками (обмотками запрета ) накопителя 4 и обеспечив вает в них ток, равньш по. величине, адресному полутоку записи. Формирователь работает в такте Запись и посьшает ток в обмотки запрета, когда в соответствукйцую ячейку накопителя 4 необходимо записать О. Формирователь 6 кодов числа принимает и хранит код числа,считанный с сердечников накопителя 4 и усиленный усилителями воспроизведения (не показаны). Формирователь 1 кодов адреса управляет генератором 9 контрольных ный перебор адресов. Синхронно с ним генератор 9 контрольных.кодов выра- батьшает числовую последовательность (контрольный код )- чередование нулей и единиц, при записи которых в накопитель и последующем считьшани их создается экстремальный, т.е. самый тяжелый режим работы накопителя 4, когда суммарная некомпенсированная помеха на проводе считывания приближается к максимальному значению. Распределитель 7 импульсов обеспе чивает автономную работу устройства и вырабатывает сигналы управления необходимой мощности, длительности и с определенными временными интерва лами в зависимости от режимов работы и команд, управляет адресной и числовой частями устройства. Предлагаемое устройство является учебным и обладает широкими дидакти ческими возможностями. Регулятор 8 длительности импульсо дает возможность управлять длитёльностью импульсов координатных адресных токов, которые адресные коммутаторы 2 и 3 посылают в адресные шины X и Y накопителя 4 в такте Чтение, а также длительностью временного интервала между двумя соседними импульсами Чтение-Запись в сторону уменьшения и увеличения от номинального значения. Это дает возможность наглядно демонстрировать временные параметры запоминакяцего устройства, такие, как быстродействие, выявить предельное быстродействие, допустимое для данного запоминающего устройства. В адресных коммутаторах 2 и 3 предусмотрена возможность контроля и замера величины тока непосредствен но в координатных шииах X и Y накопителя 4 в тактах Чтение и Запись. Это необходимо для снятия характеристик, например, для определен ния областия надежного хранения информации. Коммутатор 10режимов,работы обеспечивает выполнение, например, в двух режимах - одноразовом„ 1 неп ре рьгоном - пяти команд: Чтение, Запись, Запись контрольного кода, Очистка накопителя, Очистка гчейки При выполнении первых двух команд обращение осуществляется в одну какую-либо ячейку памяти, адрес которой задается формирователей I кодов адреса. При выполнении команд Запись контрольного кода, Очистка накопителя адреса задаются автоматически в порядке возрастания. При выполнении команды Очистка ячейки стирается информация в ячейке,адрес которой задан формирователем I кодов адреса. Все характерные точки разрядных (числовых ) и адресных каналов выведены на контрольные гнезда (не показаны ) и доступны для наблюдения с помощью индикато{)а, например осциллографа, за процессами, происходящими в установке при чтении или записи информации в накопителе. Выходы усилителей воспроизведения, усиливающих сигналы в обмотке считывания матриц накопителя 4, так же выведены на контрольные гнезда (не показаны). Тракт воспроизведения в одном из разрядов выведен для контроля более подробно. В этом разряде имеется регулировка амплитуда ( сигнала на выходе усилителя, здесь же можно наблюдать процесс стробирования выходного сигнала (для исключения помех основанный на принципе временной селекции. Входы формирователя 6 кодов числа через коммутатор 10 режимов работы соединены с выходами генератора 9 контрольных кодов. Команда Запись контрольного кода дает возможность проверять работу накопителя в режиме записи, хранения и считывания тяжелого кода, когда суммарная некомперсированная помеха на проводе считывания приближается к максимальному значению. Блок растровой разверткн дает возможность наблюдать на экране осциллографа сразу весь запоминающий массив поразрядно (не показан). Контрольные гнезда распределителя 7 импульсов (не показаны )дают возмож ность наблюдать на индикаторе основные сигналы, составляняцие цикл обращения к запоминающему устройству. Эти сигналы обеспечивают синхронную работу всех узлов устройства. Последовательность сигналов цикла обрамлена специальными вспомогательными сигналами (для синхронизации, например, осциллографа ). Можно наблюдать, как применяется эта последовательность в зависимости от выполняемой команды.

Г

}Н&1.6

. 2

в

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Устройство для отображения информации | 1987 |

|

SU1571646A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Запоминающее устройство | 1975 |

|

SU639016A1 |

УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ЗАПИСИ ИНФОРМАЦИИ-В ПАМЯТЬ ЭВМ, содержащее формирователь кодов адреса, подключенный через.первый и второй адресные коммутаторы соответственно к первому и второму входам накопителя, т-ретий вход которого через формирователь импульсов Соединен с выходом формирователя кодов числа. первый, второй и третий входы которого подключены соответственно к выходу накопителя и первому и второму выходам распределителя импульсов, третий выход которого соединен с входом формирователя кодов адреса, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены регулятор длительности импульсов, вход которого соединен с четвертым выходом распределителя импульсов, первый выход - с вторыми входами . адресных коммутаторов, а второй выход - с вторым входом формирователя импульсов, и последовательно включенные генератор контрольных кодов и коммутатор режимов работы, выход которого соединен с четвертым входом формирювателя кодов числа, вход генератора контрольных кодов подключен к выходу формирователя кодов адреса.

I

иа. 3

| Запоминающее устройство | 1973 |

|

SU444239A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОФШД | 1973 |

|

SU429466A1 |

Авторы

Даты

1985-04-30—Публикация

1983-12-15—Подача