Изобретение относится к вычислительной технике, может быть использовано для управления обменом информацией между устройством ввода-вывода и процессором и является усовершенствованием известного селекторного канала по авт.св. № 1103218.

Целью изобретения является повышение быстродействия канала.

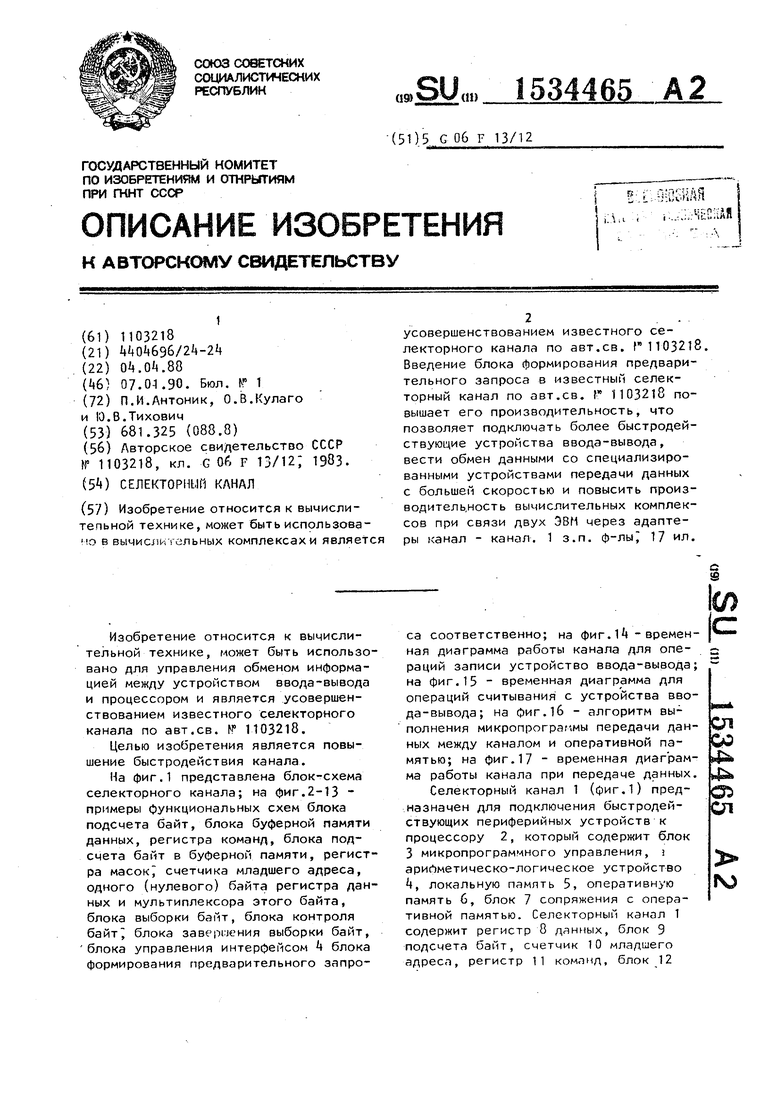

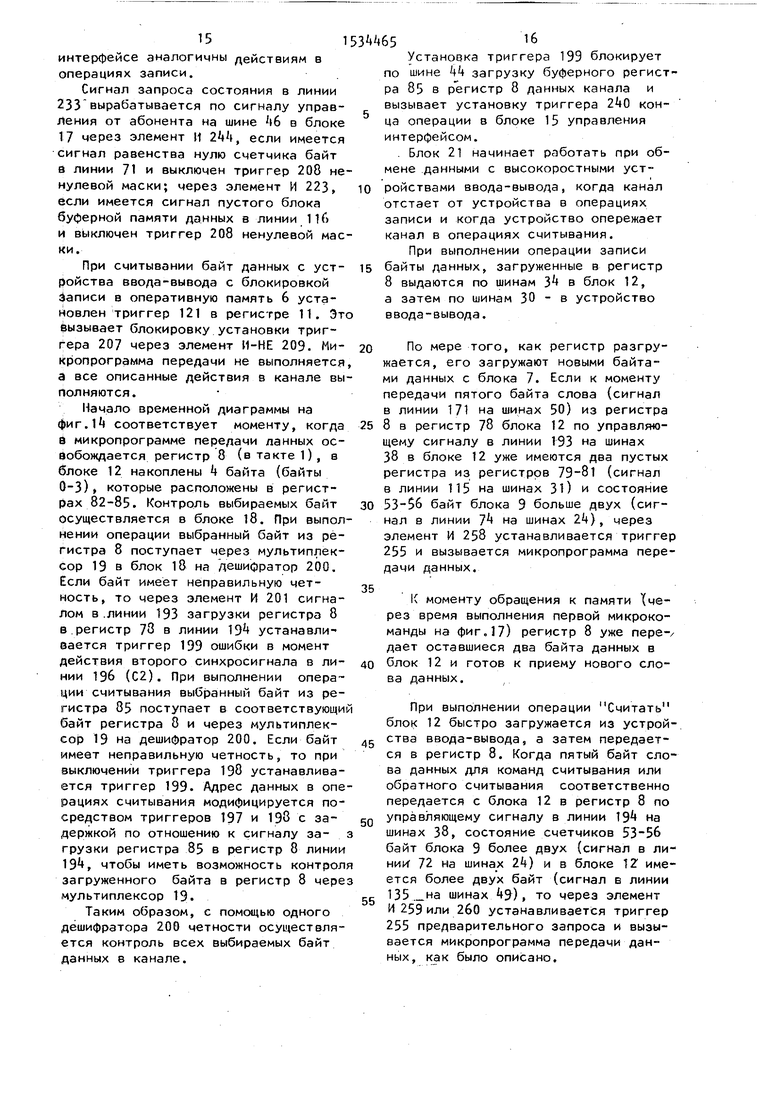

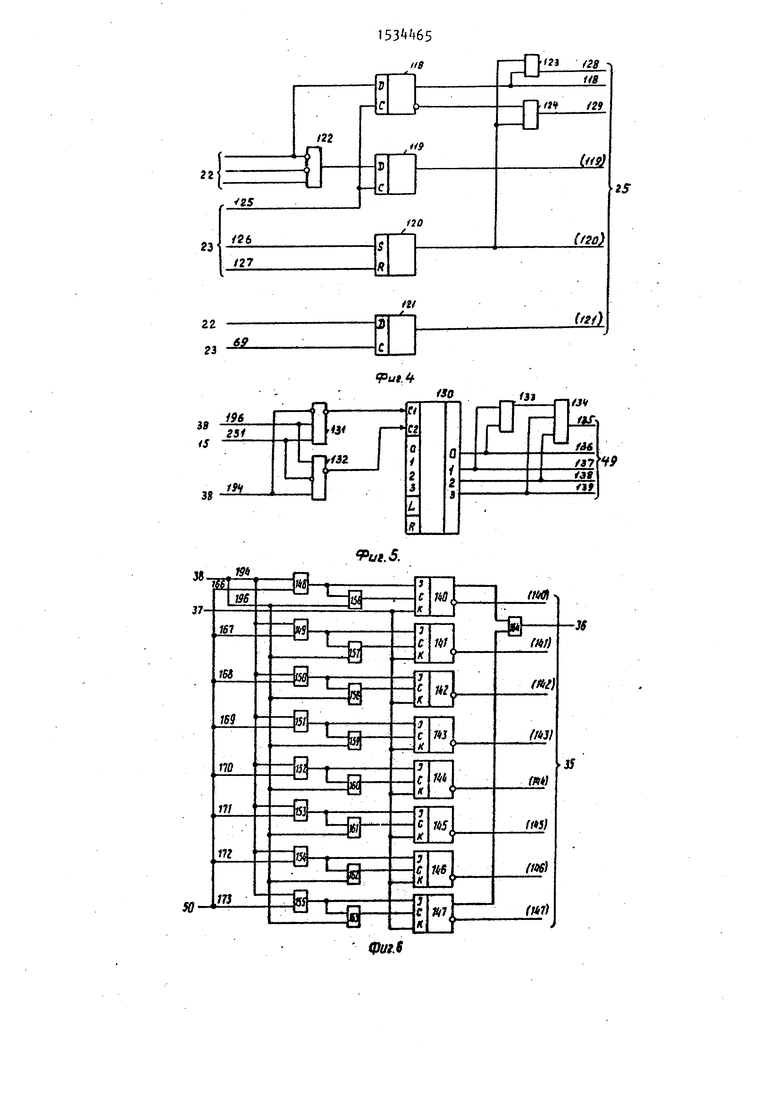

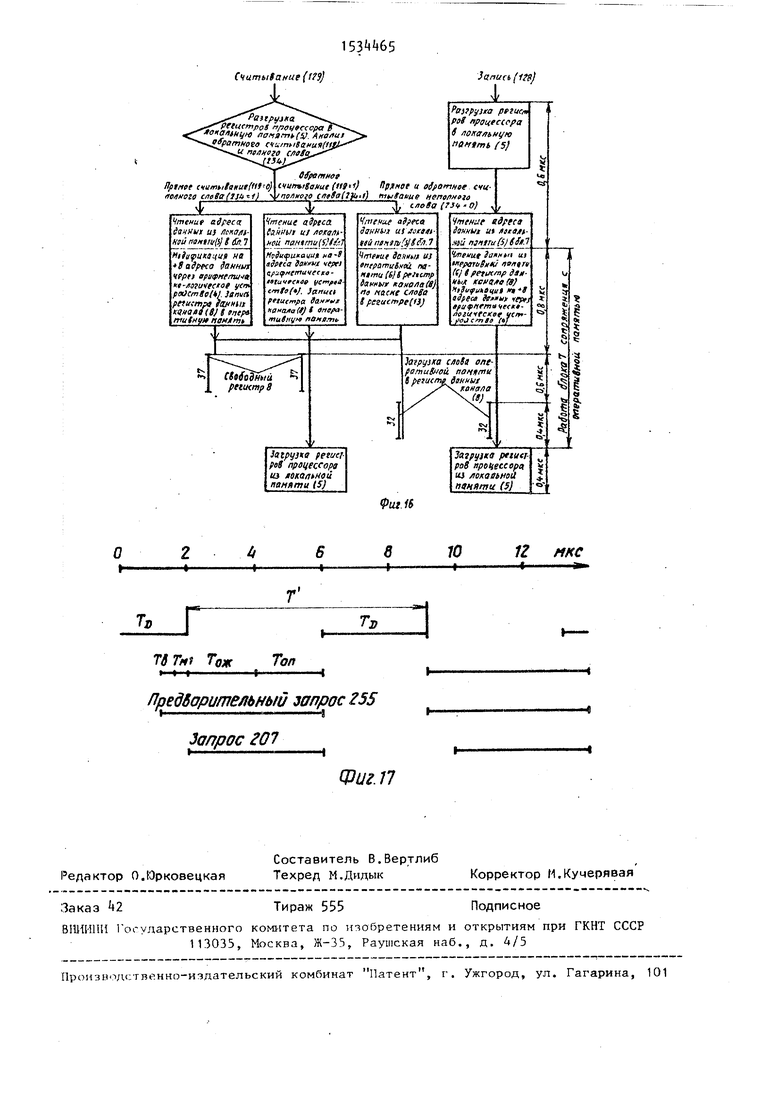

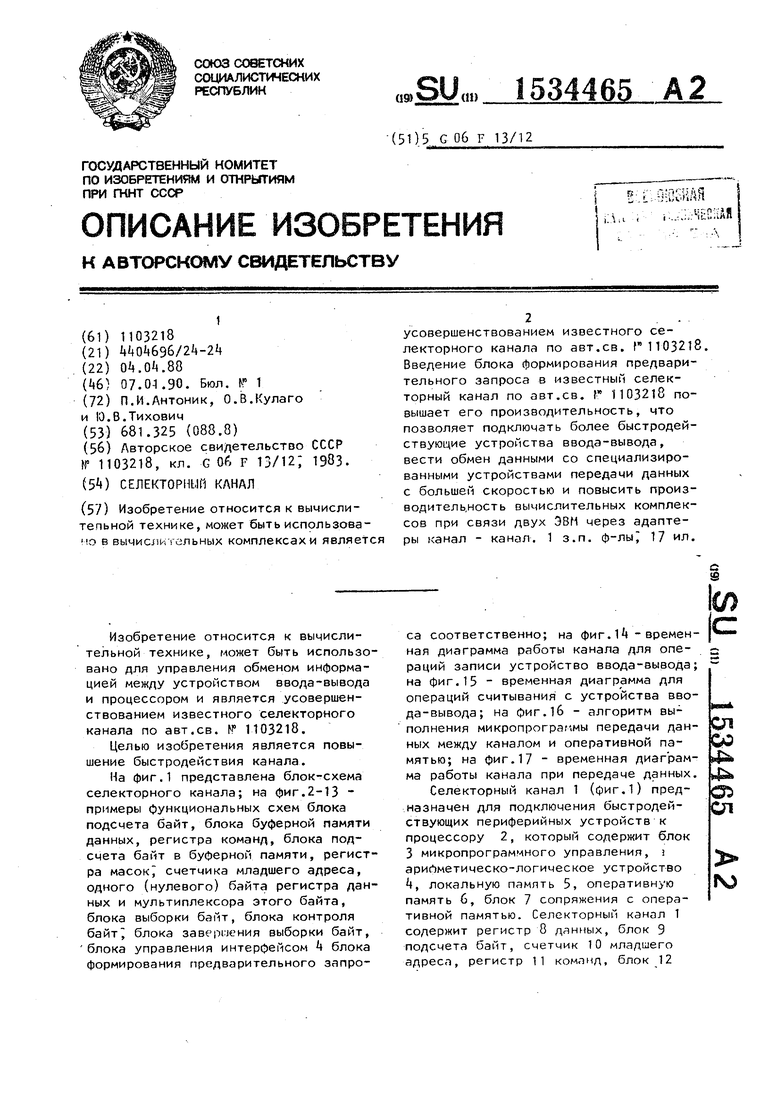

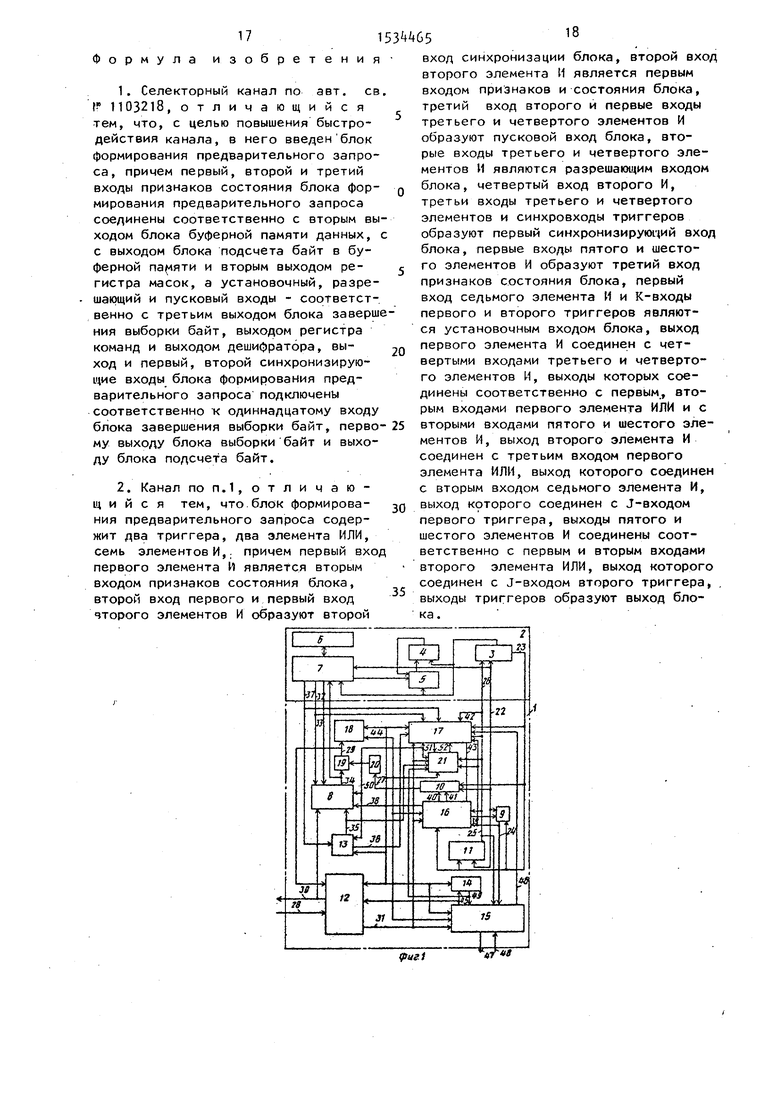

На фиг.1 представлена блок-схема селекторного канала; на фиг.2-13 - примеры функциональных схем блока подсчета байт, блока буферной памяти данных, регистра команд, блока подсчета байт в буферной памяти, регистра масок счетчика младшего адреса, одного (нулевого) байта регистра данных и мультиплексора этого байта, блока выборки байт, блока контроля байт; блока завсриения выборки байт, блока управления интерфейсом блока формирования предварительного запроса соответственно; на фиг. -временная диаграмма работы канала для операций записи устройство ввода-вывода; на фиг.15 временная диаграмма для операций считывания с устройства ввода-вывода; на фиг.1б - алгоритм выполнения микропрограммы передачи данных между каналом и оперативной памятью; на фиг.17 - временная диаграмма работы канала при передаче данных.

Селекторный канал 1 (фиг.1) предназначен для подключения быстродействующих периферийных устройств к процессору 2, который содержит блок 3 микропрограммного управления, i ариЛметическо-логическое устройство k, локальную память 5, оперативную память 6, блок 7 сопряжения с оперативной памятью. Селекторный канал 1 содержит регистр 8 данных, блок 9 подсчета байт, счетчик 10 млддиего адреса, регистр 11 команд, блок 12

(/

cz

ел

00 Јъ Јь ОЭ

сп

го

31

буферной памяти данных, регистр 13 масок, блок И подсчета бант буферной памяти, блок 15 управления интерфейсом, блок 16 выборки байт, блок 1 завершения выборки байт, блок 18 контроля байт, мультиплексор 19, i дешифратор 20, блок 21 формирования предварительного запроса, шины 22 и 23 второго и первого входов канала 1, шины 2k и 25 выходо блока Э и регистра 11, шины 26 первого выхода канала 1, шины 27 счетчика шины 23 четвертого входа канала 1, шины 29 выхода мультиплексора 19, шины 30 третьего выхода канала 1 , шины 31 второго выхода блока 12, шин 32-3 шестого и третьего входов и второго выхода канала 1, шина 35 и 3 второго и первого выходов регистра 13, шины 37 седьмого входа канала 1, шины ЗЗ- первого -.четвертого выходов блока 16, шины 2 и +3 выходов блока 17, шины М выхода блока 18, шины 5 и U6 второго и третьего вы- ходов блока 15 , шины k7 и 8 четвертого выхода и пятого входа канала 1, шины Й9 выхода блока 1, шины 50 выхода дешифратора 20, шины 51 первого входа блока 21 и шины 52 выхода блока 21 .

Операция передачи данных в канале 1 начинается по специальной команде процессора 2, которая задает адрес селекторного канала 1 и устройства ввода-вывода, и при помощи специальных управляющих слов указывает код команды, начальный адрес оперативной памяти, количество передаваемых байт данных и другие управляющие признаки, которые располагаются в регистрах канала 1 и в локальной памяти 5, образуя в совокупности управляющие слова канала. В локальной памяти 5 размещается адрес следующего командного слова канала, адрес данных, ключи защиты, признаки и отметки, используемые в микропрограммах канала 1. Счетчик байт размещается в блоке 9, младший адрес - в счетчике 10, команда - в регистре 11. Регистры загружаются по шинам 22 из локальной памяти 5 препроцессора 2 по управляющим сигналам на шинах 23 с блока 3.

Блок 12 буферной памяти данных выiI

полней в виде стековой памяти. Загружается по шинам 28 из устройства ввода-вывода и по шинам 29 с выхода

0

5 0 25

30

35

40

45

50

мультиплексора 19 и разгружается по шинам 30 в регистр 8 или в устройство ввода-вывода.

Регистр 8 данных канала хранит 815айтовое слово, которым обменивается канал 2 с оперативной памятью 6 в процессе передачи данных.

Регистр 13 масок хранит 8-разрядную маску слова для операции считывания с устройства ввода-вывода. Управляют примером байт данных в регистр 8 с шин 33.

Блок 16 выборки байт управляет передачей байт из регистра 8 в блок 12 буферной памяти данных через мультиплексор 19 для операции записи на устройство ввода-вывода и выборкой байт с блока 12 буферной памяти данных в регистр 8 для операций считыва- , ния из устройства ввода-вывода.

Блок 17 завершения выборки байта определяет момент выключения из работы блока 16, формирует признак (Полное-неполное слово) завершения выборки байт с блока 12 буферной памяти данных в регистр 8, определяет момент выхода на микропрограммную приостановку для обслуживания данных и состояния.

Блок 21 предварительного запроса формирует предварительный признак Полное-неполное слово и предварительный запрос на микропрограммную приостановку для обслуживания данных.

Блок 18 контроля осуществляет контроль выбираемых байт из регистра 8 или блока 12.

Блок 15 управления интерфейсом осуществляет.загрузку блока 12 в операциях считывания с устройства ввода- вывода и разгрузку блока 12 в операциях записи на устройство ввода-вы- вода. Под управлением блока 15 осуществляются начальная выборка устройства ввода-вывода, завершения операции ввода-вывода на интерфейс и другие функции. i

Блок 9 подсчета байт (фиг.2) содержит счетчики 53-56 (синхронные реверсивные двоичные «-разрядные), элементы ИЛИ 57-65, элементы И 66-68, линии 69 входа и линии 70-77 выхода блока, загружается по шинам 22 вторым - третьим байтом слова локальной памяти 5 по отрицательному управляющему сигналу в линии 69 на шинах 23. Вычитание из счетчиков производится отрицательным сигналом на шине 39. Блок 9 вырабатывает на шинах 2 сигналы равенства счетчика 1,0,15- более 2 и более 3 (сигналы в линиях 70-77).

О

Блок 12 буферной памяти данных (фиг.З) содержит триггеры (регистры) 78-85, триггеры (флажки) 86-93, элементы ИЛИ , элементы И 103-111, 10 элементы ИЛИ 112,113 и линии 11 4-117 выхода блока, управляется вторым синхросигналом по шинам 38. Нулевые выходы триггеров 86-93 соединены с С-входом соответствующих регистров 15 78-85 (на фиг.З представлены только два разряда каждого буферного регистра). Если блок 12 отключен, то все триггеры 86-93 сброшены и регистрах 78-85 присутствует нулевая 20 информация, так как элементы ИЛИ 112- 113 выключены, а сигналы на С-входах регистров 78-85 включены. При загрузке блока 12, например, из регистра 8 по шинам 29, когда включается CHI- 25 нал загрузки на шинах 38 и если загружается 1, включаются элементы ИЛИ 112-113 и байт данных поступает в регистр 78 и последующие регистры.

В конце такта загрузки по заднему 30 фронту синхросигнала на шинах 38 устанавливается триггер 86 полного буферного регистра 78 через элемент ИЛИ , выключается синхросигнал на С-входе регистра 78 и байт данных 35 записывается в регистр 78. В последующем такте канала через элементы ИЛИ 95-100 и элемент И 109 устанавливается триггер 93 полного буферного регистра 85 и сбрасывается триггер 40 86, так как триггер 87 выключен, и байт данных из регистра 78 переписывается в регистр 85. В последующих тактах при загрузке через регистр 78 аналогичным образом байт данных за- 45 писывается в регистр , устанавливается триггер 92, так как включен триггер 93, и т.д.

При разгрузке блока 12 буферной амяти данных, например, на устройст- §о во ввода-вывода по шинам 30 по сигнау сброса регистра 85 на шинах А5 риггер 93 сбрасывается и байт данных з регистра передается в регистр 5, так как включается сигнал на 55 -входе регистра 85, а в следующем Ттретьем, включая такт сброса) такте станавливается триггер 93 и сбрасывается триггер 92.

Блок 12 буферной памяти вырабатывает сигнал в линии 1Й пустого регистра 78, сигнал в линии 115 пустых буферных регистров 78-80 или 78,79 и 81 одновременно, сигнал в линии 116 пустого блока 12 и сигнал в линии 11 полного регистра 85.

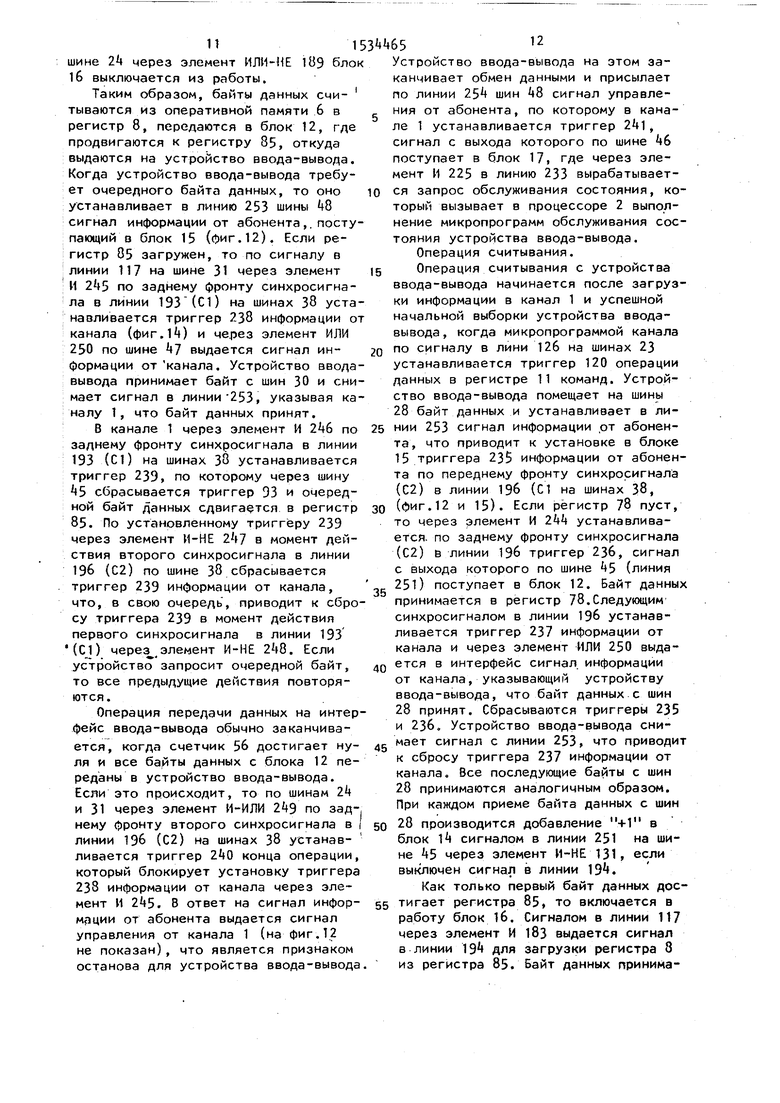

Регистр 11 команд (фиг.) содержи триггер 118 записи, триггер 119 обратного считывания, триггер 120 операции данных, триггер 121 блокировки записи в оперативную память, элементы И 122-12, линии 125-127 входов и линии 128 и 129 выхода, загружается по шине 22 входа канала нулевым байтом слова локальной памяти по управляющим сигналам в линиях 69 и 125 на шине 23 входа канала. Причем, если включен седьмой разряд нулевого байта слова локальной памяти, то устанавливается триггер 118 записи, а если седьмой, шестой разряды нулевого байта слова локальной памяти выключены и включен четвертый разряд, то через элемент И 122 устанавливается триггер 119 обратного считывания. Триггер 120 операции данных устанавливается микропрограммой канала после успешной начальной вы - борки устройства ввода-вывода сигналом в линии 126 на шине 23 входа канала, когда устройство ввода-вывода в ответ на командует канала присылает нулевой байт состояния и сбрасывается сигналом в линии 127 на шинах 23, когда завершена передача данных и устройство ввода-вывода присылает конечный байт состояния. Триггер 120 разрешает обмен данными между каналом и устройством ввода-вывода посредством включения команды записи в линии 128 или считывания в линии 129 через элементы И 123 и 12.

Триггер 121 загружается третьим разрядом нулевого байта слова локальной памяти 5 на шинах 22 по управляющему сигналу в линии 69 на шинах 23.

Триггер 121 запрещает запись в оперативную память байт данных, считываемых из устройства ввода-вывода.

Блок И подсчета байт в буферной памяти (фиг.5) содержит счетчик 130 (синхронный реверсивный двоичный -разрядный), элементы И-НЕ 131 и 132, элемент И 133, элемент ИЛИ 131 и линии 135-139 выхода блока, используется только в командах считывания из устройства ввода-вывода. Добавле

ние М1 в счетчик 130 производится в момент действия синхросигнала на шинах 38 канала по управляющему сигналу на шинах bk во время загрузки буОерного регистра 78 с шин 28, а вычитание 1 - по управляющему сигналу на шинах 38 в конце передачи из регистра 85 по шинам 30 в регистр 8 данных канала. Если указанные и уп равляющие сигналы присутствуют одновременно, то счетчик 130 не считает. Регистр 13 масок (фиг.6) содержит триггеры ЙО-Й7 масок соответственно нулевого - седьмого байт регистра 8, элементы V1 Й8-1б и линии 165. Триггеры масок устанавливаются по сигналу загрузки регистра 8Ј в регистр 8 на шинах 38 в момент действия второго синхросигнала на шинах 38, в зависимости от содержимого счетчика 10 младшего адреса через дешифратор 20 (выходы 166-173) Регистр 13 масок сбрасывается сигналом на шинах 37 с блока 7 после передачи данных из регистра 85 в оперативную память 6. В регистре 13 формируется через элемент И 16 на шин 36 сигнал полного слова в регистре 8

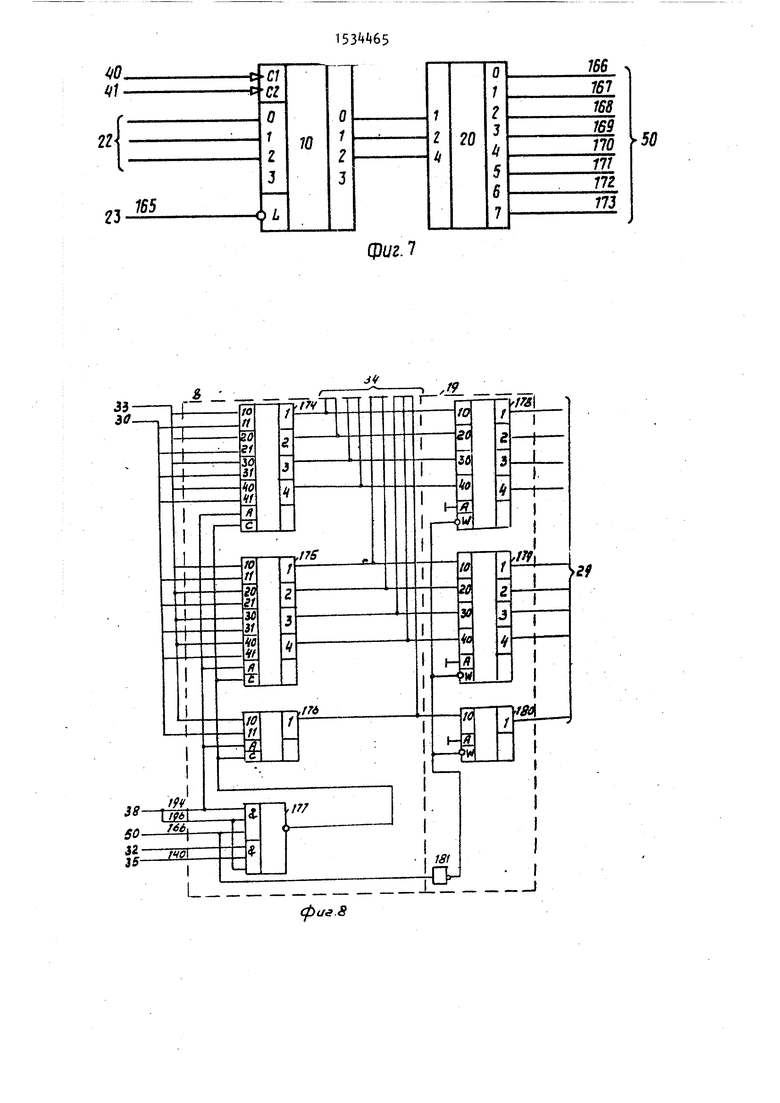

Счетчик 10 младшего адреса с вход ной линией 165 (фиг.7) выполнен как синхронный двоичный реверсивный -разрядный счетчик. Регистр 11 загружается по шине 22 одна младшими разрядами третьего байта слова локальной памяти 5 по управляющему сигналу в линии 165 на шинах 23. Добавление 1 в счетчик 10 производится по отрицательному сигналу на шинах UO, а вычитание 1 - по отрицательному сигналу на шинах П. Выходы 166-173 дешифратора 20 подаются на входы регистра 13 (фиг.7).

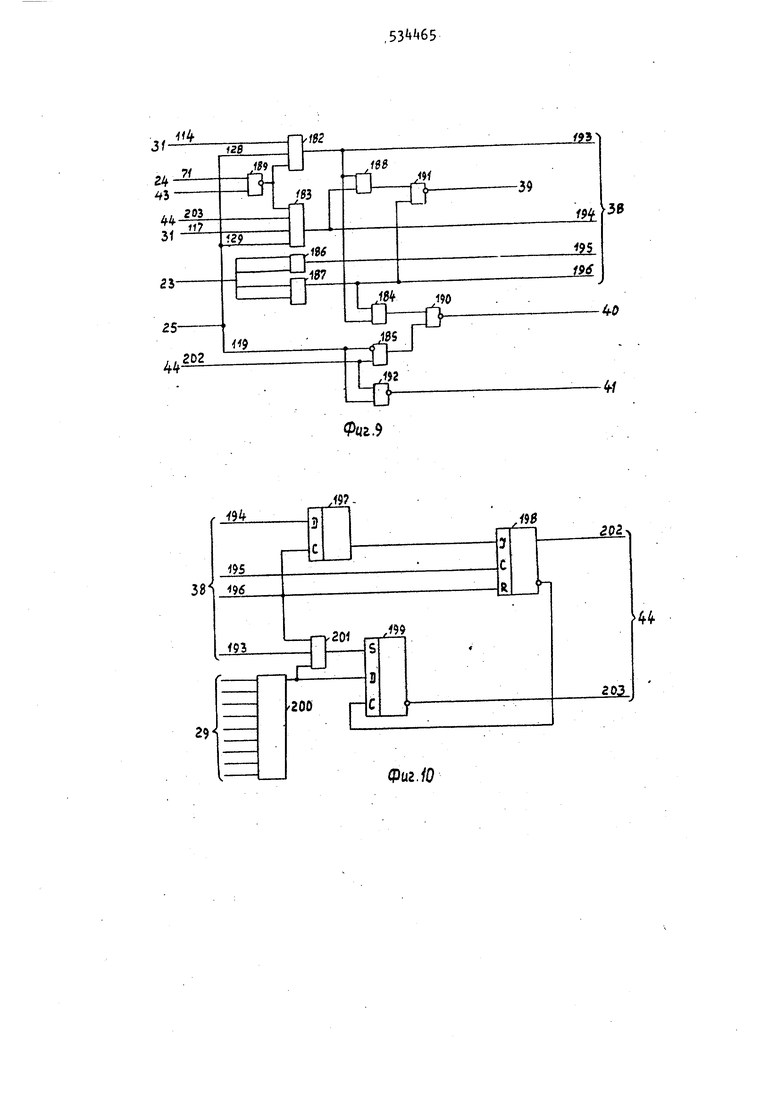

Регистр 8 данных (фиг.8) может - быть выполнен на селекторах-мультиплексорах с запоминанием и элементе И-ИЛИ-НЕ 177, загружается по переднему фронту второго синхросигнала на шинах 38 с регистра 85 с шин 30 по управляющему сигналу на шинах 38, если включен сигнал в лини 166 на выходе дешифратора 20, из оперативной памяти 6 (нулевого байта слова) по шинам 33 по управляющему сигналу на шине 32, если триггер нулевого байта регистра 8 сброшен. На фиг.8 представлен только нулевой байт восьмибайтного регистра 8. Ос15

- JQ .

зо

и

тальные байты регистра 8 идентичны нулевому.

Мультиплексор 19 (для нулевого байта) содержит (фиг.8) -разрядные селекторы-мультиплексоры 178-180 с тремя устойчивыми состояниями по выходу и элемент НЕ 181. Мультиплексоры 178-180 переключаются из третьего (высокоимпедансного) состояния сигналом в линии 166 на шинах 50 с выхода дешифратора 20 через элемент НЕ 181. Одноименные выходы мультиплексоров 19 всех байтов (например, вторые разряды мультиплексора нулевого - седьмого байта) объединены. Таким образом, при модификации счетчика 10 посредством дешифратора 20 выбирается через мультиплексоры 173- 180 один из байтов регистра 8.

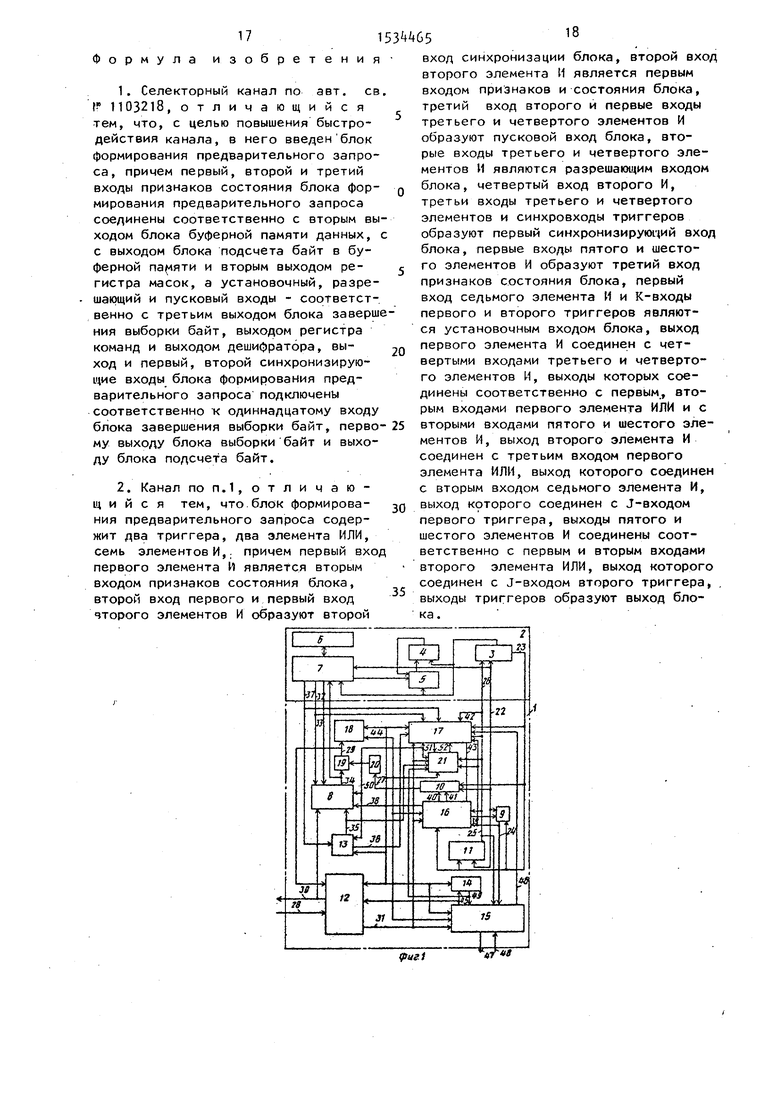

Блок 16 выборки байт (фиг.9) содержит элементы И 182-185, ИЛИ 186- 188, ИЛИ-НЕ 189 и 190, И-НЕ191 и 192, линии 193-196 шин 38 первого выхода блока 16.

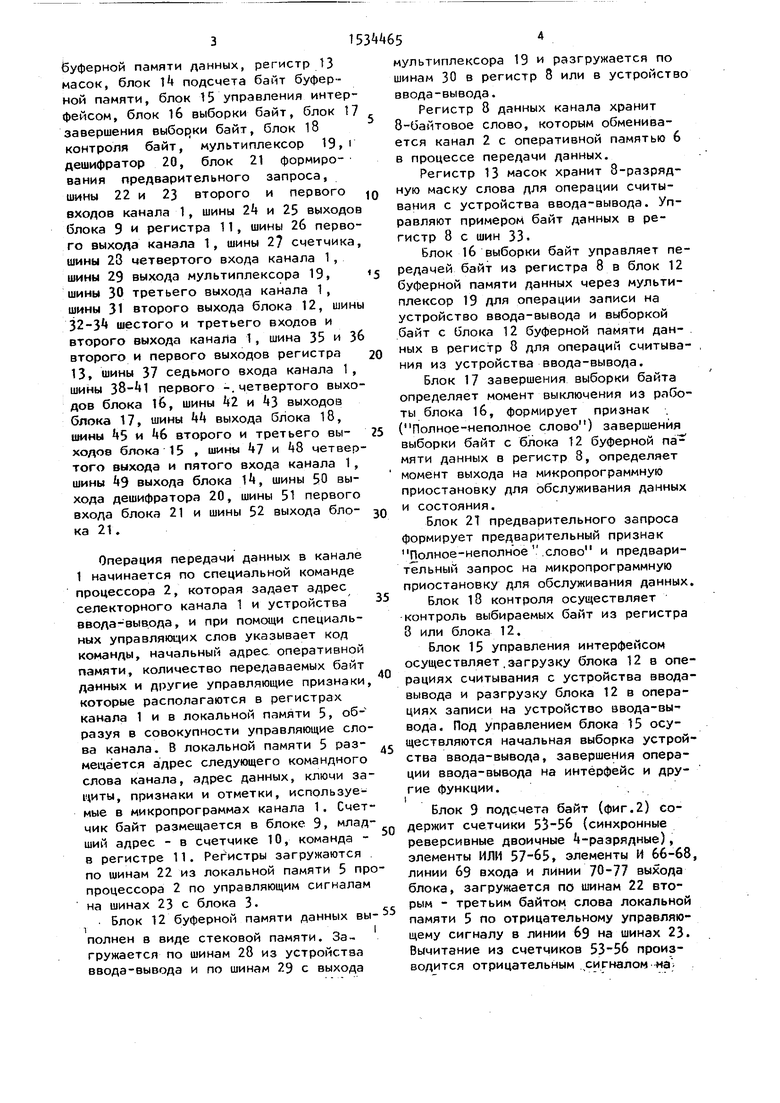

Блок 18 контроля байт (фиг.10) содержит триггер 197 задержки сигнала в линии 19 загрузки регистра 85 в регистр 8, триггер 198 модификации регистра 11, триггер 199 ошибки данных в регистре 8, дешифратор 200 четности, элемент И 201, линии 202 и 203 шины й выхода блока.

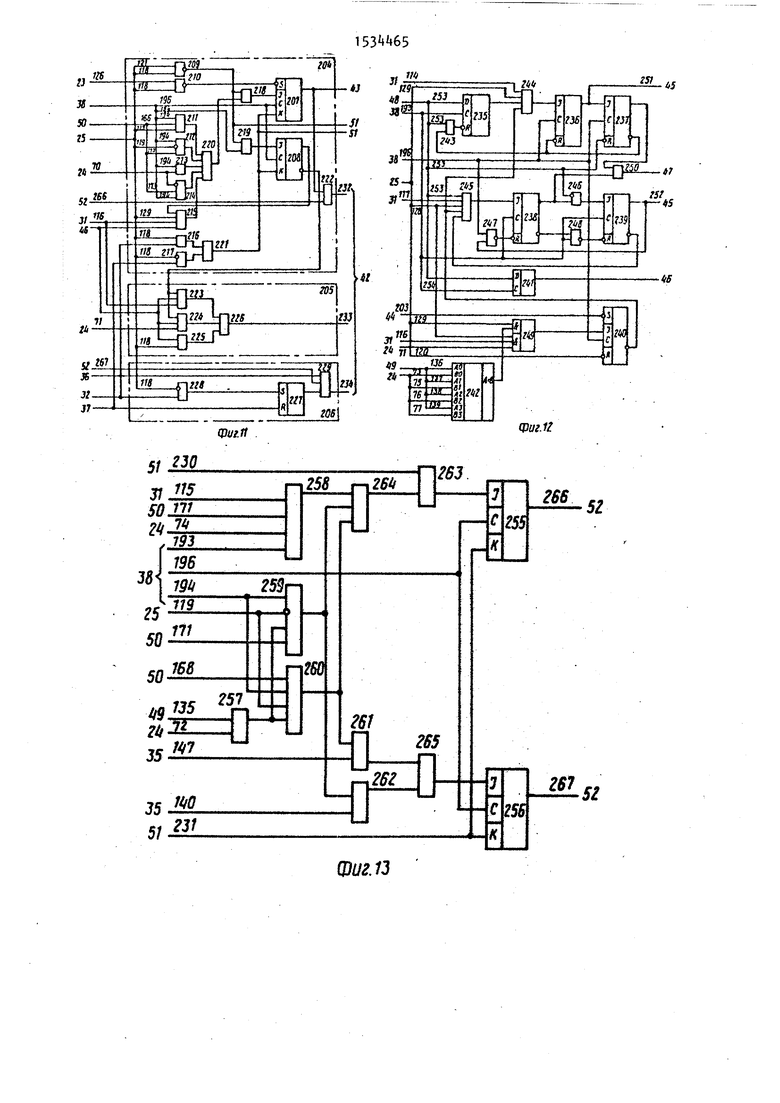

Блок 17 завершения .выборки байт 35 (фиг.11) состоит из узла 20 формирования запроса данных, узла 205 формирования запроса состояния и узла 206 формирования признака полного слова. Узел 20 содержит триггер 207 запроса данных триггер, 208 ненулевой мас ки слова и коммутатор сигналов запроса данных, включающий элементы И-НЕ 209 и 210, И 211-219, ИЛИ 220-222. Узел 205 представляет собой коммутатор сигналов состояния, выполненный на элементах И 223-225 и элементе ИЛИ 226. Узел 206 содержит триггер 227 полного слова, элемент И 228, ИЛИ 229, линии 230 и 231 шины 51 ли-, нии 232-231 шины k2.

20

25

40

45

50

Блок 15 управления интерфейсом (фиг. 12) содержит триггеры 235-2М, элемент сравнения двух чисел,, элементы И (,t И-НЕ , И-ИЛИ , ИЛИ 250, линии 251 и 252 шины U5. Сигнал в линии 253 на шинах i8 устанавливает триггер 235, сигнал в линии 25 на шинах 48 - триггер .

9

Блок 21 формирования предварительного запроса (Оиг.13) содержит триггер 255 предварительного запроса данных, триггер 256 предварительного полного слова, элементы И 257-263, ИЛИ 26 4-265, линии 266 и 267 шины 52

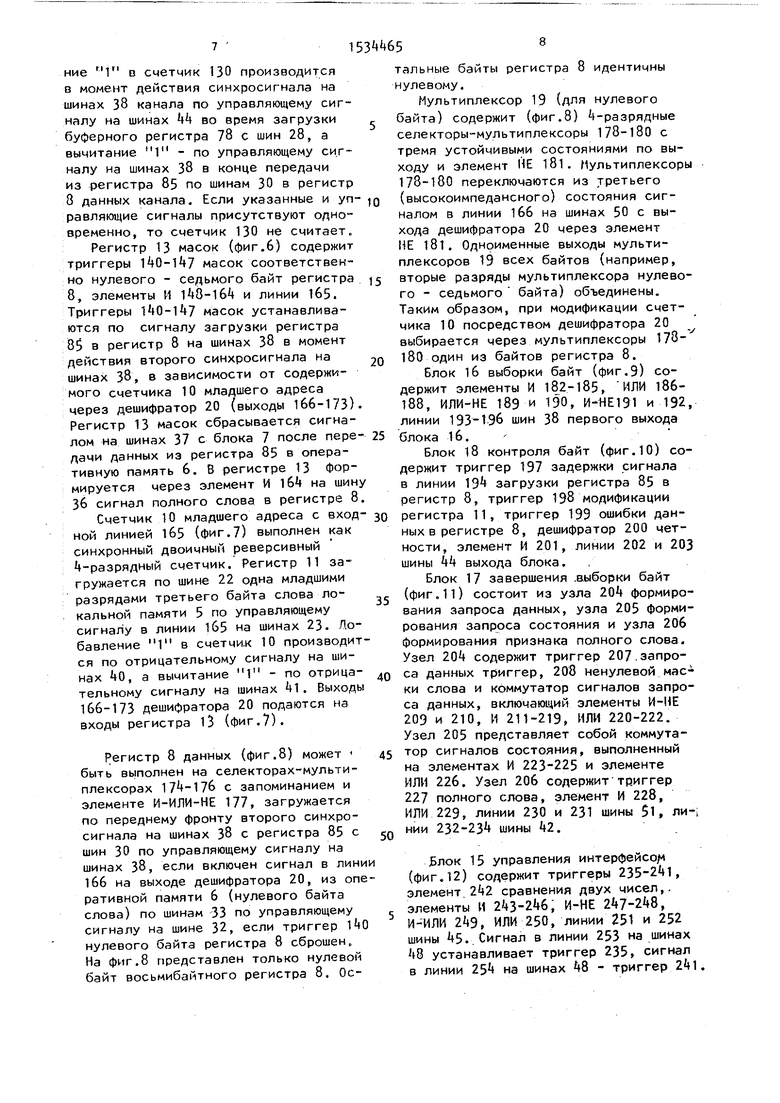

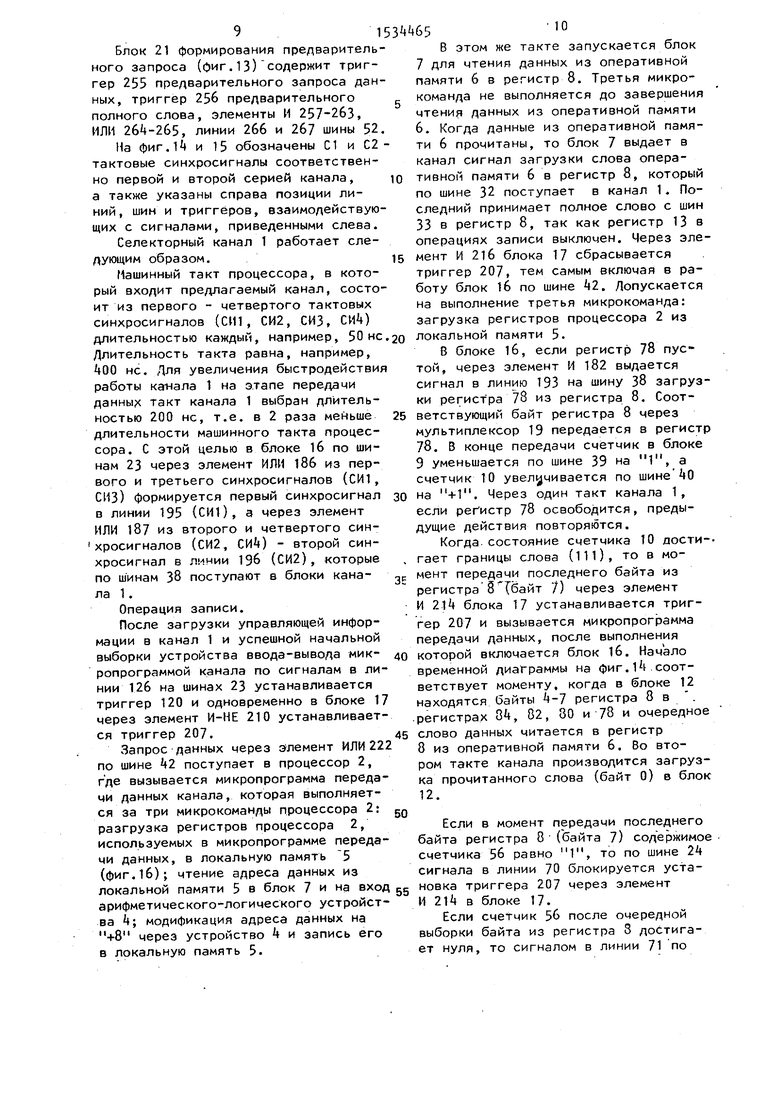

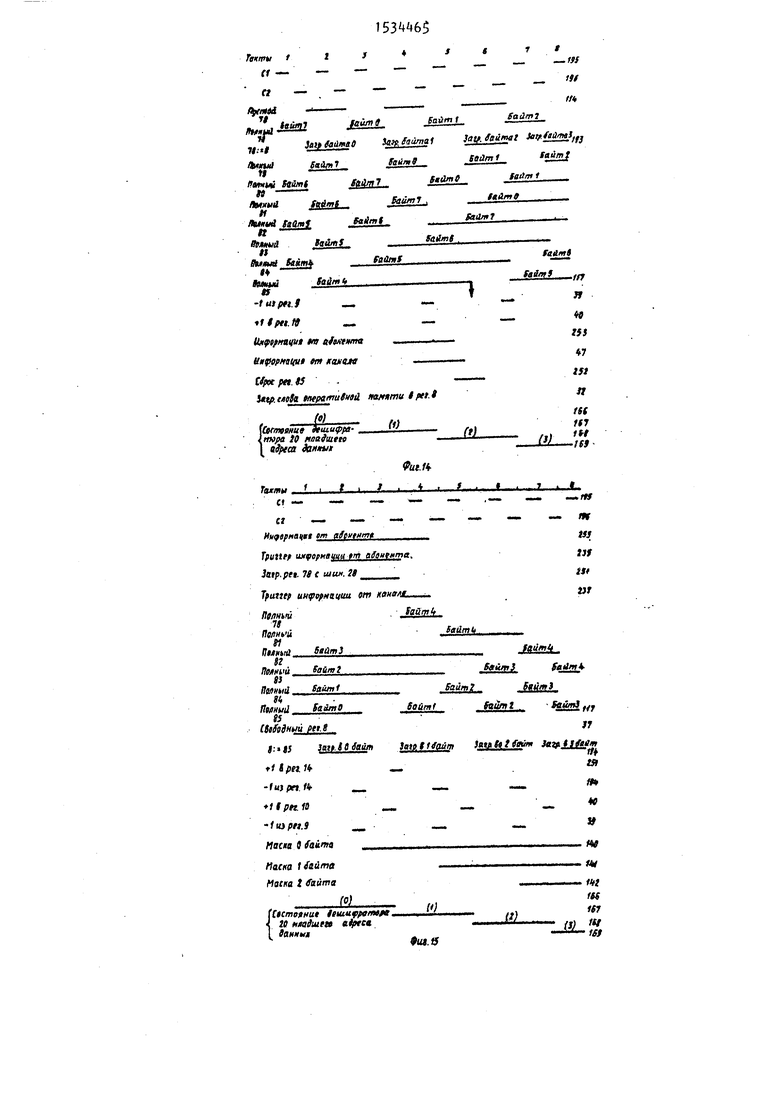

На фиг. и 15 обозначены С1 и С2 тактовые синхросигналы соответственно первой и второй серией канала, а также указаны справа позиции линий, шин и триггеров, взаимодействующих с сигналами, приведенными слева.

Селекторный канал 1 работает следующим образом.

Машинный такт процессора, в который входит предлагаемый канал, состоит из первого - четвертого тактовых синхросигналов (СИ1, СИ2, СИЗ, СИМ длительностью каждый, например, 50нс Длительность такта равна, например, kQQ не. Для увеличения быстродействи работы канала 1 на этапе передачи данных такт канала 1 выбран длительностью 200 не, т.е. в 2 раза меньше длительности машинного такта процессора. С этой целью в блоке 16 по шинам 23 через элемент ИЛИ 186 из первого и третьего синхросигналов (СИ1, СИЗ) формируется первый синхросигнал в линии 195 (СИ1), а через элемент ИЛИ 187 из второго и четвертого синхросигналов (СИ2, - второй син- в линии 196 (СИ2), которые поступают в блоки канахросигналпо шинам 38 ла 1 .

Операция записи.

После загрузки управляющей информации в канал 1 и успешной начальной выборки устройства ввода-вывода микропрограммой канала по сигналам в линии 126 на шинах 23 устанавливается триггер 120 и одновременно в блоке 17 через элемент И-НЕ 210 устанавливается триггер 207.

Запрос данных через элемент ИЛИ 22 по шине 2 поступает в процессор 2, где вызывается микропрограмма передачи данных канала, которая выполняется за три микрокоманды процессора 2: разгрузка регистров процессора 2, используемых в микропрограмме передачи данных, в локальную память 5 (фиг.1б); чтение адреса данных из локальной памяти 5 в блок 7 и на вход арифметического-логического устройства 4; модификация адреса данных на +8 через устройство и запись его в локальную память 5.

10

0

5

о локальной

В этом же такте запускается блок 7 для чтения данных из оперативной памяти 6 в регистр 8. Третья микрокоманда не выполняется до завершения чтения данных из оперативной памяти 6. Когда данные из оперативной памяти 6 прочитаны, то блок 7 выдает в канал сигнал загрузки слова оперативной памяти 6 в регистр 8, который по шине 32 поступает в канал 1. Последний принимает полное слово с шин 33 в регистр 8, так как регистр 13 в операциях записи выключен. Через элемент И 216 блока 17 сбрасывается триггер 207, тем самым включая в работу блок 16 по шине 2. Допускается на выполнение третья микрокоманда: загрузка регистров процессора 2 из

памяти 5.

В блоке 16, если регистр 78 пустой, через элемент И 182 выдается сигнал в линию 193 на шину 38 загрузки регистра 78 из регистра 8. Соот- 5 ветствующий байт регистра 8 через

мультиплексор 19 передается в регистр 78. В конце передачи счетчик в блоке 9 уменьшается по шине 39 на 1, а счетчик 10 увеличивается по шине 0 на +1. Через один такт канала 1, если регистр 78 освободится, предыдущие действия повторяются.

Когда состояние счетчика 10 дости-- гает границы слова (111), то в момент передачи последнего байта из регистра 8 (байт 7) через элемент И блока 17 устанавливается триггер 207 и вызывается микропрограмма передачи данных, после выполнения которой включается блок 16. Начало временной диаграммы на фиг.11 соответствует моменту, когда в блоке 12 находятся байты 4-7 регистра 8 в регистрах 0, 82, 80 и 78 и очередное слово данных читается в регистр 8 из оперативной памяти 6. Во втором такте канала производится загрузка прочитанного слова (байт 0) в блок 12.

0

Е

0

5

Если в момент передачи последнего байта регистра 8 (байта 7) содержимое счетчика 56 равно 1, то по шине 24 сигнала в линии 70 блокируется установка триггера 207 через элемент И в блоке 17.

Если счетчик 56 после очередной выборки байта из регистра 3 достигает нуля, то сигналом в линии 71 по

шине через элемент ИЛИ-НЕ 189 бло 16 выключается из работы.

Таким образом, байты данных счи- тываются из оперативной памяти 6 в регистр 8, перелаются в блок 12, где продвигаются к регистру 85, откуда выдаются на устройство ввода-вывода. Когда устройство ввода-вывода требует очередного байта данных, то оно устанавливает в линию 253 шины 8 сигнал информации от абонента,, поступающий в блок 15 (фиг.12). Если регистр 85 загружен, то по сигналу в линии 117 на шине 31 через элемент И по заднему фронту синхросигнала в линии 193(С 1) на шинах 38 устанавливается триггер 238 информации о канала (фиг.И) и через элемент ИЛИ 250 по шине 7 выдается сигнал информации от канала. Устройство ввода вывода принимает байт с шин 30 и снимает сигнал в линии 253, указывая каналу 1, что байт данных принят.

В канале 1 через элемент И по заднему фронту синхросигнала в линии 193 (С1) на шинах 38 устанавливается триггер 239, по которому через шину 5 сбрасывается триггер 93 и очередной байт Данных сдвигается в регистр 85. По установленному триггеру 239 через элемент И-НЕ в момент действия второго синхросигнала в линии 196 (С2) по шине 38 сбрасывается триггер 239 информации от канала, что, в свою очередь, приводит к сбросу триггера 239 в момент действия первого синхросигнала в линии 193 (С1) через элемент И-НЕ . Если устройство запросит очередной байт, то все предыдущие действия повторяются.

Операция передачи данных на интерфейс ввода-вывода обычно заканчивается, когда счетчик 56 достигает нуля и все байты данных с блока 12 переданы в устройство ввода-вывода. Если это происходит, то по шинам 2 и 31 через элемент И-ИЛИ по заднему фронту второго синхросигнала в линии 196 (С2) на шинах 38 устанавливается триггер конца операции, который блокирует установку триггера 238 информации от канала через элемент И . В ответ на сигнал информации от абонента выдается сигнал управления от канала 1 (на фиг.12 не показан), что является признаком останова для устройства ввода-вывода

0

Устройство ввода-вывода на этом заканчивает обмен данными и присылает по линии 25 шин Ц8 сигнал управления от абонента, по которому в канале 1 устанавливается триггер , сигнал с выхода которого по шине 6 поступает в блок 17, где через элемент И 225 в линию 233 вырабатывается запрос обслуживания состояния, который вызывает в процессоре 2 выполнение микропрограмм обслуживания состояния устройства ввода-вывода. Операция считывания.

5 Операция считывания с устройства ввода-вывода начинается после загрузки информации в канал 1 и успешной начальной выборки устройства ввода- вывода , когда микропрограммой канала по сигналу в лини 126 на шинах 23 устанавливается триггер 120 операции данных в регистре 11 команд. Устройство ввода-вывода помещает на шины 28 байт данных и устанавливает в ли5 нии 253 сигнал информации от абонента, что приводит к установке в блоке 15 триггера 235 информации от абонента по переднему фронту синхросигнала (С2) в линии 196 (С1 на шинах 38,

0 (фиг.12 и 15). Если регистр 78 пуст, то через элемент И устанавливается по заднему фронту синхросигнала (С2) в линии 196 триггер 236, сигнал с выхода которого по шине 5 (линия 251) поступает в блок 12. Байт данных принимается в регистр 78.Следующим синхросигналом в линии 196 устанавливается триггер 237 информации от канала и через элемент ИЛИ 250 выдается в интерфейс сигнал информации от канала, указывающий устройству ввода-вывода, что байт данных с шин 28 принят. Сбрасываются триггеры 235 и 236. Устройство ввода-вывода снимает сигнал с линии 253, что приводит к сбросу триггера 237 информации от канала. Все последующие байты с шин 28 принимаются аналогичным образом. При каждом приеме байта данных с шин

0 28 производится добавление +1 в блок 1 сигналом в линии 251 на шине 5 через элемент И-НЕ 131, если выключен сигнал в линии 19.

Как только первый байт данных дос5 тигает регистра 85, то включается в работу блок 16. Сигналом в линии 117 через элемент И 183 выдается сигнал в линии 19 для загрузки регистра 8 из регистра 85. Байт данных принима5

0

5

13

ется в соответствующий байт регистра 8 (согласно состоянию счетчика 10 на входе дешифратора 20), устанавливается в регистре 13 триггер маски соответствующего байта регистра 8. В конце такта загрузки по шине 39 производится вычитание 1 с блока 9 модификация на 1 счетчика 10 (на И для операции считывания через элемент ИЛИ-НЕ 190 по шине 40, на 1 для операций обратного считывания через элемент И-НЕ 192, по шине 41), производятся вычитание 1 с блока И через элемент И-НЕ 132 по сигналу в линии 19 и сброс регистра 85 по сигналу в линии 194. При загрузке хотя бы одного байта в регист 8 всегда устанавливается триггер 208 через элемент И 219 в блоке 17.

При последующих загрузках байтов данных с шин 28 описанные действия повторяются.

Блок 17 выключает блок 16 и формирует запрос данных для выполнения микропрограммы передачи данных в следующих случаях: когда в процессе выборки байт достигается граница слова в регистре 8, в этом случае для команды считывания устанавливается триггер 208 через элемент И 212, а для команды обратного считывания - через элемент И 211; когда выбирается последний Сайт г. блока 12, то по шине 2 через элемент И 213 устанавливается триггер 207; когда с устройства ввода считывается блок данных длинной, меньшей, чем указано в счетчике 56, в этом случае устройство ввода вместо запроса на линии 253 присылает сигнал по линии 25, который устанавливает триггер 241, сигнал с единичного выхода которого по шине 46 поступает в блок 17. Если условия, описанные в первом случае, не соблюдаются, то после выборки все байтов данных с блока 12 в регистр 8 сигналом в линии 116 (пустой буфер через элемент И 215 устанавливается триггер 207 запроса данных. Сигнал запроса состояния в линии 233 блокируется по сигналу на шинах 46 на элементах и 223 и 224 низким уровнем сигнала с нулевого выхода триггера 208.

Запрос данных по шине 42 поступает в процессор 2, где вызывается микропрограмма передачи данных канала , которая выполняется за три

14

,

10

20

25

30

35

40

45

микрокоманды (фиг.1б): разгрузка регистров процессора 2 в локальную память 5 и ветвление по триггеру 119 и признаку в линии полного слова; прямое и обратное считывание полного слова, чтение адреса данных из локальной памяти 5 в блок 7 на вход арифметико-логического устройства 4, модификация адреса данных

48

или

-81

челосоответственно на

рез устройство 4 и запись его в

кальную память 5.

В этом же такте запускается блок 15 7 для записи данных из регистра 8 по шинам 34 в оперативную память 6.

Третья микрокоманда не выполняется до завершения передачи и записи переданных данных из регистра 8 в оперативную память 6. Когда данные из регистра 8 переданы, то блок 7 выдает в канал 1 сигнал свободного регистра 8, который по шине 37 поступает в блок 17 и регистр 13. Регистр 13 сбрасывается и через элемент И 217 сбрасываются триггеры 207 и 208 вторым синхросигналом по линии 196 (С2), тем самым включая в работу блок 16. Запускается после записи в оперативную память 6 данных третья микрокоманда (загрузка регистров процессора 2 из памяти 5).

Прямое или обратное считывание неполного слова.

Эта микрокоманда анапогична второй микрокоманде в операциях записи за исключением того, что адрес данных не модифицируется,данные с шин 33 принимаются в регистр 8 по маске слова в регистре 13, сигналом загрузки слова оперативной памяти 6 в регистр 8 на шинах 32 через элемент И 228 устанавливается триггер 227, триггеры 207 и 208 не сбрасываются. Это дает возможность повторно войти в микропрограмму передачи данных, но уже для записи полного слова, после выполнения третьей микрокоманды, как описано.

Операция передачи данных на интерфейс ввода-вывода обычно заканчивается, когда содержимое счетчика 130 в блоке 1 становится равным содержимому счетчиков 53-56 в блоке 9. В этом случае через элемент 242 сравнения (фиг.12) устанавливается триггер 240 конца операции, который через элемент И 244 блокирует установку триггера 236. Дальнейшие действия на

50

55

15

интерфейсе аналогичны действиям в операциях записи.

Сигнал запроса состояния в линии 233 вырабатывается по сигналу управления от абонента на шине в блоке 17 через элемент И 2М, если имеется сигнал равенства нулю счетчика байт в линии 71 и выключен триггер 208 ненулевой маски; через элемент И 223, если имеется сигнал пустого блока буферной памяти данных в линии 11( и выключен триггер 208 ненулевой маски.

При считывании байт данных с устройства ввода-вывода с блокировкой записи в оперативную память 6 установлен триггер 121 в регистре 11. Это вызывает блокировку установки триггера 207 через элемент И-НЕ 209. Микропрограмма передачи не выполняется, а все описанные действия в канале выполняются.

Начало временной диаграммы на фиг. соответствует моменту, когда в микропрограмме передачи ланных освобождается регистр 8 (в такте 1) , в блоке 12 накоплены k байта (байты 0-3), которые расположены в регистрах 82-85. Контроль выбираемых байт осуществляется в блоке 18. При выполнении операции выбранный байт из регистра 8 поступает через мультиплексор 19 в блок 18 на дешифратор 200. Если байт имеет неправильную четность, то через элемент И 201 сигналом в линии 193 загрузки регистра 8 в регистр 73 в линии 19 устанавливается триггер 199 ошибки в момент действия второго синхросигнала в линии 196 (С2) . При выполнении операции считывания выбранный байт из регистра 85 поступает в соответствующий байт регистра 8 и через мультиплексор 19 на дешифратор 200. Если байт имеет неправильную четность, то при выключении триггера 198 устанавливается триггер 199- Адрес данных в операциях считывания модифицируется посредством триггеров 197 и 193 с задержкой по отношению к сигналу за- з грузки регистра 85 в регистр 8 линии 19, чтобы иметь возможность контроля загруженного байта в регистр 8 через мультиплексор 19.

Таким образом, с помощью одного дешифратора 200 четности осуществляется контроль всех выбираемых байт данных в канале.

153 651б

Установка триггера 199 блокирует по шине загрузку буферного регистра

85

5

0

5

0

5

0

5

0

5

)5 в р егистр 8 данных канала и вызывает установку триггера конца операции в блоке 15 управления интерфейсом.

Блок 21 начинает работать при обмене данными с высокоростными устройствами ввода-вывода, когда канал отстает от устройства в операциях записи и когда устройство опережает канал в операциях считывания.

При выполнении операции записи байты данных, загруженные в регистр 8 выдаются по шинам 3 в блок 12, а затем по шинам 30 в устройство ввода-вывода.

По мере того, как регистр разгружается, его загружают новыми байтами данных с блока 7. Если к моменту передачи пятого байта слова (сигнал в линии 171 на шинах 50) из регистра 8 в регистр 78 блока 12 по управляющему сигналу в линии 193 на шинах 38 в блоке 12 уже имеются два пустых регистра из регистров 79-81 (сигнал в линии 115 на шинах 31) и состояние 53-56 байт блока 9 больше двух (сигнал в линии 7 на шинах 2k), через элемент И 258 устанавливается триггер 255 и вызывается микропрограмма передачи данных.

К моменту обращения к памяти через время выполнения первой микрокоманды на фиг.17) регистр 8 уже передает оставшиеся два байта данных в блок 12 и готов к приему нового слова данных.

При выполнении операции Считать блок 12 быстро загружается из устройства ввода-вывода, а затем передается в регистр 8. Когда пятый байт слова данных для команд считывания или обратного считывания соответственно передается с блока 12 в регистр 8 по управляющему сигналу в линии 19 на шинах 38, состояние счетчиков байт блока 9 более двух (сигнал в линии 72 на шинах и в блоке 1Z имеется более двух байт (сигнал в линии 135 на шинах 9), то через элемент И 259 или 260 устанавливается триггер 255 предварительного запроса и вызывается микропрограмма передачи данных, как было описано.

риг1

fr«t

LA

чо

-т J- го un

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Селекторный канал | 1975 |

|

SU570891A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

Изобретение относится к вычислительной технике, может быть использовано в вычислительных комплексах и является усовершенствованием известного селекторного канала по авт. св. N 1103218. Введение блока формирования предварительного запроса в известный селекторный канал по авт. св. N 1103218 повышает его производительность, что позволяет подключать более быстродействующие устройства ввода - вывода и вести обмен данными со специализированными устройствами передачи данных с большей скоростью и повысить производительность вычислительных комплексов при связи двух ЭВМ через адаптеры канал - канал. 1 с., 1 з.п. ф-лы. 17 илл.

v

«

Put.S.

Сц Г- - Cb

14

S

J4 N - CS

U1 bo

-c-

ON

U1

4t -

- o th - - о

S

§

«

§

(J1L

,W3 С

95 38i 196

f93

-T-vSOf

200

J95

3 С

202JW

44

г оз

Фиг, 10

гя

«

;

Фиг. 13

Л t г J т да

d - - - - - - -

- -

-

/JiJtesz . -ЈЈЈ21 ю йм Ubfiu- ff ±alff)

ie

7fed/ Jttlml

BlIHmu

toLlJbimjfa f. «Ј2f

ЙМ/+

. ./. . . 4 .

CJ « «ЯМ Ml «MM MV

Hv ftfnaii4 im (tfcxmmtfjj

Tfuttrf ujtyotMtiua tm ttfeHmme.Uf

pti. t t uiiui. Ц fft

Tfiatef инффнвции вт ночамUT nt/ww fen/n t

neflm u(eumit

H

ПмнчЛ SiumJfgtlmit

Яинчй faumlStwnJ fail

Питый ScAmlБайт 2 jkumJ

Пмнм SaAmt SeumjHun I faum fff

IkltdHuu pti I...IT

Г «15 Jgt t feum Jen,t tfqtim ) V ft i Mm ittfUfttm

It

tit pti H №

-1u)pn1k0

+ 11РП.П -

-1ЮРН.9 .- -.

«oc«e 0 faint . .. . . ....

Маога f fauma «v

Считы1акиг(

4umntet,ue(ttl i) .

полису (fftfe(fjti.l) mulauut MtntflH M

Т

Т,

Тд Tm Т0ж Ton

ч

Предварительный запрос 255

Запрос 201

)qnU(i(1fs) f

Pffirpylro prtue Pfl fftmrcecfa v локальную Orrtmt (5)

4tVu/ alfK9 Запит ui Jjrt/i Hiintnirii ilSfi 7

Чтгщ leank u) tntpemutvai na- Kimu (tltprt unf lnnHur яанала (I) it fttcKt c/iala I peeuf ft(U)

ctefe one- femulHeu rtoritmH I регистр ftnuui

напала

w.

Jaifyito priucr pot про чесе вря ю /mnanHod пвняти (5)

Т

П

| Селекторный канал | 1983 |

|

SU1103218A1 |

| G Of, F 13/12; 1983. | |||

Авторы

Даты

1990-01-07—Публикация

1988-04-04—Подача