Изобретение относится к импульсной технике и может быть использовано при разработке цифровых логических устройств.

Известны однотактные счетные триггеры на МОП-транзисторах с дополнительной симметрией, содержащие квазистатический триггер, инвертор и схему совпадения.

Однако эти триггеры требуют для реализации одного двоичного разряда большого количества МОП-транзисторов.

С целью упрощения единичное плечо предложенного квазистатического триггера подключено к затворам транзисторов инвертора, выход инвертора соединен со стоком первого транзистора схемы совпадения, исток второго транзистора схемы совпадения подключен к затворам нулевого плеча квазистатического триггера, а затворы первого и второго транзисторов схемы совпадения соединены соответственно с выходом единичного плеча триггера предыдущего каскада и со счетным входом, подключе1П1ым к выходу схемы управления.

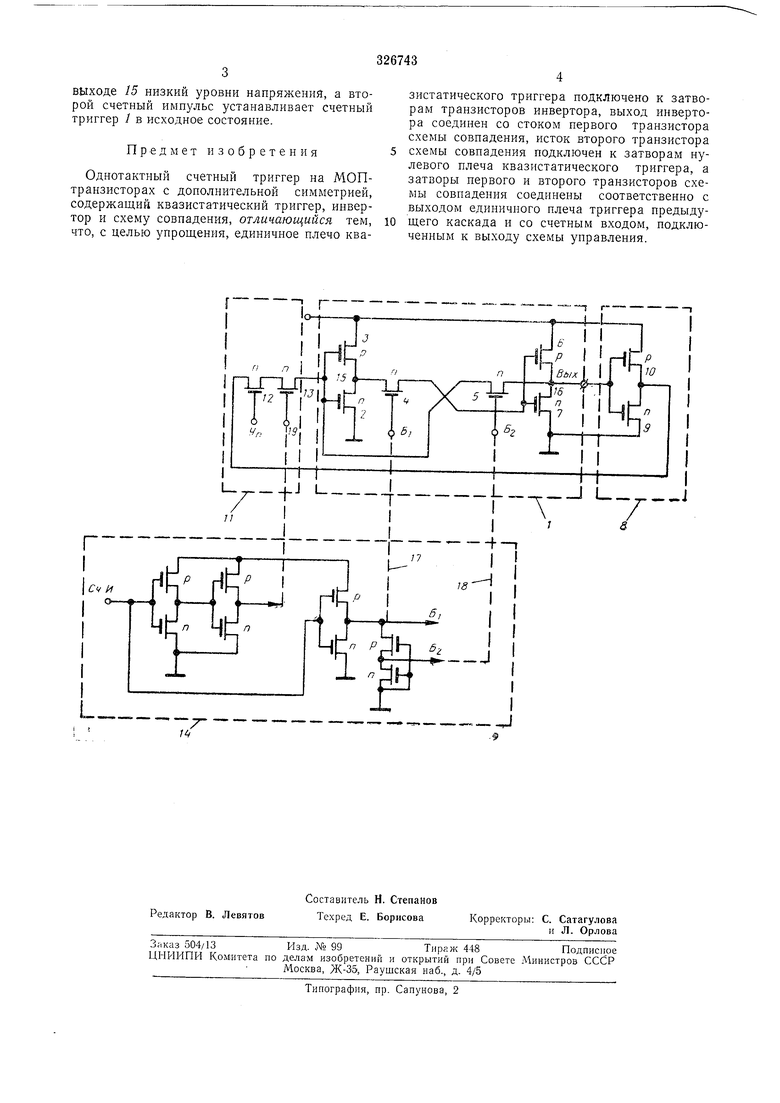

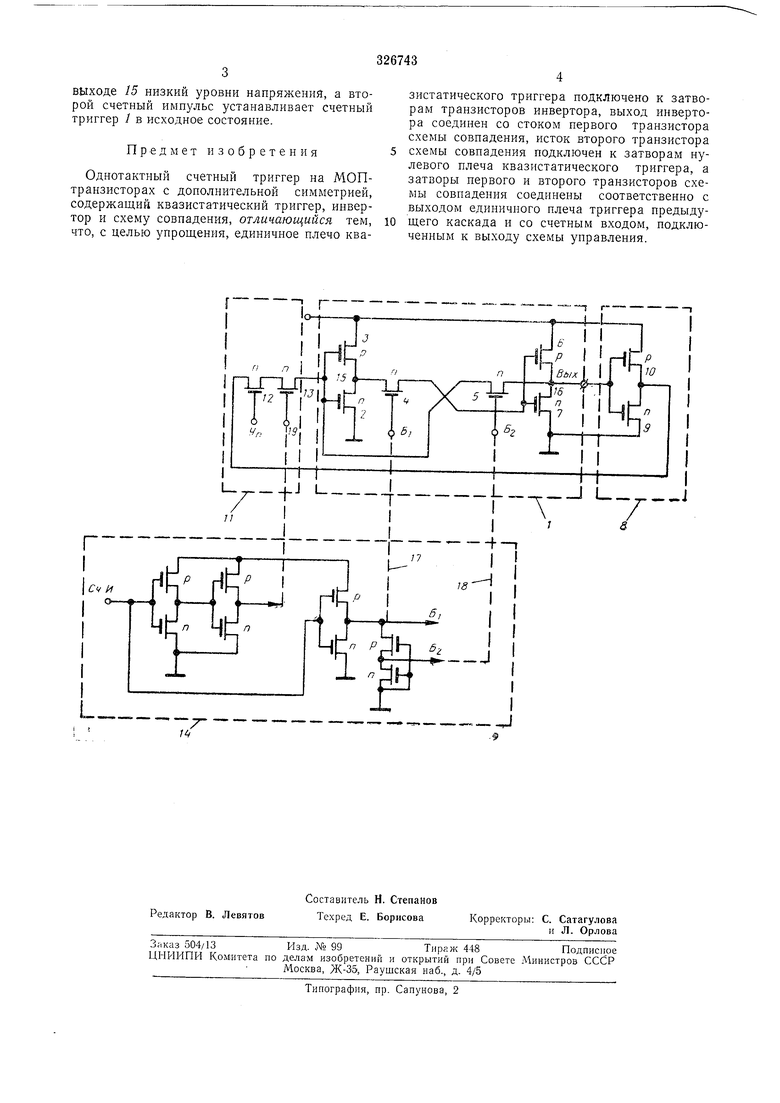

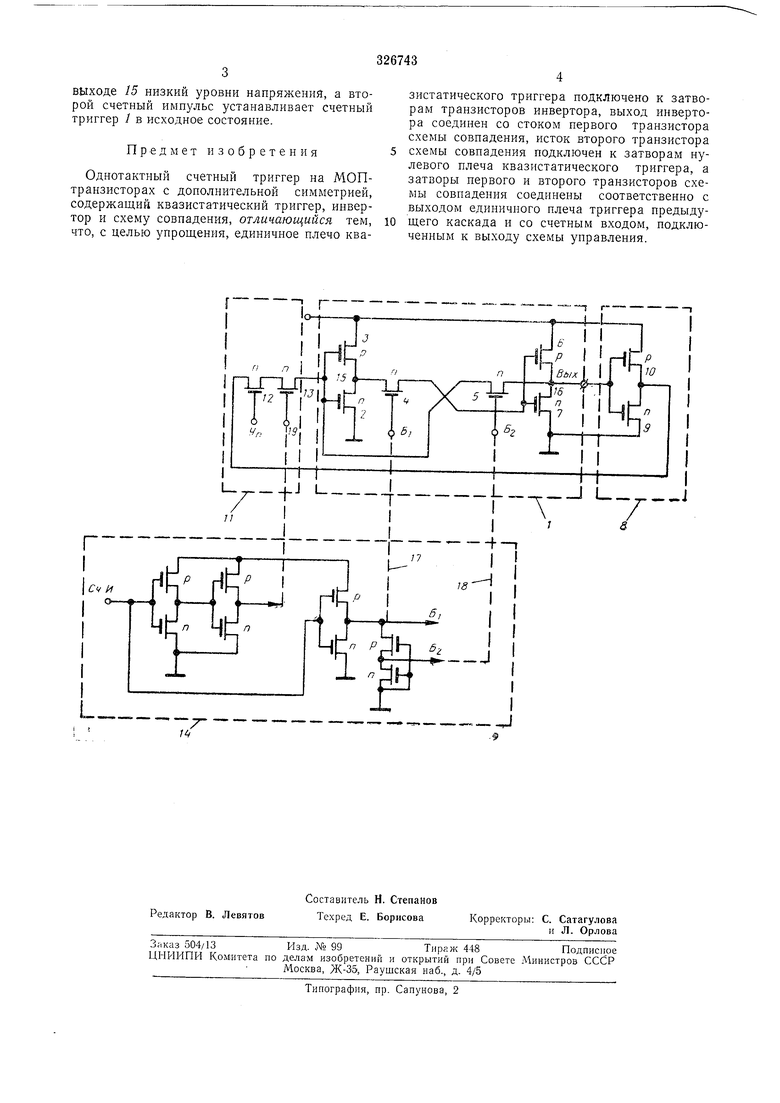

На чертеже приведена функциональная схема предложенного триггера.

Устройство содержит квазистатический триггер 1 на транзисторах 2-7, инвертор 8 на транзисторах 9, 10 и схему 11 совпадения иа транзисторах 12, 13. Единичное плечо триггера, являющееся информационным выходом

разряда счетчика, подключено к затворам инвертора 8, выход которого подключен к стоку транзистора 12, а исток транзистора 13 соединен с затворами транзисторов 2, 3 нулевого

плеча триггера /.

Для управления работой квазистатических триггеров / используется схема 14 управления, которая вырабатывает блокирующие импульсы Б и BZ для всех п разрядов счетчика.

В начале работы счетный триггер 1 находится в нулевом состоянии. При этом на выходе 15 высокий, а на выходе 16 низкий уровень напряжен1 я. Связн 17 и 18 включены (только для первого каскада счетчика), а на

электроды затвора и стока транзистора 12 подаются положительные уровни напряжений от батареи и с выхода инвертора 8 соответственно. В этом состоянии триггер / находится до прихода первого счетного импульса положительиой полярности, подаваемого на вход 19.

При подаче первого счетного импульса открывается схема }} совпадения, разрываются связи 17 и 18, на выходе транзистора 2 формируется низкий уровень нaпpянieния, а на выходе транзистора 7 уровень напрял ения не изменяется.

выходе 15 низкий уровни напряжения, а второй счетный импульс устанавливает счетный триггер / в исходное состояние.

Предмет изобретения

Однотактный счетный триггер на МОПтранзисторах с дополнительной симметрией, содержащий квазистатический триггер, инвертор и схему совпадения, отличающийся тем, что, с целью упрощения, единичное плечо квазистатического триггера подключено к затворам транзисторов инвертора, выход инвертора соединен со стоком первого транзистора схемы совпадения, исток второго транзистора схемы совпадения подключен к затворам нулевого плеча квазистатического триггера, а затворы первого и второго транзисторов схемы совпадения соединены соответственно с выходом единичиого плеча триггера предыдущего каскада и со счетным входом, подключенным к выходу схемы управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| Динамический триггер на моптранзисторах | 1976 |

|

SU657594A1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| СЧЕТНЫЙ ТРИГГЕР НА МДН-ТРАНЗИСТОРАХ | 1973 |

|

SU369717A1 |

| Генератор импульсов | 1975 |

|

SU570185A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

Авторы

Даты

1972-01-01—Публикация