1

Изобретение относится к области автоматики и вычислительной техники и может найти применение, в частности, при построении многоразрядных счетчиков и делителей частоты, а также может быть использовано в качестве разрядной ячейки статического регистра сдвига (при незначительной коррекции схемы).

Известен счетный триггер на МДП-транзисторах, содержащий триггер, выполненный на одном инверторе и двухвходовой схеме совпадения и инвертирования, первый вход которой подключен к выходу инвертора.

Недостатком известного устройства является его сложность, связанная с наличием двух динамических элементов памяти и двух шин входных сигналов (прямого и инверсного).

Предложенное устройство от известного отличается тем, что выход схемы совпадения и инвертирования подключен к стоку двух дополнительных МДП-транзисторов, причем исток первого из них подключен к затвору второго, а объединенный затвор первого и исток второго дополнительных МДП-транзисторов подключены ко второму входу схемы совпадения и инвертирования.

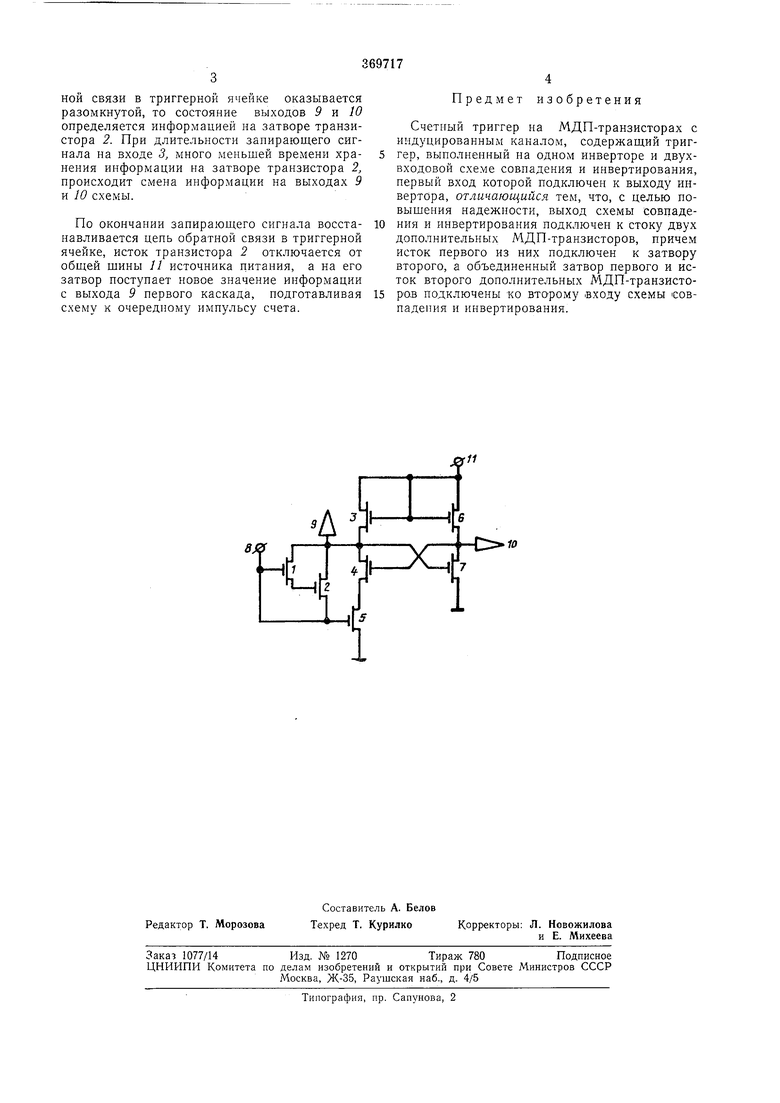

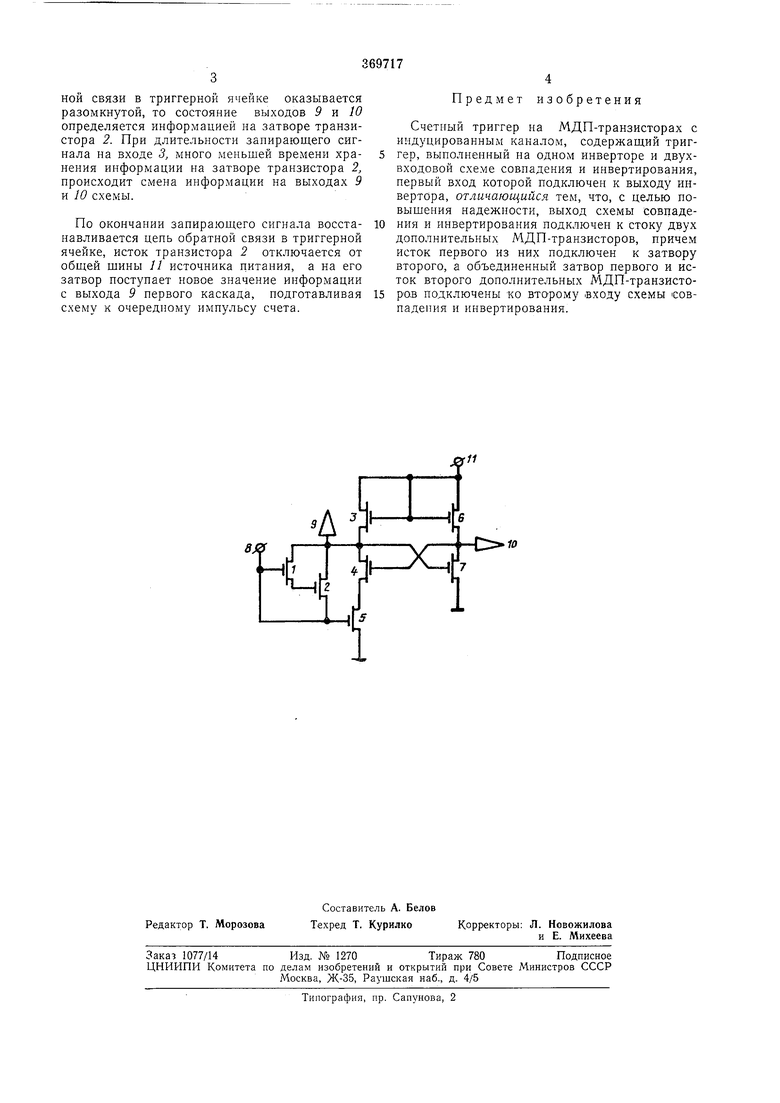

На чертеже показан предлагаемый счетный триггер. Полевые МДП-транзисторы 1 и 2 образуют схему динамического хранения информации, запоминающим элементом в которой

является конденсатор, образованный затвором транзистора 2, полевые МДП-транзисторы 3- 7 образуют схему статического триггера с замкнутой петлей обратной связи при действии на затворе транзистора 5 высокого уровня сигнала (если на затворе транзистора 5 действует низкий уровень сигнала, то он закрывается и размыкает цепь обратной связи в триггерной ячейке, которая превращается при этом в двухкаск-адную логическую схему); транзисторы 5 и 5 используются в качестве нагрузочных элементов триггерной ячейки. Кроме того, счетный триггер содержит щину 8 инверсных сигналов импульсов счета (вход схемы), выход 9 схемы (выход первого каскада), выход

10схемы (выход второго каскада) и щпну 11 источника питания Е.

В исходном состоянии в отсутствии импульсов счета на входе 8 схемы действует высокий потенциал, замыкающий петлю обратной связи в триггерной ячейке и пропускающий сигнал с выхода 9 первого каскада на затвор транзистора, не влияющего при этом на состояние плеч триггера.

При поступлении импульса счета потенциал на входе 8 схемы у.меньщается до нуля, закрывая транзисторы У и 5 и подключая исток транзистора 2 через внутреннее сопротивление генератора входных сигналов к общей щине

11источника питания Е. Так как цепь обратной связи в триггерной ячейке оказывается разомкнутой, то состояние выходов 9 и 10 определяется информацией на затворе транзистора 2. При длительности занирающего сигнала на входе 3, много меньшей времени хранения информации на затворе транзистора 2, происходит смена информации на выходах 9 и 10 схемы.

По окончании запирающего сигнала восстанавливается цепь обратной связи в триггерной ячейке, исток транзистора 2 отключается от общей шины 11 источника питания, а на его затвор поступает новое значение информации с выхода 9 первого каскада, подготавливая схему к очередному импульсу счета.

Предмет изобретения

Счетный триггер на МДП-транзисторах с индуцированным каналом, содержащий триггер, выполненный на одном инверторе и двухвходовой схеме совпадения и инвертирования, первый вход которой подключен к выходу инвертора, отличающийся тем, что, с целью повыщения надежности, выход схемы совпадения и инвертирования подключен к стоку двух дополнительных МДП-транзисторов, причем исток первого из них подключен к затвору второго, а объединенный затвор первого и исток второго дополнительных МДП-транзисторов подключены ко второму входу схемы совпадения и инвертирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Источник питания | 1980 |

|

SU900376A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Тактируемый @ -триггер | 1985 |

|

SU1267590A1 |

| @ -Триггер | 1983 |

|

SU1138929A1 |

| Триггер со счетным входом на взаимодополняющих МДП-транзисторах | 1989 |

|

SU1622925A1 |

80

0

Авторы

Даты

1973-01-01—Публикация