1

Изобретение относится к запоминающим устройствам.

В известном разрядном формирователе, содержанием входное устройство, выполненное на одно,каскадном усилителе, выходное устройство, .вылолненное на траизисторах р-п-р- и п-р-п- типов, резисторы, имеется межкаскадный трансформатор связи, который искажает фронты импульса записи, ограничивает быстродействие, увеличивает суммарную задержку и ограничивает степень возможной интеграции запамилающих устройств на МОП-транзисторах. Кроме того, разрядный формирователь с межкаскадной трансформаторной связью ле может быть непосредственно соединен с комплексом логических схем управления ло трактам заоиси и считывания.

В предлагаемом разрядном фор миров1ателе, с целью улучшения фронтов имлульса записи, .повышения быстродействия формирователя, обеспеченияНепосредственной связи с комплексом логических схем управления и повышения степени интеграции, входное устройство содержит схему «ИЛИ, выполненную на двух транзисторах п-р-л- типа, включенных по схеме с общим эмиттеро-м и общей коллекторной нагрузкой, входы которой соответственно соединены с входами записи и считывания и с резисторами смещения, Однокаскадный усилитель .выполнен по схаме с -общлм

эмиттером на транзисторе п-р-п- типа, база .которого через резистор соедияепа со входом записи, транзисторы выходного устройства соединены последовательно, причем к их коллекторам подсоединены нагрузочные резисторы, общая точка соединения которых подключена к щине разрядной литии, база транзистора п-р-л- типа соединена с выходом схемы «ИЛИ, база транзистора р-п-ртипа соединена через резистор связи с выходом однокаскадного усилителя, а переход база-эмиттер зашунтирован резистором утечки.

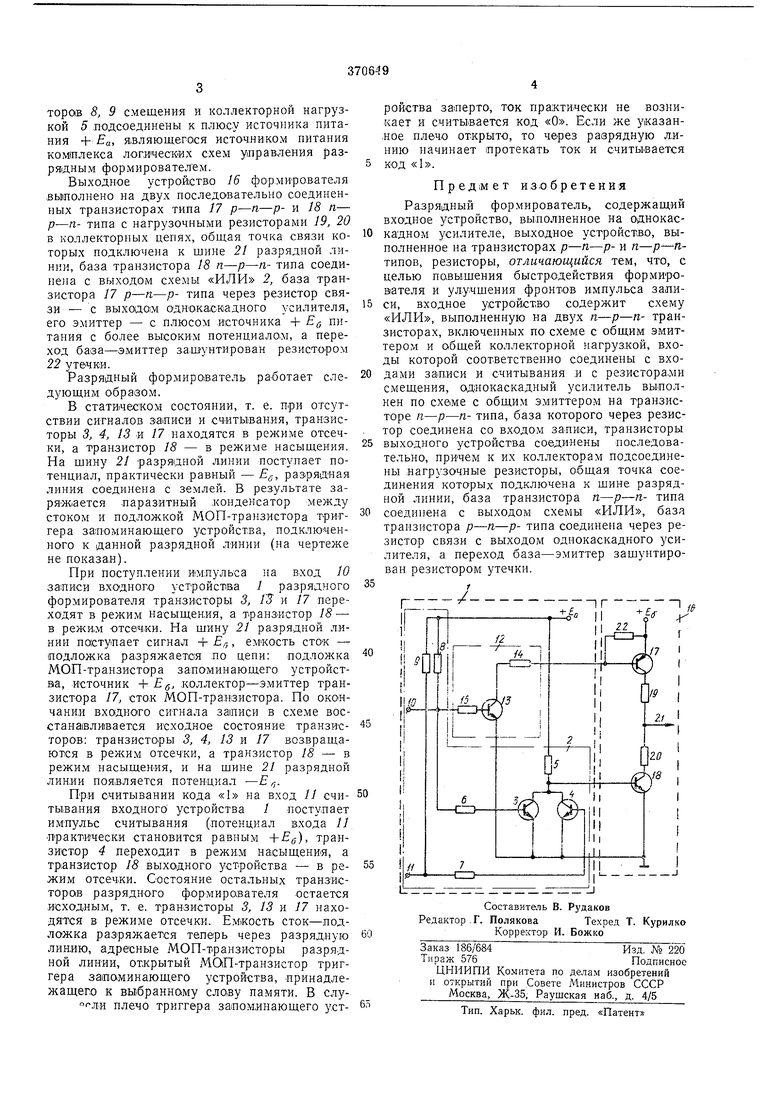

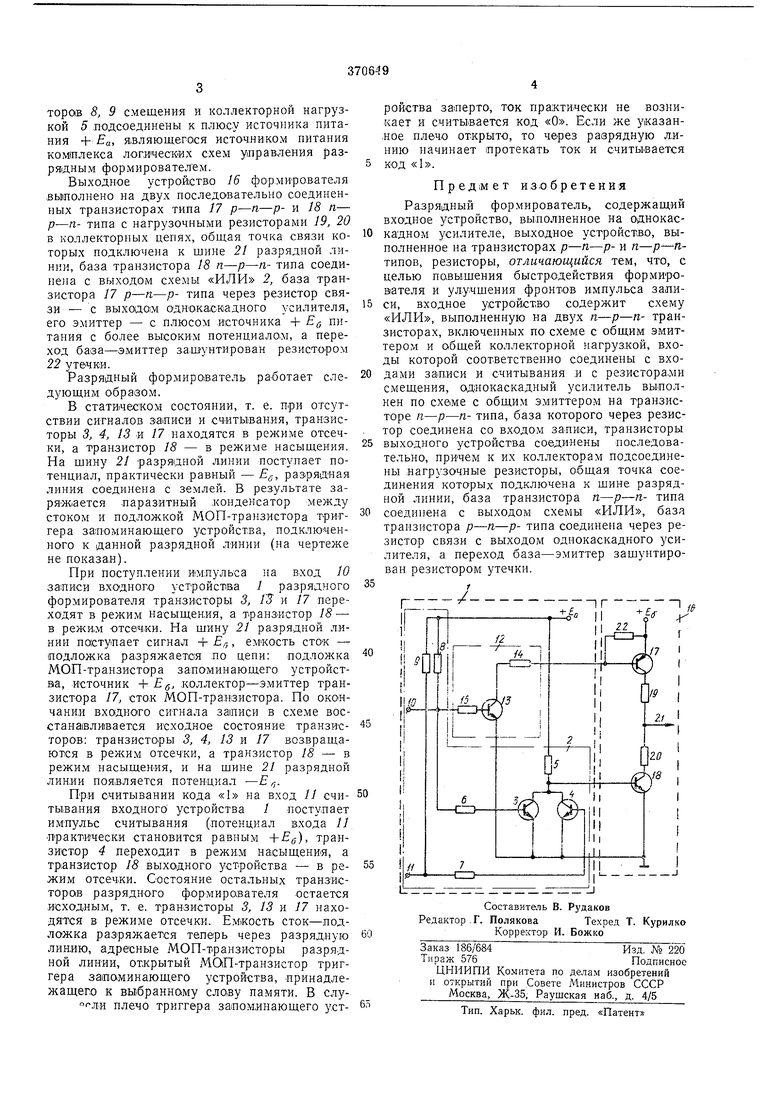

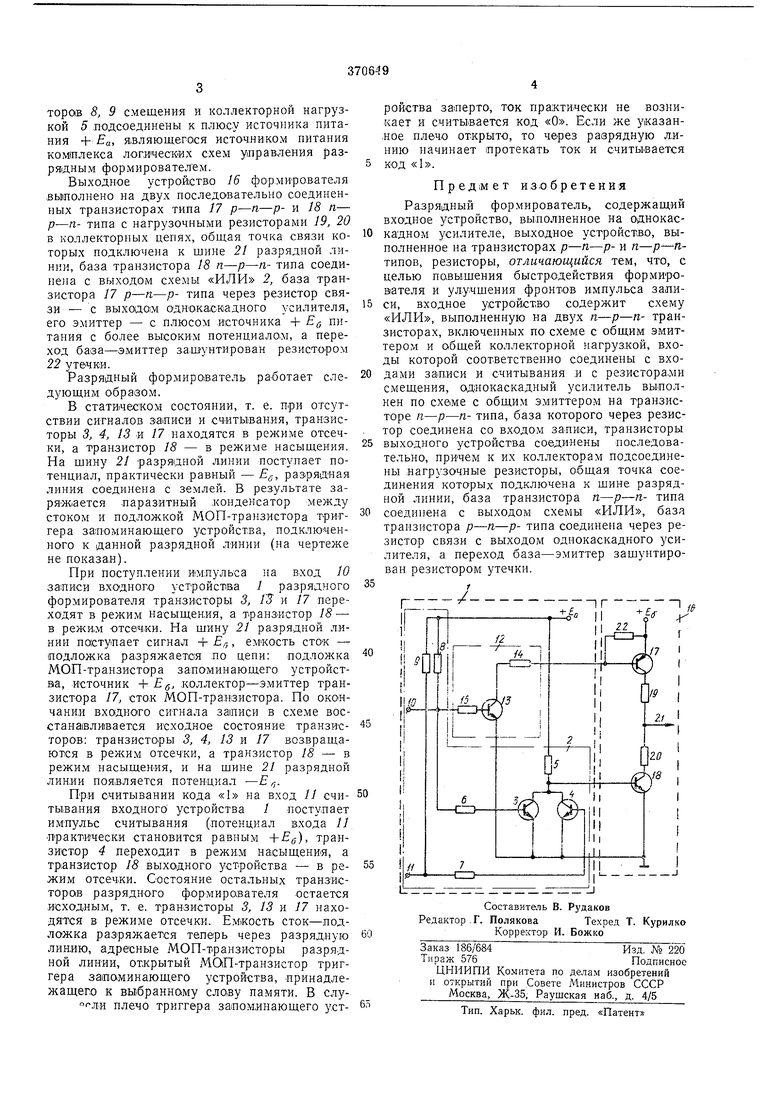

Па чертеже представлена принципиальная электрическая схема предлагаемого разрядного фор.м.ирователя.

Разрядный формирователь состоит из входного и выходного устройств. Входное устройство / формирователя содержит логическую схему «ИЛИ 2, выполненную на двух транзисторах 3, 4 п-р-п- типа с общей коллекторной нагрузкой 5, двумя базовыми резисторами 6, 7 и двумя резисторами 8, 9 смещения, общие точки связи которых соединены соответственно со входами записи 10 и считывания //, и одно.каскадный усилитель 12 сиь налов записи, выполненный по схеме с эмиттером на транзисторе 13 п-ррезистором 14 связи в коллектор резистором 15, вторым выво со входом 10 залиси. В

| название | год | авторы | номер документа |

|---|---|---|---|

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1972 |

|

SU327586A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ | 1973 |

|

SU377869A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ | 1973 |

|

SU381095A1 |

| Усилитель считывания | 1977 |

|

SU748505A1 |

| Формирователь импульсов | 1979 |

|

SU788361A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| Формирователь тока выборки дляблОКОВ пАМяТи | 1979 |

|

SU842954A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

Авторы

Даты

1973-01-01—Публикация