Изобретеи.ие относится « области запоМИнаюш.их устройств и 1может быть использовано в качестве устройства для формирования двухнолярных разрядных токов записи оперативного заиоминающего устройства.

Известиы устройства для формирования разрядных токов записи 1, 2.

Одно ИЗ них содержит входной каскад и выходное устройство, выполненное на транзисторах различного типа ироводимости 1J. Для этого устройства характерны большие аипаратурные затраты.

Из известных устройств иаиболее близким техническим решением к данному изобретению является устройство для формирования разрядных токов записи иоложительной и отрицательной полярности, содержаш.ее два формирователя импульсов тока, каждый из которых содержит входной и два выходных каскада, выполненные на транзисторах и резисторах 2,

Недостатками известного устройства для формирования разрядных токов заииси являются наличие в составе устройства двух трансформаторов, не поЗВОляюш,их получить полную интегральность устройства при изготовлении и ограЕичиваюш,их быстродействие, недостаточная помехоустойчивость устройства (ложное срабатывание транзисторов выходных каскадов), определяемая порогом

срабатывания выходных транзисторов, и необходимость ирименения двух источииков напряжения положительной .и отрицательиой полярности, каждый из которых используется только при формировании импульсного тока одной полярности.

Целью изобретения является повышение быстродействия и помехоустойчивости устройства, уменьшение иотребляемой мош,ности н

количества источников питаиия в нем.

Поставленная цель достигается тем, что иредлол енное устройство содерж-ит дополнительные каскады, каждый из которых выиолнен на двух транзисторах, база первого и

эмнттер второго транзисторов соединены с коллектором транзистора соответствуюш,его входного каскада, коллектор первого транзистора через первый резисгор соединен с niHнои питания, эмиттер подключен непосредственно к .коллектору второго транзисгора и через второй резистор к базе второго транзистора, которая через третий резистор соединена с шиной нулевого потенциала. Эмиттер первого и база второго транзисторов подключены

соответственно к базам транзисторов выходных каскадов, Коллекторы транзисторов первых выходных каскадов через четвертый резистор подключены к шине питания. Эмиттеры транзисторов вторых выходных каскадов

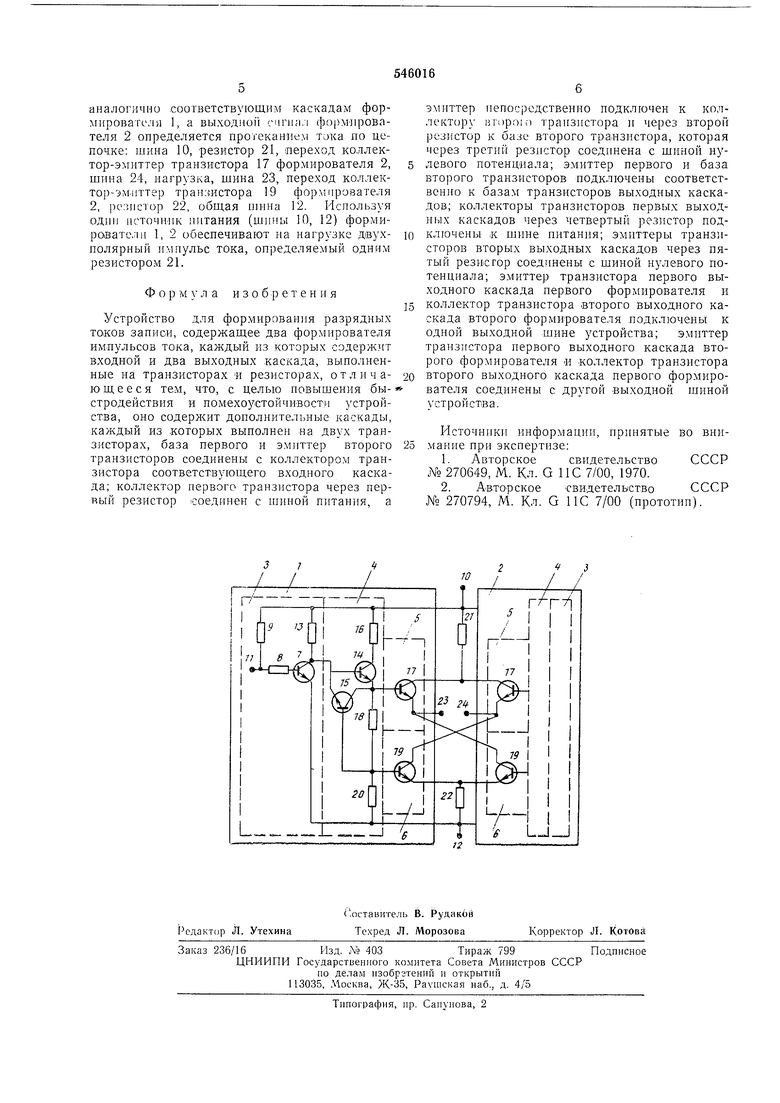

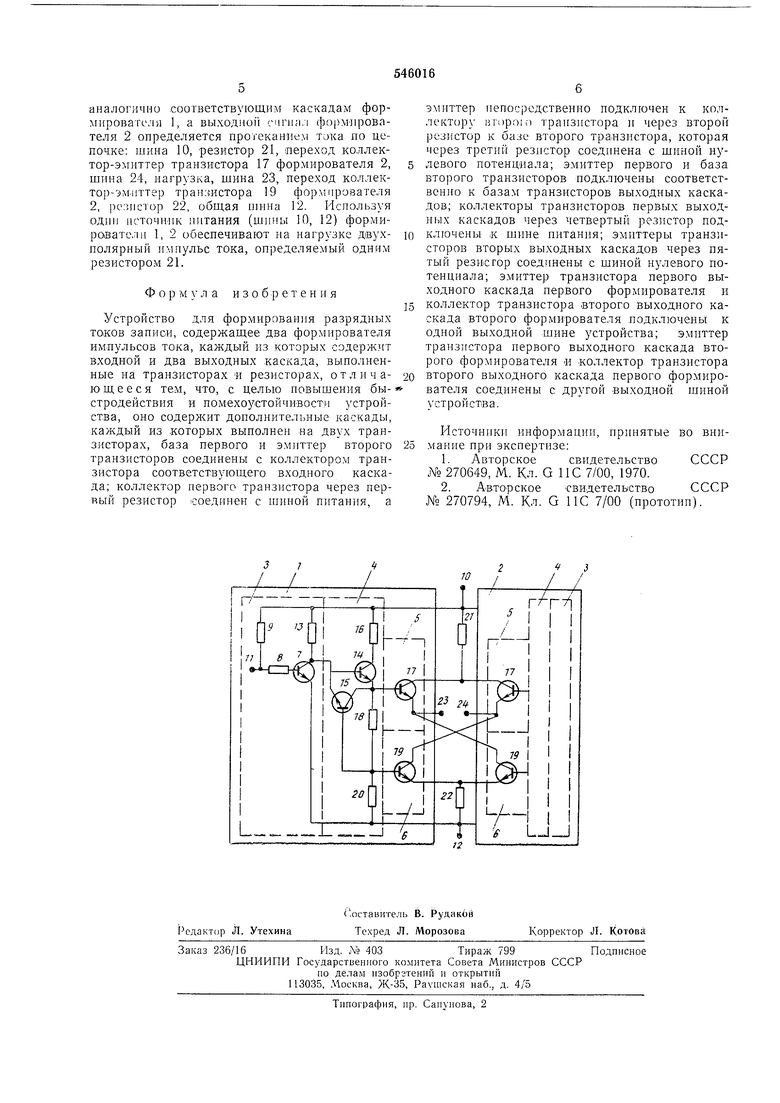

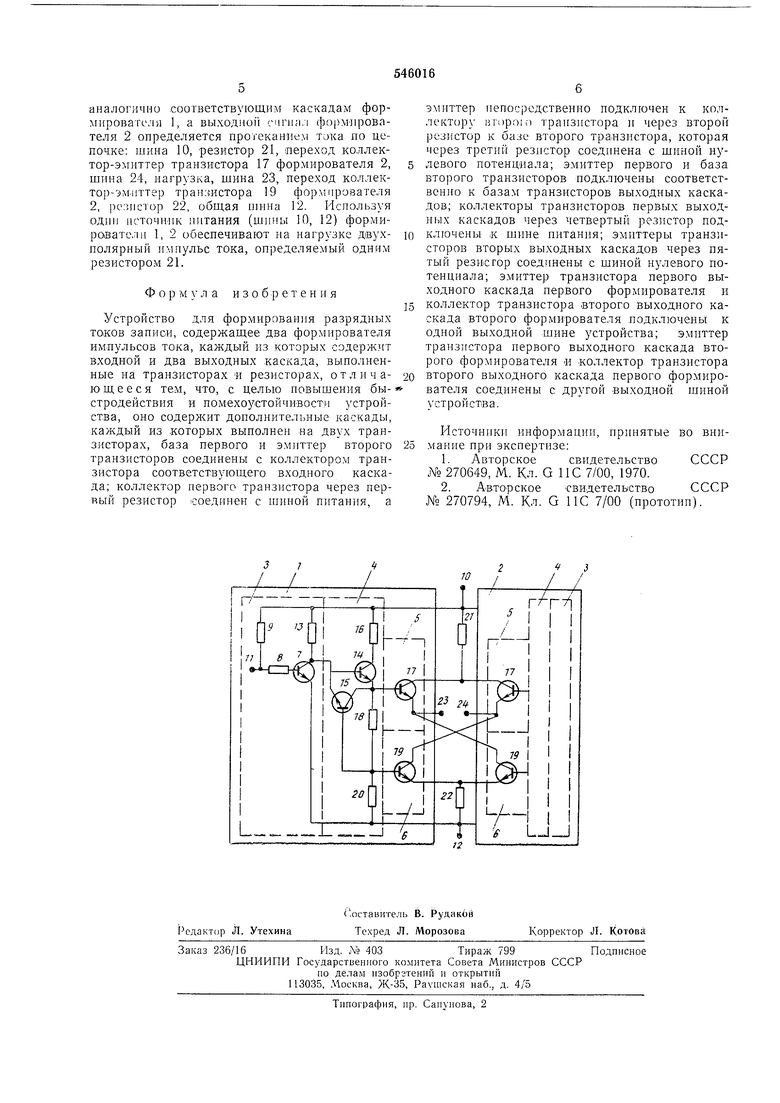

через пятый резистор соединены с шиной нулевого потенциала. Эмиттер транзистора первого выходного каскада первого формирователя и коллектор транзистора второго выходного каскада второго формирователя подключены к одной выходной шине устройства. Эммитер транзистора первого выходного каскада второго формирователя и коллектор т-ранзистора второго выходного каскада первого формирователя соединены с другой выходной иппюй устройсгоа. На чертеже представлеиа электрическая схема устройства для формирования разрядных токов записи. Устройство содержит два идентичных формирователя 1, 2 и.м.пульсов тока. Каждый формирователь 1 и 2 содержит одинаковые входной каскад 3, дополнительный каскад 4, первый 5 и второй 6 выходиые каскады. Фуикциоиальные связи в формирователях 1и 2 идентичны, поэтому приведено описание связей одного фор.мирователя. База транзистора 7 входного каскада 3 через последовательно соединенные резисторы 8 и 9 подключена к шине питания 10. Резисторы 8 и 9 соединены с входной шиной 11. Эмиттер транзистора 7 подключен к шине нулевого потенциала 12, а его коллектор через резистор 13 соединен с шиной 10 и непосредственно подключен к базе первого транзистора 14 и эмиттеру второго транзистора 15 каскада 4. Коллектор транзистора 14 через первый резистор 16 соединен с шиной 10, его эмиттер непосредственно подключен к коллектору транзистора 15 и базе транзистора 17 каскада 5, а через второй резистор 18 соединен с базами транзистора 15 и транзистора 19 каскада 6, которые через третий резистор 20 иодключены к шине 12. Коллекторы траизисторов 17 каскадов 5 формирователей 1 и 2 соединены и через четвертый резистор 21 подключены к шине 10. Эмиттеры транзисторов 19 каскадов 6 формирователей 1 и 2 соединены и через иятый резистор 22 подключены к шине 12. Э.миттер транзистора 17 формирователя 1 соединен с коллектором транзистора 19 формирователя 2и с одной выходной шиной 23, а эмиттер транзистора 17 формирователя 2 соединен с коллектором транзистора 19 формирователя 1 « с другой выходной шиной 24. Устройство работает следующем образом. В «сходном состоянии при отсутствии входных сигналов, додаваемых на базу транзистора 7 через резистор 8 формирователя 1 или формирователя 2, транзисторы 7 входных каскадов 3 открыты и работают в режиме насыщения за счет напряжения, подаваемого на их базы через резисторы 8 И 9. Напряжение коллектора транзистора 7, равное падению напряжения иа переходе коллектор-эмиттер, 1рикладывается к базе транзистора 14 и к амиттеру транзистора 15, обеспечивая работу транзисторов в режиме отсечки, поскольку его величины недостаточно для отпирания транзистора 14, а переход база-эмиттер транзистора 15 смещен в обратном направлении. За счет работы транзистора 14 в режиме отсечки ток через резисторы 16, 18 и 20 не протекает, и базы транзисторов 17 и 19 имеют нулевой потенциал, а транзисторы 17 и 19 закрыты. Таким образом, в исходном состоянии дополнительные ,и выходные каскады закрыты, и мощность не рассеивают. Входной сигнал отрицательной полярности поступает иа ишну 11 формирователя 1 или 2 в зависимости от того, какой полярности иеобходимо сформировать разрядный ток записи. При лодаче входного сигнала на шину 11 формирователя 1 формирователь 2 остается в исходном состоянии, и выходной сигнал на нагрузке формируется формирователем 1. При этом транзистор 7 закрывается, траизистор 14 открывается, и по цепочке шина 10, резистор 16, переход коллектор-эмиттер транзистора 14, резисторы 18, 20, шина 12 - протекает ток. Величины сопротивления резисторов 16, 18, 20 выбраны таким образом, что за счет падения напряжения обеспечивается смещение. необходимое для открывания транзисторов 17 и 19. В результате через нагрузку протекает ток ио цепочке: шина 10, резистор 21, переход коллектор-эмиттер транзистора 17 формирователя 1, шина 23, нагрузка, ши.на 24, переход коллектор-эмиттер транзистора 19 формирователя 1, резистор 22, общая шипа 12. Величины сопротивления резисторов 21 и 22 выбраны таким образом, что ток записи и соответственно рассеиваемая мощность определяются величиной сопротивления резистора 21. Таким образом, иеобходимым условием протекания тока через нагруЗКу является одновременное открывание транзисторов 17 и 19 одного формирователя, что иовышает помехоустойчивость устройства при отсутствии входного сигнала за счет уменьшения вероятности срабатывания двух транзисторов одновременно при помехе. Резистор, служащий для создания обратной связи и о,бщий для формирователей 1, 2, дополнительно повышает помехоустойчивость вторых выходных каскадов обоих формирователей. При прохождении тока записи через транзисторы 17, 19 происходит накопление заряда в базах. По окончании действия входного сигнала транзистор 7 открывается, а транзистор 14 закрывается. Потенциал эмиттера транзистора 15 понижается, а потенциал базы транзистора 15 становится выше .потенциала эмиттера за счет накопленного заряда в базах транзисторов 17, 19. В результате транзистор 15 откры вается только .на время процесса компенсаци накопленного заряда, обеспечивая низкоомную цепь разряда через открытый транзистор 7, повышая тем самым быстродействие устройства и улучшая параметры тока записи. При подаче входного сигнала на шину 11 формирователя 2 формирователь 1 остается в исходном состоянии, ;входной и дополнительный каскады формирователя 2 работают

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1977 |

|

SU748505A1 |

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1972 |

|

SU327586A1 |

| Устройство для формирования разрядных токов записи | 1988 |

|

SU1550581A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Формирователь импульсов | 1974 |

|

SU657601A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

Авторы

Даты

1977-02-05—Публикация

1975-05-19—Подача