1

Изобретение относится к запоминающим устройствам и может быть использовано в системах автоматики и вычислительной техники.

Цель изобретения - повьшение надежности устройства.

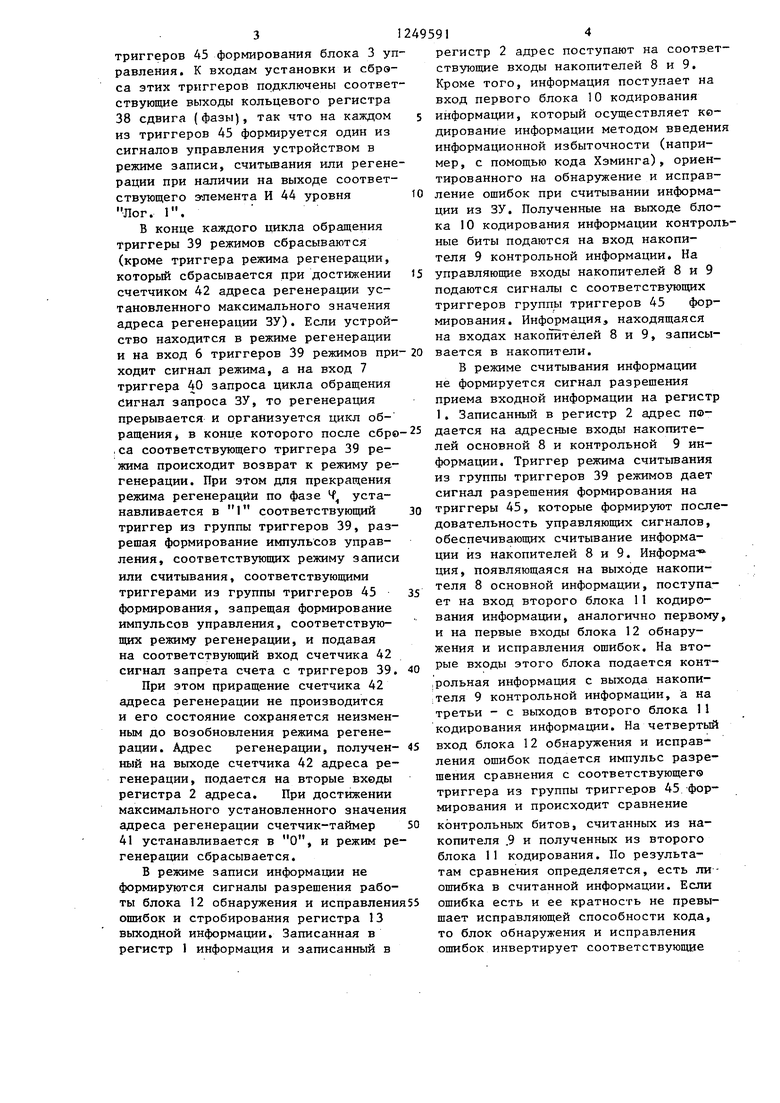

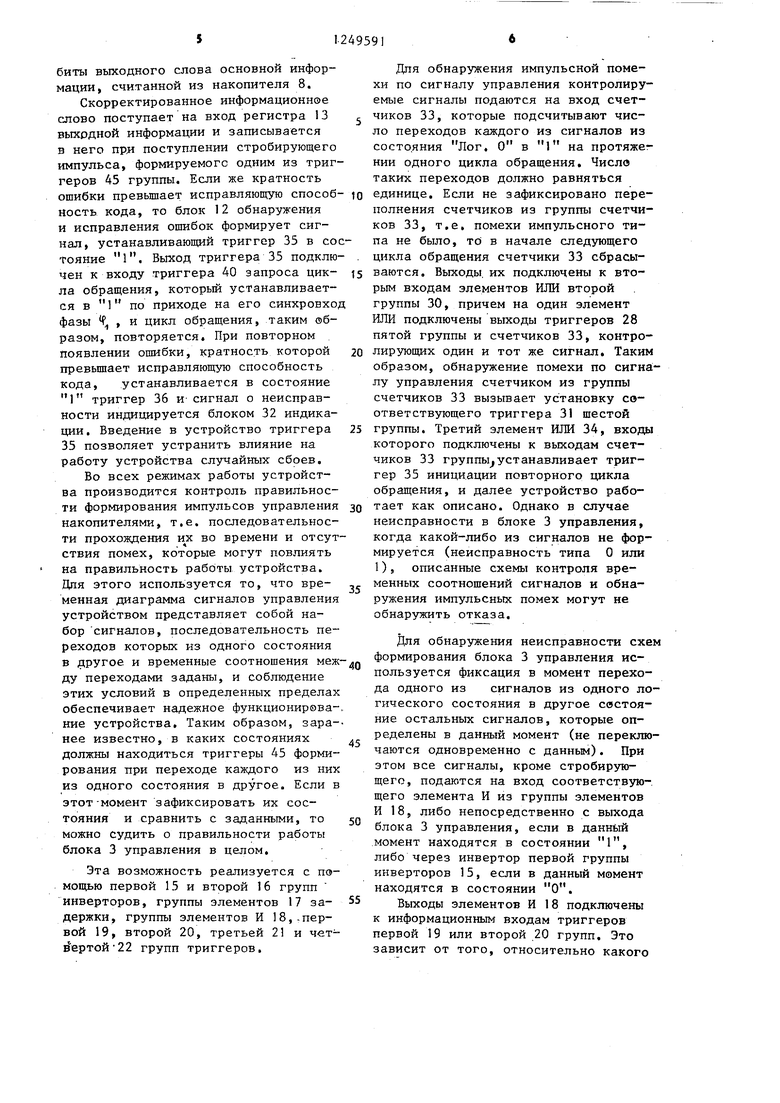

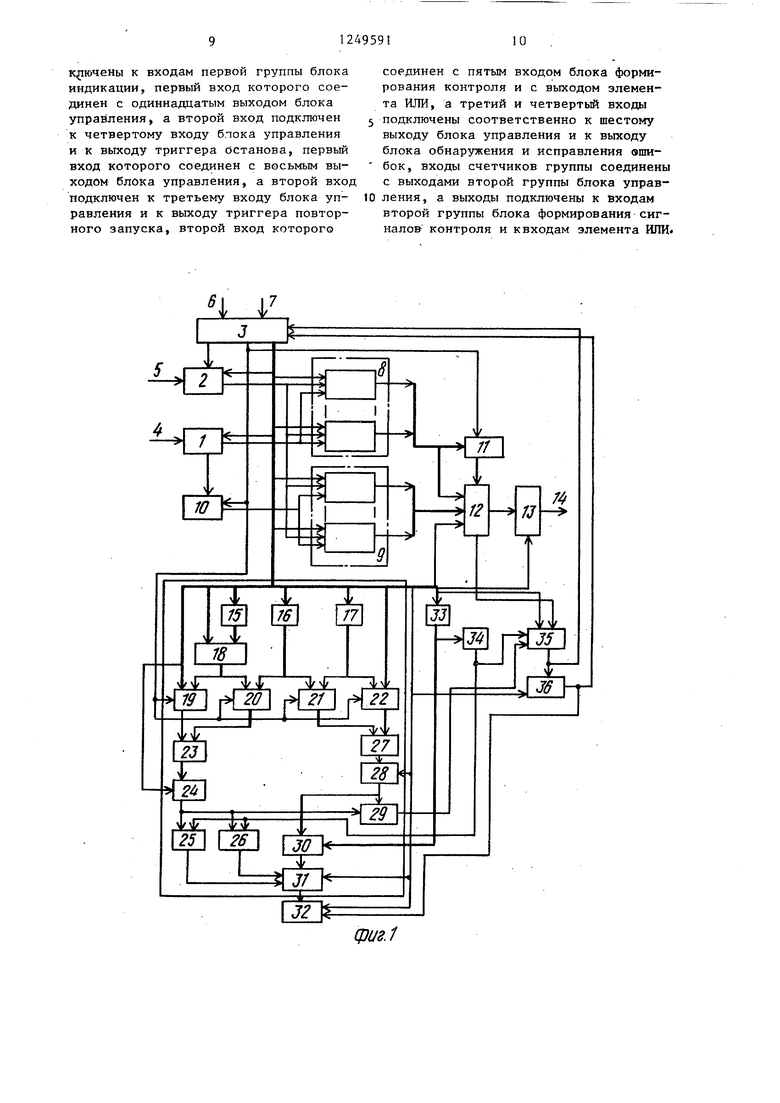

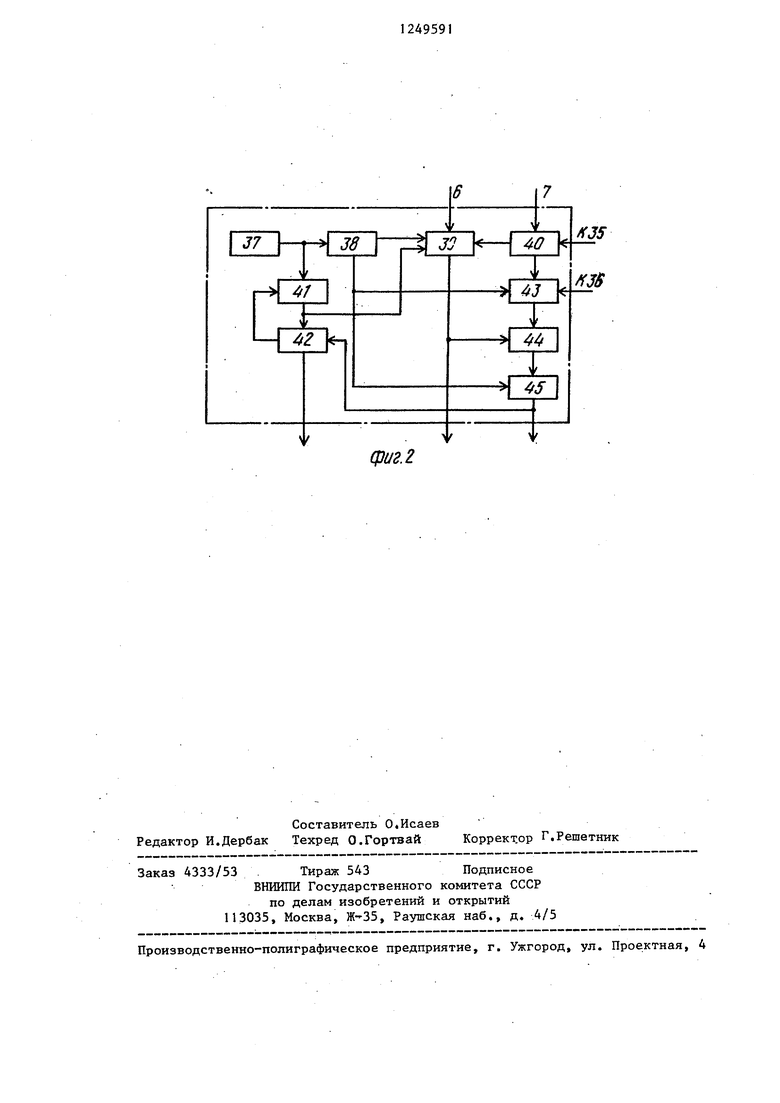

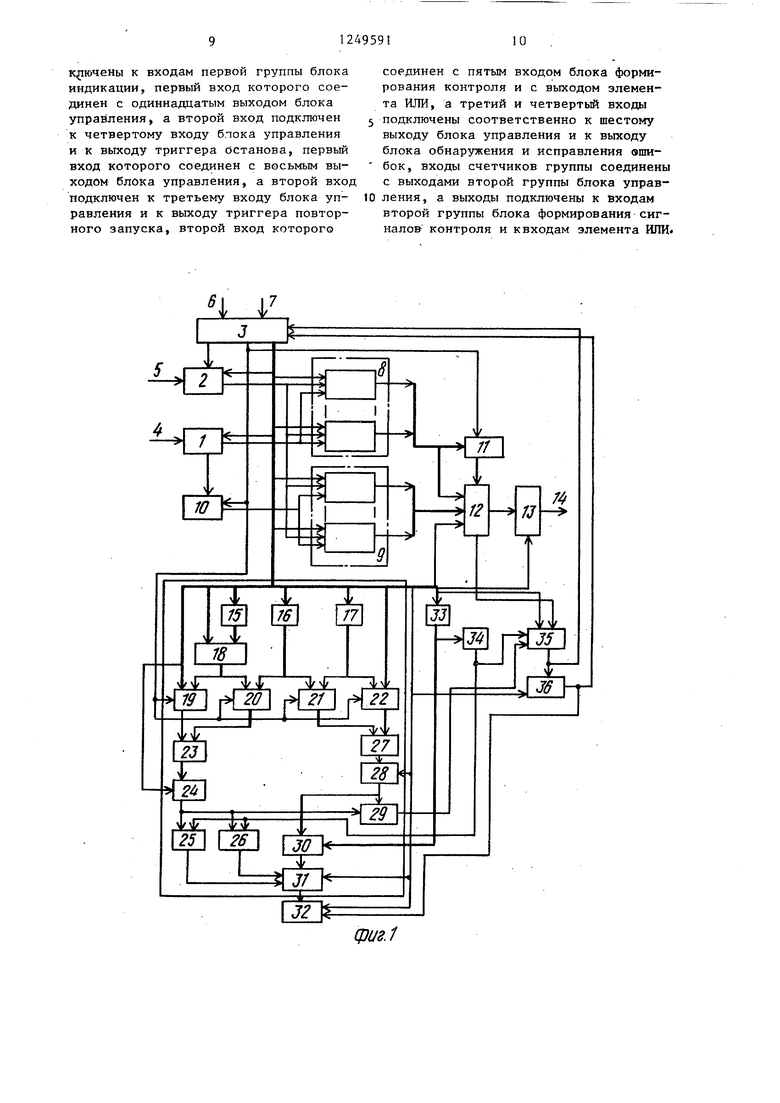

На фиг. 1 представлена схема запоминающего устройства с самоконтролем; на фиг. 2 - схема блока управления.

Запоминающее устройство (ЗУ) (фиг. 1) содержит входной регистр 1 информации, регистр 2 адреса, блок 3 управления, информационные 4, адресные 5 и управляющие 6 и 7 входы устройства, основной 8 и дополни- тельньш 9 накопители,первый 10 и второй 11 блоки кодирования, блок 12 обнаружения и исправления ошибок, регистр 13 выходной информации, выходы 14 которого являются информационными выходами устройства, первую 15 и вторую 16 группы инверторов,, группу элементов 17 задерлжи, группу элементов И 18, первую 19, вторую 20, третью 21 и четвертую 22 группы триггеров, первый элемент ИЛИ 23, триггер 24 отказа, первый 25 и второй 26 элементы И, первую группу элементов ИЛИ 27, пятую группу триггеров 28, второй элемент ИЛИ 29, вторую группу элементов ИЛИ 30, шестую группу триггеров 31, блок 32 индикации, группу счетчиков 33, третий элемент ИЛИ 34, триггер 35 повторного запуска и триггер 36 останова. Элементы 15-31 со связями представля ют блок самоконтроля.

Блок 3 управления (фиг, 2)содержит генератор 37 прямоугольных импульсов, кольцевой регистр 38 сдвига, группу триггеров 39 режимов, триггер 40 запроса цикла, счетчик- таймер 41 , счетчик 42 адреса регенерации, триггер 43 синхронизации цикла, группу элементов И 44 и группу триггеров 45 формирования.

Запоминающее устройство с самоконтролем работает следующим образом

На вход 6 группы триггеров 39 режимов блока 3 управления поступает сигнал установки режима (запись или считывание), на вход 5 регистра 2 адреса - адрес, по которому необходи МО произвести запись или чтение информации, а на вход 4 регистра 1 входной информации в режиме записи - входная информация. После этого на

495912

вход 7 триггера 40 запроса цикла об- ращения блока 3 управления поступает/ сигнал запроса ЗУ, который устанавливает этот триггер в состояние 0.

5 Генератор 37 прямоугольных импульсов блока 3 управления непрерывно вырабатывает прямоугольные импульсы за- данной частоты. Эти импульсы подаются на входы счетчика-таймера 41 и

to кольцевого регистра 38 сдвига блока. 3 управления.

Когда содержимое счетчика-таймера 41 достигает величины, эквивалентной периоду регенерации информации в ЗУ, 15 то на вход триггера 39 режимов подается сигнал установки режима регене рации. С помощью кольцевого регистра 38 сдвига блока 3 управления исходная последовательность импульсов генера20 тора 37 прямоугольных импульсов делится на несколько последовательностей импульсов меньшей частоты (фаз) , сдвинутых относительно друг друга по фазе на такт генератора и испвль25 зуемых для формирования импульсов управления накопителями 8 и 9, и сигналов управления другими блоками устройства, для которых соблюдаются временные соотношения, необходимые

30 для надежной работы устройства, Чис- л 0 фаз равно числу выходов кольцевв- го регистра 38 сдвига, и они имеют условную нумерацию от Ч до Ч , где п - число фаз, Последовательность

2J импульсов всех фаз между двумя последовательными импульсами Ч назьгаа- ется циклом формирования.

Последовательность импульсов, необходимая для работы устройства, фор4Q мируется следующим образом. Поскольку сигналы на перечисленные входы 4-7 устройства приходят в производительный момент времени, для синхронизации работы устройства их прием

4 на соответствующие регистры или триггеры осуществляется по фазе Ч , которая подается на их входы синхронизации. Одновременно фаза Ч , поданная на вход синхронизации триггера

5Q 43 синхронизации цикла блока 3 управления, устанавливает его в состояние 1,

Выход триггера 43 подключен к первым входам группы элементов И 44, 55 к вторым входам кото рых подключены соответствующие выходы триг геров 39 режимов. Выходы элементов И 44 под- .ключены к входам разрешения группы

триггеров 45 формирования блока 3 управления. К входам установки и сбрв- са этих триггеров подключены соответствующие выходы кольцевого регистра 38 сдвига (фазы), так что на каждом из триггеров 45 формируется один из сигналов управления устройством в режиме записи, считьшания или регенерации при наличии на выходе соответствующего элемента И 44 уровня Лог. 1.

В конце каждого цикла обращения Триггеры 39 режимов сбрасываются (кроме триггера режима регенерации, который сбрасывается цри достижении счетчиком 42 адреса регенерации установленного максимального значения адреса регенерации ЗУ). Если устройство находится в режиме регенерации и на вход 6 триггеров 39 режимов при ходит сигнал режима, а на вход 7 триггера 40 запроса цикла обращения сигнал запроса ЗУ, то регенерация прерывается и организуется цикл обращения в конце которого после сбр0 ,са соответствующего триггера 39 режима происходит возврат к режиму регенерации. При этом для прекращения режима регенерации по фазе Ч устанавливается в 1 соответствующий

триггер из группы триггеров 39, разрешая формирование импульсов управления, соответствующих режиму записи или считывания, соответствующими триггерами из группы триггеров 45 формирования, запрещая формирование импульсов управления, соответствующих режиму регенерации, и подавая на соответствующий вход счетчика 42 сигнал запрета счета с триггеров 39.

При этом приращение счетчика 42 адреса регенерации не производится и его состояние сохраняется неизменным до возобновления режима регенерации. Адрес регенерации, получен- ный на выходе счетчика 42 адреса регенерации, подается на вторые входы регистра 2 адреса. При достижении максимального установленного значени адреса регенерации счетчик-таймер 41 устанавливается в О, и режим регенерации сбрасывается.

В режиме записи информации не формируются сигналы разрешения работы блока 12 обнаружения и исправлени ошибок и стробирования регистра 13 выходной информации. Записанная в регистр 1 информация и записанный в

j Ю

15 20 25

0

5 0

5 0

5

регистр 2 адрес поступают на соответствующие входы накопителей 8 и 9. Кроме того, информация поступает на вход первого блока 10 кодирования информации, который осуществляет кодирование информации методом введения информационной избыточности (например, с помощью кода Хэминга), ориентированного на обнаружение и исправление ошибок при считывании информации из ЗУ. Полученные на выходе блока 10 кодирования информации контрольные биты подаются на вход накопителя 9 контрольной информации. На управляюш 1е входы накопителей 8 и 9 подаются сигналы с соответствующих триггеров группы триггеров 45 формирования. Информация, находящаяся на входах накопителей 8 и 9, записывается в накопители.

В режиме считывания информации не формируется сигнал разрешения приема входной информации на регистр 1. Записанный в регистр 2 адрес подается на адресные входы накопителей основной 8 и контрольной 9 информации. Триггер режима считьшания из группы триггеров 39 режимов дает сигнал разрешения формирования на триггеры 45, которые формируют последовательность управляющих сигналов, обеспечивающих считывание информации из накопителей 8 и 9. Информа ция, появляющаяся на выходе накопителя 8 основной информации, поступает на вход второго блока 11 кодирования информации, аналогично первому, и на первые входы блока 12 обнаружения и исправления ошибок. На вторые входы этого блока подается конт- .рольная информация с выхода накопи- :теля 9 контрольной информации, а на третьи - с выходов второго блока 1 кодирования информации. На четвертый вход блока 12 обнаружения и исправления ошибок подается импульс разрешения сравнения с соответствующего триггера из группы триггеров 45 -формирования и происходит сравнение

контрольных битов, считанных из накопителя .9 и полученных из второго блока 11 кодирования. По результатам сравнения определяется, есть ли- ошибка в считанной информации. Если ошибка есть и ее кратность не превышает исправляющей способности кода, то блок обнаружения и исправления ошибок инвертирует соответствующие

биты выходного слова основной информации, считанной из накопителя 8.

Скорректированное информационное слово поступает на вход регистра 13 выходной информации и записывается в него прл поступлении стробирующего импульса, формируемого одним из триггеров 45 группы. Если же кратность ошибки превьшает исправляющую способ- ность кода, то блок 12 обнаружения и исправления ошибок формирует сигнал, устанавливающий триггер 35 в сотояние 1. Выход триггера 35 подклю- чен к входу триггера 40 запроса цик- ла обращения, который устанавливается в 1 по приходе на его синхровход фазы % , и цикл обращения, таким образом, повторяется. При повторном появлении ошибки, кратность которой превьш1ает исправляющую способность кода, устанавливается в состояние 1 триггер 36 и- сигнал о неисправности индицируется блоком 32 индикации. Введение в устройство триггера 35 позволяет устранить влияние на работу устройства случайных сбоев.

Во всех режимах работы устройства производится контроль правильности формирования импульсов управления накопителями, т.е. последовательности прохождения во времени и отсутствия помех, которые могут повлиять на правильность раббты устройства. Дпя этого используется то, что вре- менная диаграмма сигналов управления устройством представляет собой набор сигналов, последовательность переходов которых из одного состояния в другое и временные соотношения меж ду переходами заданы, и соблюдение этих условий в определенных пределах обеспечивает надежное функционировакие устройства. Таким образом, заранее известно, в каких состояниях должны находиться триггеры 45 формирования при переходе каждого из них из одного состояния в другое. Если в этот-момент зафиксировать их состояния и сравнить с заданными, то можно судить о правильности работы блока 3 управления в целом.

Эта возможность реализуется с помощью первой 15 и второй 16 групп инверторов, группы элементов 17 за- держки, группы элементов И 18,-первой 19, второй 20, третьей 2) и чет- в ертой 22 групп триггеров.

Для обнаружения импульсной помехи по сигналу управления контролируемые сигналы подаются на вход счетчиков 33, которые подсчитывают число переходов каждого из сигналов из состояния Лог. О в I на протяжении одного цикла обращения. Число таких переходов должно равняться единице. Если не зафиксировано переполнения счетчиков из группы счетчиков 33, т.е. помехи импульсного типа не было, то в начале следующего цикла обращения счетчики 33 сбрасываются. Выходы, их подключены к вторым входам элементов ИЛИ второй группы 30, причем на один элемент ИЛИ подключены выходы триггеров 28 пятой группы и счетчиков 33, контролирующих один и тот же сигнал. Таким образом, обнаружение помехи по сигна лу управления счетчиком из группы счетчиков 33 вызывает установку соответствующего триггера 31 шестой группы. Третий элемент ИЛИ 34, входы которого подключены к выходам счетчиков 33 группы устанавливает триггер 35 инициации повторного цикла обращения, и далее устройство работает как описано. Однако в случае неисправности в блоке 3 управления, когда какой-либо из сигналов не формируется (неисправность типа О или 1)5 описанные схемы контроля временных соотношений сигналов и обнаружения импульсных помех могут не обнаружить отказа.

Для обнаружения неисправности схе формирования блока 3 управления используется фиксация в момент перехода одного из сигналов из одного логического состояния в другое состояние остальных сигналов, которые определены в данный момент (не переключаются одновременно с данным). При этом все сигналы, кроме стробирующего, подаются на вход соответствующего элемента И из группы элементов И 18, либо непосредственно с выхода блока 3 управления, если в данный момент находятся в состоянии 1, либо через инвертор первой группы инверторов 15, если в данный момент находятся в состоянии О.

Выходы элементов И 18 подключены к информационным входам триггеров первой 19 или второй 20 групп. Это зависит от того, относительно какого

перехода синхронизирующего сигнала реализованы условия проверки на элементе И 18: если относительно перехода сигнала из состояния О в состоя ние 1, то сигнал синхронизации на вход триггера из первой группы триггеров 19 подается непосредственно с выхода блока 3 управления. Если условия проверки реализованы для перехо- да сигнала из состояния 1 в состояние О, то сигнал синхронизации подается с выхода блока 3 управления через инвертор 16 второй группы на вход синхронизации триггера 20 вто рой группы. Выходы триггеров первой 19 и второй 20 групп подключены к входам первого элемента ИЛИ 23, и при фиксации нарушения условий, заданных элементами И 18, на тригге- pax первой 19 и второй 20 групп, триггер 24 устанавливается в состояние 1, что приводит к установке триггера 35, и далее устройство работает как описано.

Первый 25 и второй 26 элементы И предназначены для определения характера зафиксированной сбойной ситуации. Если установлен триггер 24 отказа и зафиксировано переполнение хотя бы одного из счетчиков 33, то это означает импульсную помеху по одному из сигналов управления. При этом на вь1ходе первого элемента И 25 появляется уровень Лог. 1 и уста- навливается соответствующий триггер 31 щестой группы. Если установлен триггер 24 и нет переполнения счетчиков 33 группы, то это означает отказ одного из формирующих триггеров 45 блока 3 управления. При этом на выходе второго элемента И 26 появляется уровень Лог. 1 и устанавливает соответствующий триггер 31 шестой группы.

В начале повторного цикла обраще ния все триггеры (кроме триггеров 35 и 36j, счетчики схемы контроля и регистр выходной информации устанавливаются в исходное состояние.

Триггеры 35 и 36, кроме этого, устанавливаются в исходное состояние при нажатии кнопки Сброс (не показана) или в конце цикла обращения (по фазе 4), при условии, что при обращении не обнаружено ошибки. Формула изобретения

Запоминающее устройство с самоконтролем, содержащее регистр адреса

5 Ю 15 0 5

0 Q 5

0

выходы которого соединены с адресными входами основного и дополнительного накопителей, а входы первой группы являются адресными входами устройства, регистр входной ин формации, входы первой группы которого являются информационными входами устройства, а выходы подключены к .информационным входам основного накопителя и к входам первой группы первого блока кодирования, выходы которого соединены с информационными входами дополнительного накопителя, блок управления, первый и второй входы которого являются управляющими входами устройства, выходы первой группы подключены к входам второй группы регистра адреса, выходы второй группы соединены с управляющими входами основного и дополнительного накопителей, а первый, второй, третий, четвертый и пятый выходы блока управления подключены соответственно к входам первого и второго блоков кодирования, регистра адреса, регистра входной информации, регистра выходной информации, блока обнаружения и исправления ошибок, входы первой и второй групп которого соединены соответственно с выходами и входами группы второго блока кодирования,- входы третьей группы подключены к выходам дополнительного накопителя, а выходы группы блока обнаружения и исправления ошибок подключены к входам первой группы регистра выходной информации, выходы которого являются информационными выходами устройства, входы второй группы второго блока кодирования соединены с выходами основного накопителя, отличающееся тем, что, с целью повьш1ения надежности устройства, в него введены блок формирования сигналов контроля, группа счетчиков, элемент ИЛИ, триггер повторного запуска, триггер останова и блок индикаций, причем входы первой группы блока самоконтроля подключены к выходам вт®- рой группы блока управления, первый, второй, третий и четвертый входы соединены соответственно с первым, седьмым, девятым и десятым выходами блока управления, выход блока формирования сигналов контроля соединен с первым входом триггера повторного запуска, а выходы первой группы подк ючены к входам первой группы блока индикации, первый вход которого соединен с одиннадцатым выходом блока упрайления, а второй вход подключен к четвертому входу блока управления и к выходу триггера останова, первый вход которого соединен с восьмым выходом блока управления, а второй вход подключен к третьему входу блока управления и к выходу триггера повторного запуска, второй вход которого

соединен с пятым входом блока формирования контроля и с выходом элемента ИЖ, а третий и четвертый входы

5 подключены соответственно к шестому выходу блока управления и к выходу блока обнарз ения и исправления вши бок, входы счетчиков группы соединены с выходами второй группы блока управ10 ления, а выходы подключены к Входам второй группы блока формирования сигналов контроля и квходам элемента ИЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920848A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

Изобретение относится к запоми- нающим устройствам и может быть использовано в системах автоматики и вычислительной техники. Целью изобретения является повьшёние надежности устройства. Устройство содержит регистры адреса входной и выходной информации, основной и дополнительный накопители, первьй и второй блоки кодирования, блок обнаружения и исправления ошибок, блок самоконтроля, группу счетчиков, элемент ИЛИ, триггер повторного запуска, триггер останова и блок индикации. Во всех режимах работы устройства блоком самоконтроля осуществляется проверка правильности формирования импульсов управления накопителями путем фиксации логических переходов импульсов и сравнения их с заданными. Для обнаружения помех по сигналам управления используются счетчики, подсчитывающие количество логических переходов контролируемых сигналов в течение цикла обращения к ОЗУ. При обнаружении помехи или при неправильном формировании импульсов управления инициируется повторный запуск цикла ОЗУ путем установки соответствующего триггера. Если неисправность повторяется, устройство останавливается и индицируется неисправная цепь управления. 2 ил. с « СО со ел

Ч ,

фив.1

фиг. 2

| Электроника, 1981, т | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU385319A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-07—Публикация

1985-01-07—Подача