Предлагаемое устройство может быть нсиользовано в электроизмерительной и вычислительной технике для нреобразования изменяющихся во времени иенрерывных сигналов в цифровой код.

Известны аналого-цифровые преобразователи (АЦП) перезарядного уравновешивания, содержащие сравнивающее устройство, преобразователи кода в напряжение, регистр триггеров разрядов со схемой переноса единицы, логические схемы, тактовый генератор и распределитель тактовых импульсов.

Известные устройства обладают недостатком, заключающимся в большом количестве дополнительных элементов.

С целью уменьщения динамической погрешно сти И упрощения схемы в предлагаемом преобразователе выход сравнивающего устройства соединен с одним из входов дополнительных схем совпадения младших разрядов, вторые входы которых подключены- к выходам распределителя тактовых импульсов, управляющий коррекцией в данном разряде, а выходы дополнительных схем совпадения соединены с соответствующими входами схемы переноса едишщы предыдущих разрядов, включенных в младших разрядах регистра триггеров, причем выходы распределителя тактовых импульсов, управляющие коррекцией

младщих разрядов, подключены к соответствующим входам второго преобразователя кода в напряжение, выход которого соединен со схемой суммирования напряжений преобразователей кода в напряжение.

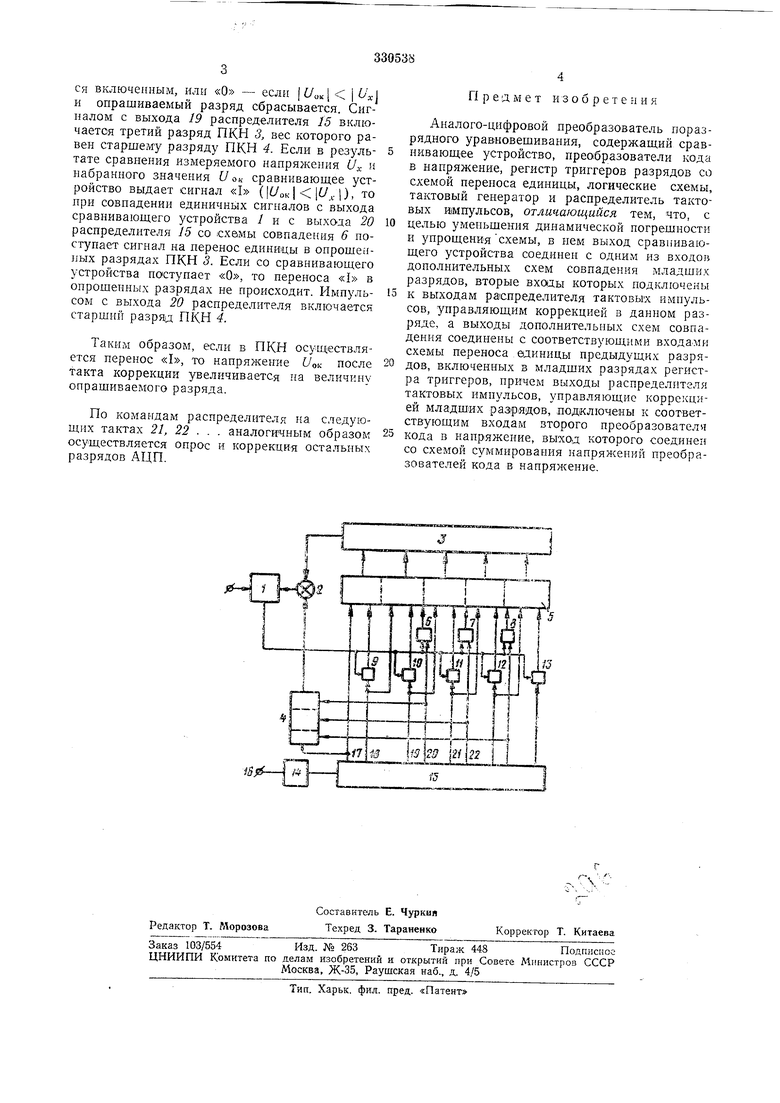

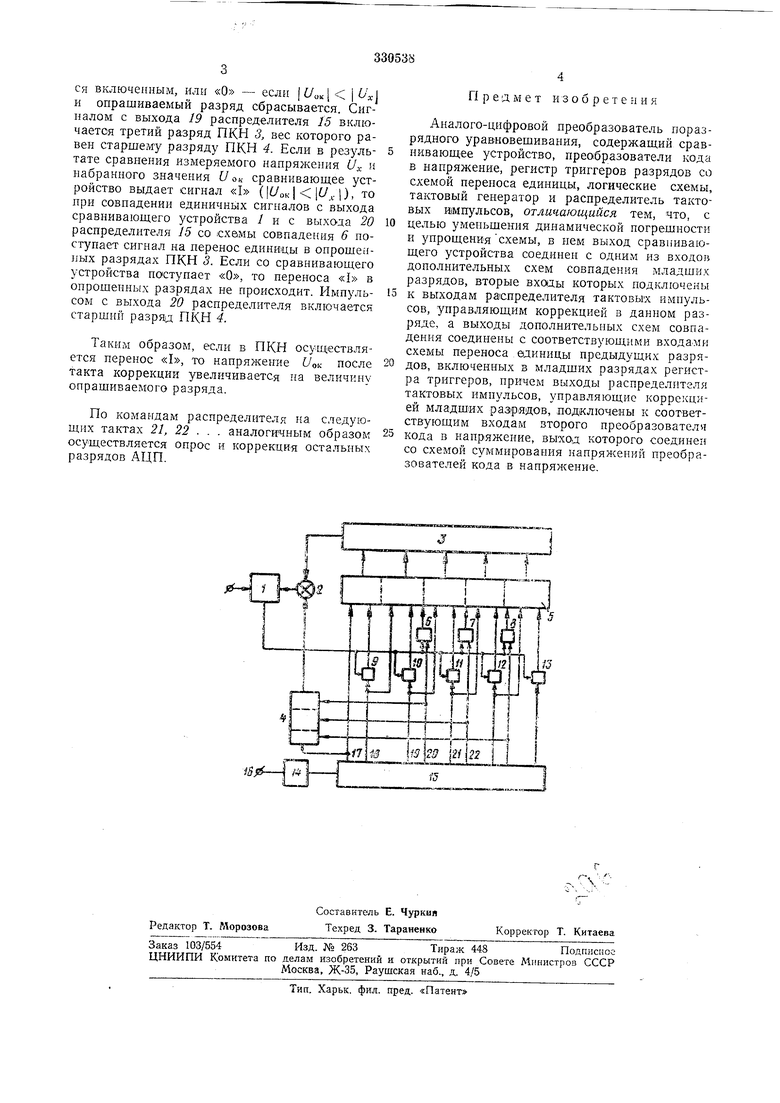

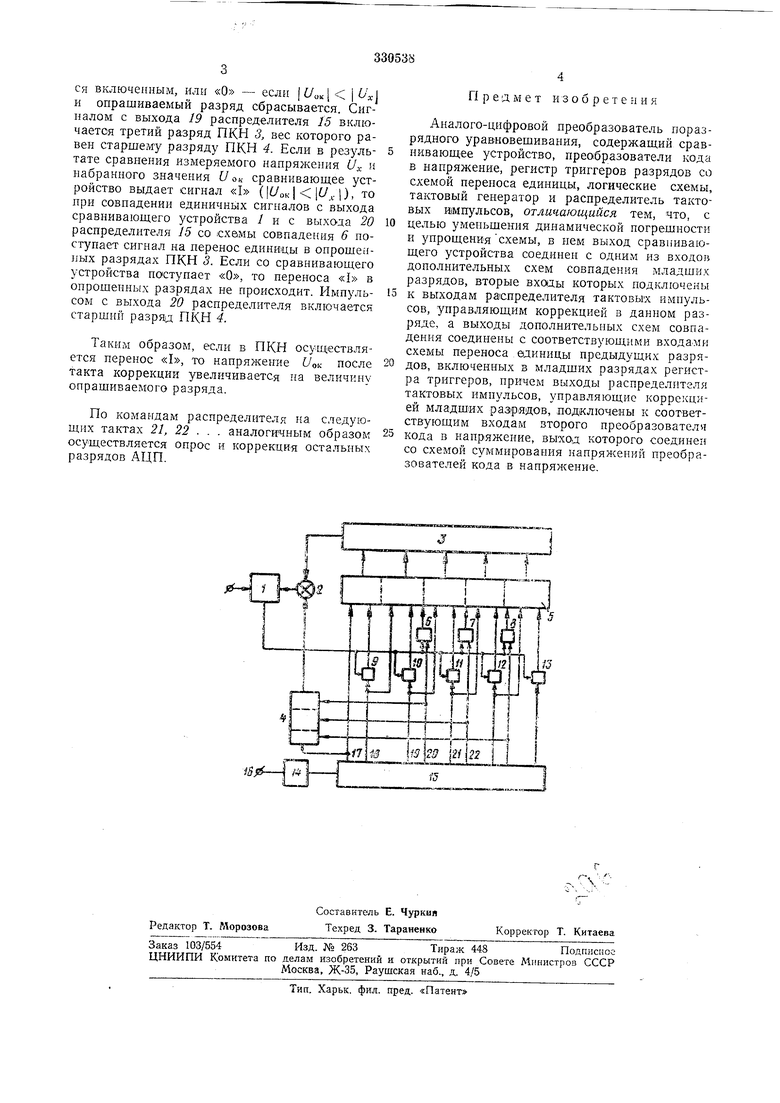

На чертеже приведена схема нредлагае.мого аналого-цифрового ир.еобразователя в пятиразрядный ДВОИЧНЫЙ код.

Устройство содержит сравнивающее устройство 1, схему суммирования напряжений 2, преобразователи кода в напряжение (ПКН) 3 И 4, регистр триггеров разрядов со схемой переноса единицы 5, схемы совпадений 6-13, тактовый генератор 14, распределитель тактовых импульсов 15.

По сигналу запуска на входе 16 с генератора тактовых импульсов 14 поступают импульсы па распределитель 15, который напрял ением на выходе 17 устанавливает все элементы распределителя в исходное состояние, при этом включаются все разряды ПКН 4 л старший разряд ПКН 3, подключая к схеме суммирования напряжепия UK и и„, соответствующие включенным разрядам.

Затем с выходов 18 и 19 распределптеля 15 поступают тактовьге импульсы и производится опрос старших разрядов, при этом со сравнивающего устройства / поступает сигнал еслп И опрашиваемый разряд остается включенным, или «О - если I Ua и опрашиваемый разряд сбрасывается. Сигналом с выхода 19 распределителя 15 включается третий разряд ПКН 3, вес которого равен старшему разряду ПКН 4. Если в результате сравнения измеряемого напряжения U н набранного значения U ок сравнивающее устройство выдает сигнал «I .(), то при совпадении единичных сигналов с выхода сравнивающего устройства / и с выхо-да 20 распределителя 15 со схемы совпадения 6 поступает сигнал на перенос единицы в опрощенпых разрядах ПКН 3. Если со сравнивающего устройства поступает «О, то переноса «I в опрощенных разрядах ие происходит. Импульсом с выхода 20 распределителя включается старщий разрад ПКН 4. Таким образом, если в ПКН осуществляется перенос «I, то напряжение UOK после такта коррекции увеличивается па величину опращиваемого разряда. По командам распределителя на следующих тактах 21, 22 . . . аналогичным образом осуществляется опрос и коррекция остальных разрядов АЦП. Предмет изобретения Аналого-цифровой преобразователь поразрядного уравновешивания, содержащий сравниваюЩве устройство, преобразователи кода в напряжение, регистр триггеров разрядов со схемой переноса единицы, логические схемы, тактовый генератор и распределитель тактовых И1мпульсов, отличающийся тем, что, с целью уменьшения динамической погрешности и упрощения схемы, в нем выход сравнивающего устройства соединен с одним из входов дополнительных схем совпадения младщих разрядов, вторые входы которых подключены к выходам распределителя тактовых импульсов, управляющим коррекцией в данном разряде, а выходы дополнительных схем совпадения соединены с соответствующими входа ми схемы переноса единицы предыдущих разрядов, включенных в младщих разрядах регистра триггеров, причем выходы распределителя тактовых импульсов, управляющие коррекцией младщих разрядов, подключены к соответствующим входам второго преобразователя кода в напряжение, выход которого соединен со схемой суммирования напряжений преобразователей кода в напряжение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Г. Г. ЖИВИЛОБ; ::-.:;B::^ji03MAfl'1!^'а:гни кя,;^^'^?-кАЯ'Ч.'г. | 1972 |

|

SU324705A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1972 |

|

SU439913A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СО СТАТИСТИЧЕСКОЙ ОБРАБОТКОЙ РЕЗУЛЬТАТОВ | 1973 |

|

SU389623A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

дэЧ

.

Даты

1972-01-01—Публикация