1

Изобретение относится к технике преобразования аналоговых сигналов в цифровые.

Известен аналого-цифровой преобразователь с коррекцией в процессе поразрядного уравновешивания-,.

Недостатком его является невозможность преобразования сигналов за /i-тактов.

Известен аналого-цифровой преобразователь с коррекцией динамических погрешностей, содержащий сравнивающие устройства, преобразователь кодов в напряжение, блок контрольных напряжений, схемы суммирования напряжений, логические схемы, генератор импульсов, распределитель тактовых импульсов, дополнительный преобразователь кода в напряжение, аналоговый выход которого подключен к схеме суммирования компенсирующих напряжений, а цифровой выход соединен с входом цифрового сумматора, на другой вход которого подключен цифровой выход основного преобразователя кода в напряжение .

Недостатком устройства является невысокое быстродействие за Л-тактов.

Целью изобретения является повышение быстродействия.

Цель достигается тем, что в аналогоцифровой преобразователь, содержащий основной и дополнительный преобразователи кодов в напряжения с подключенными поразрядно регистрами, распределитель тактовых импульсов, вход которого соединен с выходом генератора тактовых импульсов, а его выходы соединены с входами разрядов регистров основного и дополнительного преобразователей кода в напряжения, аналоговый выход первого из которых соединен с входом первого блока

сравнения и первыми входами блоков суммирования и вычитания, а аналоговый выход дополнительного преобразователя кода в напряжение соединен с вторыми входами блоков суммирования и вычитания, при

этом выход последнего подключен к входу второго блока сравнения, а выход блока суммирования - к входу третьего блока сравнения, сигнальный вход которого соединен с входной клеммой и с сигнальными входами первого и второго блоков сравнения, введены логический элемент НЕ, блок кодирования старших разрядов и логический блок коррекции, при этом входы блока кодирования старщих разрядов соединены с соответствующими входами логического блока коррекции и с выходами первого и третьего блоков сравнения непосредственно и через логический элемент НЕ - с выходом второго блока сравнения и

с другими входами логического блока

коррекции, соответствующие выходы которого подключены к счетным входам и к входам установки нулей младших разрядов регистра основного преобразователя кода в напряжение, входы установки единиц старших разрядов которого соединены с соответствующими входами блока кодирования старших разрядов и с входами установки единиц регистра дополнительного преобразователя кода в напряжение, причем соответствующие выходы блока кодирования старших разрядов соединены с входами установки нулей 2K-J-1 старшего разряда и с входами установки единиц 2К старшего разряда регистра основного преобразователя кода в напряжение (где К - натуральный ряд чисел), вес второго разряда которого выбран равным весу младшего разряда регистра дополнительного преобразователя кода в напряжение, а блок кодирования старших разрядов содержит логические элементы И и 2И-ИЛИ, равные числу старших разрядов регистра основного преобразователя кода в напряжение, при этом соответствующие входы логических элементов 2И-ИЛИ соединены с соответствующими входными клеммами и со вторыми входами логических элементов И, первые входы которых подключены к входным клеммам, логический блок коррекции содержит логический элемент НЕ и логические элементы И, входы которых соединены с соответствующими входными клеммами и между собой.

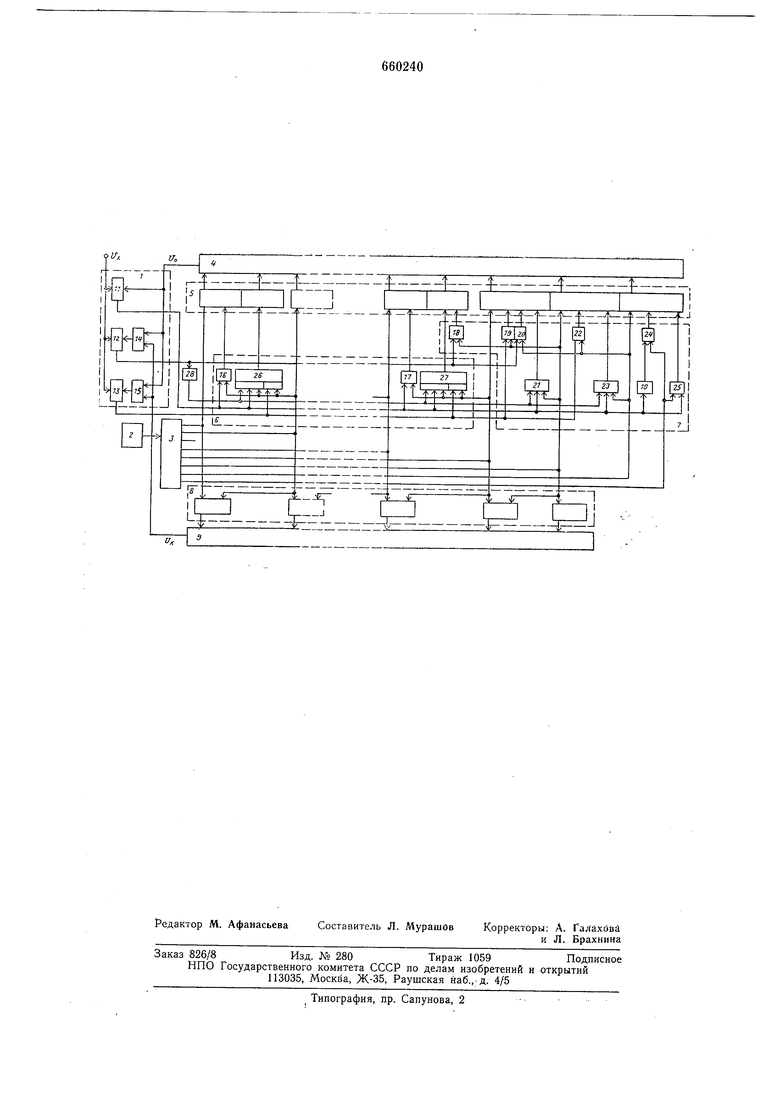

На чертеже изображена функциональная схема однннадцатиразрядного устройства.

Устройство содержит узел сравнения 1, генератор 2 тактовых импульсов, распределитель 3 тактовых импульсов, основной преобразователь 4 кода в напряжение, регистр 5 (реверсивный счетчик), блок 6 кодирования старших разрядов, логический блок 7 коррекции, дополнительные регистр 8 кода и преобразователь 9 кода в напряжение, элемент НЕ 10. Узел сравнения 1 состоит из блоков сравнения 11, 12 и 13 и аналоговых блоков вычитания 14 и блока сложения 15. Устройство содержит также элементы совпадения 16-25, элементы 2И-ИЛИ 26 и 27 и элемент НЕ 28.

Выходы распределителя 3 соединены непосредственно со входами установки «единиц младших разрядов регистра 5 и старших из пар в группе старших разрядов регистра 5, со входами регистра 8, через логический блок 6 кодирования старших разрядов со входами установки «нуля старших из пар и входами установки «единиц младших из пар разрядов регистра 5 и через логический блок 7 коррекции со счетными входами сложения и вычитания и входами установки «нуля младших разрядов регистра 5. Выходы блока сравнения соединены с управляющими входами блоков 6 и 7.

Импульсом Ао устанавливается начальное состояние, при этом старшие разряды регистров 5 и 8 устанавливаются в «единицы, все остальные разряды регистров5и8 устанавливаются в «нулевое положение (цепь установки «нулей па чертеже не показана). Вес старшего разряда дополнительного ННК соответствует весу младшего разряда из старшей пары разрядов основного регистра 5, т. е. 10-му разряду основного пнк.

Блоки сравнения И, 12 и 13 вырабатывают сигналы «1, если , Ux Uo-UK, , и «О, если , - UK, Uy: iUo-i-UK соответственно.

Импульсами Xi ... Хц производится поразрядное уравновешивание старших разрядов по два за один такт соответственно 11-ый разряд и 10-ый разряд, 9-ый разряд и 8-ой разряд, 7-ой разряд и 6-ой разряд, 5-ый разряд и 4-ый разряд.

Если в момент х , то через элемент совпадения 16 11-ый разряд регистра 5 сбрасывается в нулевое состояние, если , то 11-ый разряд остается в единичном состоянии.

Импульсом х 10-ый разряд, младший из старшей пары разрядов регистра 5, устанавливается в единичное состояние через элемент 2И-ИЛИ 26 в случае, если t/ но импульс х устапавливает в единичное Lo+бк, или Uo Ux Ua-Uy. Одновременно импульс Xi устанавливает в единичное состояние старший разряд следующей пары основного регистра 5, выключает старший разряд и включает следующий по порядку разряд дополнительного регистра 8, вес которого соответствует весу младшего из пары определяемых в следующем такте разрядов основного ПНК, т. е. 8-го разряда.

Импульсом х производится поразрядное уравновешивание 5 и 4-го разрядов, установка в единичное состояние 3-го разряда регистра 5 и включение 3-го разряда дополнительного регистра 8.

На последних тактах xs, х, Х7 происходит коррекция процесса поразрядного уравновешивания. В момент действия х напряжение UK соответствует четырем единицам младшего разряда. Если и Ux-.Uo-UK, то происходит коррекция на 4 единицы в сторону уменьшения, 3-й разряд регистра 5 остается в единичном состоянии, так как элемент совпадения 21 закрыт потенциалом с элемента НЕ 28 (отличие от ННК без коррекции на +4 единицы). Импульс Xs проходит через элемент совпадения 18 на счетный вход вычитания в 4 разряд регистра 5 и уменьшает число в регистре на 8 единиц (отличие от ПНК без коррекции на -8 единиц, а результирующее отличие от ПНК без коррекции на -4 единицы).

Если и , то происходит коррекция на 4 единицы в сторону увелнчения. Так как элемент 21 закрыт потенциалом с узла сравнения 1, то импульс х ис проходит па вход установки нуля 3-го разряда, но проходит через элемент 19 на счетный вход сложения 3-го разряда регистра 5 (отличие от ПНК без коррекции на 4-4 единицы).

Если UQ-.UX-., то коррекция не происходит. Импульс Х5 не проходит через элементы 21, 19 и 18 так как имеются запрещающиеся потенциалы с элементов 10, 13 и 12 соответственно, 3-ий разряд регистра 5 остается в единичном состоянии.

Если UQ-UK UX UO, то коррекция не происходит. Элементы 18 и 19 закрыты нотенциалами с элементов 12 и 13 соответственно. Импульс Х5 проходит через элемент совпадения 21 и устанавливает 3-ий разряд регистра 5 в нулевое состояние.

Аналогично имнульс Хе производит коррекцию па ±2 единицы младшего разряда в случае необходимости.

Импульсом Х5 в дополнительном регистре 8 включается и остается включенным до конца измерения младший разряд, имеющий равный вес со 2-м разрядом основного регистра.

Последний импульс с распределителя импульс Xj при устанавливает в нулевое состояние 1-ый разряд регистра, при поступает на счетный вход 1 разряда регистра 5 через элемент 24 и производит коррекцию на -f 1.

Следовательно, имнульс Ху изменяет число в регистре 5 на ±1 единицу.

Таким образом, преобразование напрял ения в одиннадцатиразрядный код с коррекцией динамических ошибок происходит вместо И тактов за 7 тактов.

Формула изобретения

1. Аналого-цифровой преобразователь с коррекцией динамических погрешностей, содержащий основной и дополнительный преобразователь кода в напряжение с подключенными поразрядно регистрами, распределитель тактовых импульсов, вход которого соединен с выходом генератора тактовых импульсов, а его выходы соединены с входами разрядов регистров основного и дополнительного преобразователей кода в напряжения, аналоговый выход первого из которых соединен с входом первого блока сравнения и нервыми входами блоков суммирования и вычитания, а аналоговый выход дополнительного преобразователя кода в напряжения соединен с вторыми входами блоков суммирования и вычитания, прн этом выход последнего подключен к входу

второго блока сравнения, а выход блока суммирования - к входу третьего блока сравнения, сигнальный вход которого соединен с входной клеммой и с сигнальными 5 входами первого и второго блоков сравнения, отличающийся тем, что, с целью повышения быстродействия, в него введены логический элемент НЕ, блок кодирования старших разрядов и логический блок корQ рекции, при этом входы блока кодирования старших разрядов соединены с соответствующими входами логического блока коррекции и с выходами первого и третьего блоков сравнения непосредственно и через

5 логический элемент НЕ - с выходом второго блока сравнения и с другими входами логического блока коррекции, соответствующие выходы которого подключены к счетным входам и к входам установки нулей

Q младших разрядов регистра основного преобразователя кода в напряжение, входы установки единиц старших разрядов которого соединены с соответствующими входами блока кодирования старших разрядов и

5 с входами установки единиц регистра дополнительного преобразователя кода в напряжение, причем соответствующие выходы блока кодирования старших разрядов соединены с входами установки нулей 2К+1

Q старшего разряда и с входами установки единиц 2К старшего разряда регистра, основного преобразователя кода в напряжение (где К - натуральный ряд чисел), вес второго разряда которого выбран равным

- весу младшего разряда регистра дополнительного преобразователя кода в напряжение.

2. Преобразователь по п. 1, отличающийся тем, что блок кодирования стар,, ших разрядов содерл ит логические элементы И и 2И-ИЛИ, равные числу старших разрядов регистра основного преобразователя кода в нaпpялveниe, при этом соответствующие входы логических элементов 2И-ИЛИ соединены с соответствующими

5 входными клеммами и со вторыми входами логических элементов И, первые входы которых подключены к входным клеммам, логический блок коррекции содержит логический элемент НЕ и логические элемен0

ты И, входы которых соединены с соответствующими входными клеммами и между собой.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство № 324705, кл. Н ОЗК 13/17, 1970.

2.Авторское свидетельство № 439913, кл. Н ОЗК 13/17, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1981 |

|

SU974572A1 |

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1976 |

|

SU657607A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU330538A1 |

Авторы

Даты

1979-04-30—Публикация

1976-08-01—Подача