Изобретение относится к области электроизмерительной и вычислительной техники и может быть использовано для преобразования изменяющихся во времени непрерывных сигналов в цифровой код.

Известны аналого-цифровые преобразователи (АЦИ) поразрядного уравновешивания, содержащие сравнивающие устройства, преобразователи кода в напряжение, регистр триггеров разрядов со схемами сложения н вычитания «единицы, логические схемы, тактовый генератор и раснределитель тактовы.ч импульсов.

Однако известиые устройства обладают малым диапазоном коррекции дина.мических погрсшностей и увеличенным обидим временем преобразования.

С целью уменьшения динамической ногрешиости и увеличения быстродействия в предлагаемом устройстве одни вход второго сравниБающего устройства иодключеи к источнику измеряемого сигнала, второй вход соедниен со схемой суммирования ианряжепия преобразователей кода в напряжепие; выходы сравннвающнх устройств соединены со входами дополнительных схем совпадения, к другим входам которых подключены выходы распределителя тактовых импульсов; один выходы дополнительных схем совпадения соединены со схемами сложения, а вторые - со

схемами вычитания «сднннцы, включенными в младшнх разрядах регистра триггеров; управляющпе входы второго преобразователя кода в напряжение, соответственно, соедпнены с шннамп распределителя тактовых импульсов младших разрядов преобразователя.

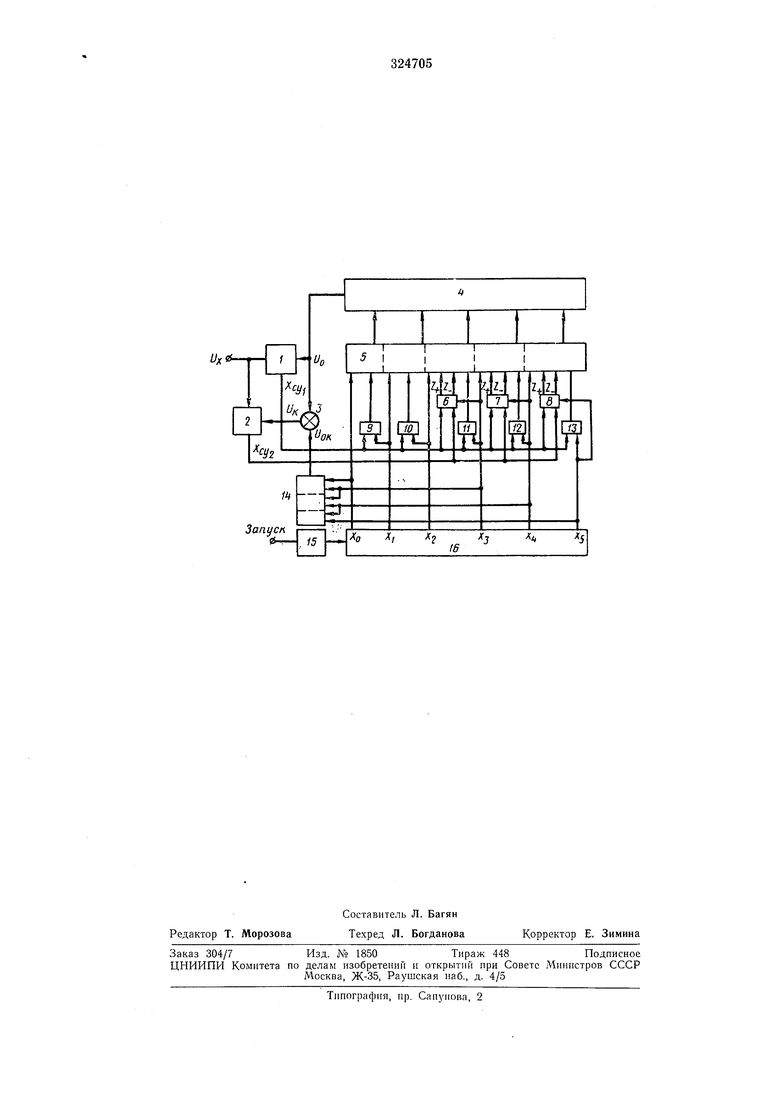

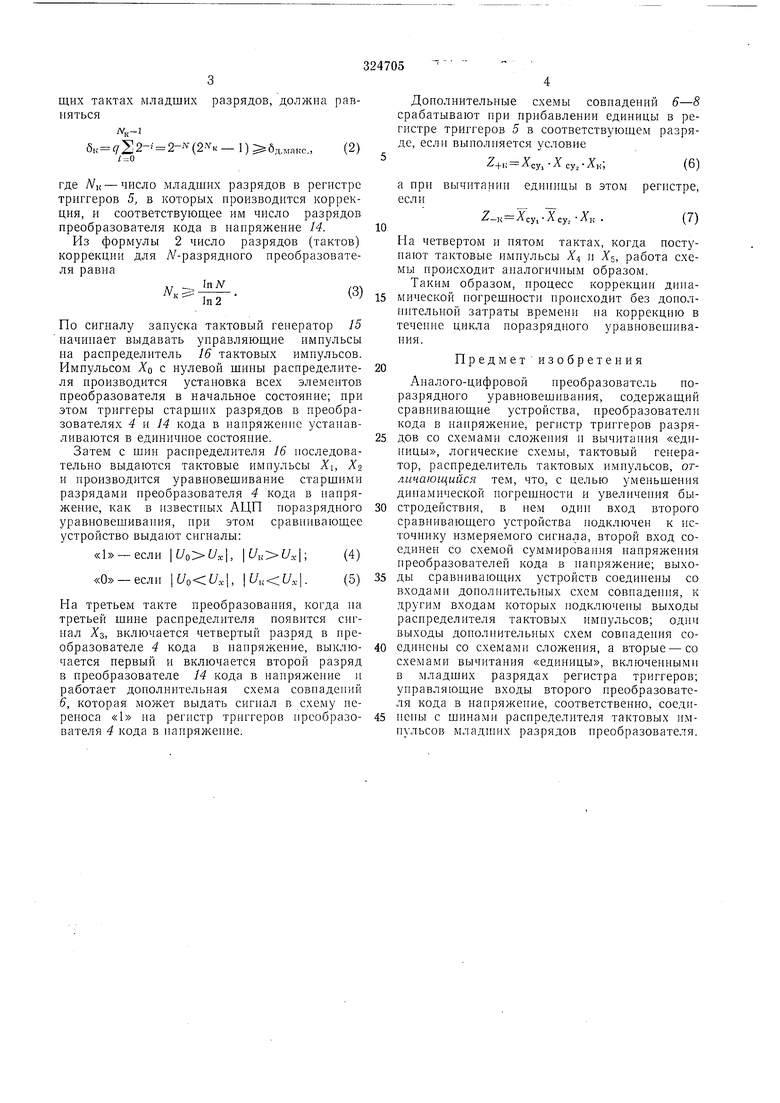

На чертеже представлена схема предлагаемого аналого-цифрового преобразователя поразрядного уравновешнвання.

Устройство содержнт сравннвающне устройства / и 2, схему 3 суммирования наиряжеиия, нреобразователь 4 кода в нанряжение, регистр триггеров 5 разрядов со схемой сложения и вычитання единицы, дополнительные схемы совнадений 6-8, схемы совпаденпй 9-13, преобразователь 14 кода в напряжение, тактовый генератор /5 и распределитель 16 тактовых импульсов.

Для обеспечения заданной точности преобразования за время одного такта донустнмо изменение входного сигнала па величину одного кванта q, максимальная велнчнпа дипамнческой погрешности, которая может возникнуть, равняется

бд.„акс. (.-V -1)9 (;V - 1) . (1);

Для обеснечения коррекции этой д1Н1амнческой ногреншостн максимальная величина нанряжения Уок, выработанная преобразователем 14 кода в паиряженне на корректирующих тактах младших разрядов, должна равнятьсябк 922- 2-Л-( 1) бд.макс.,(2) где NK - число младших разрядов в регистре триггеров 5, в которых производится коррекция, и соответствуюш,ее им число разрядов преобразователя кода в напряжение 14. Из формулы 2 число разрядов (тактов) коррекции для /V-разрядного преобразователя равна По сигналу запуска тактовый генератор 15 начинает выдавать управляющие импульсы на распределитель 16 тактовых импульсов. Импульсом Хо с пулевой шины распределителя производится установка всех элементов преобразователя в начальное состояние; при этом триггеры старших разрядов в преобразователях 4 и 14 кода в напряжение устанавливаются в единичное состояние. Затем с шин распределителя 16 последовательно выдаются тактовые импульсы Xi, Xz и производится уравновешивание старшими разрядами нреобразователя 4 кода в нанряжение, как в известных АЦП поразрядного уравновешиваиия, ири этом сравиивающее устройство выдают сигналы: «1 -если , .-|; (5) «О -если ,, ,|. На третьем такте преобразования, когда на третьей шине распределителя появится сигнал Xz, включается четвертый разряд в преобразователе 4 кода в нанряженне, выключается первый и включается второй разряд в преобразователе 14 кода в напряжение и работает дополнительная схема совпадений 6, которая может выдать сигпал в схему нереиоса «1 иа регистр триггеров нреобразователя 4 кода в иапряже1п-1е. Дополнительные схемы совпадений 6-8 срабатывают при прибавлении единицы в регистре триггеров 5 в соответствующем разряде, если выполняется условие Z+i; су.-Хк,(6) а нри вычитании единицы в этом регистре, если уVу -к - cyiAcy, -Ajj . Иа четвертом и нятом тактах, когда поступают тактовые импульсы Х и Х,, работа схемы происходит аиалогичиым образом. Таким образом, процесс коррекции дипамической погрешности происходит без дополнительной затраты времени на коррекцию в течение цикла поразрядного уравновешивания. Предмет изобретения Аналого-цифровой преобразователь поразрядного уравновешивания, содержащий сравнивающие устройства, иреобразователи кода в наиряжение, регистр триггеров разрядов со схемами сложеиия и вычитания «единицы, логические схемы, тактовый генератор, распределитель тактовых имиульсов, отличающийся тем, что, с целью уменьшения динамической погрешности и увеличения быстродействия, в нем одии вход второго сравнивающего устройства иодключен к источнику измеряемого сигиала, второй вход соединен со схемой суммирования напряжения преобразователей кода в напряжеиие; выходы сравиивающих устройств соединены со входами дополиительных схем совпадения, к другим входам которых подключены выходы распределителя тактовых импульсов; одн) выходы дополнительных схем совпадения соединены со схемами сложения, а вторые - со схемами вычитания «единицы, включенными в младших разрядах регистра триггеров; управляющие входы второго преобразователя кода в напряжение, соответственно, сосдииены с шинамн распределителя тактовых импульсов младншх разрядов нреобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1972 |

|

SU439913A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU330538A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

| Преобразователь напряжения в код | 1980 |

|

SU884126A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| ТЕЙТМ- 1П 11^f vu4«*'pr'-'&i! Ti Ari!. -^t-i-^b»SHbJiKOTEaA | 1969 |

|

SU254223A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1969 |

|

SU256858A1 |

Даты

1972-01-01—Публикация