1

Изобретение относится к вычислительной технике, и в частности, к структурам цифровых вычислительных систем.

Известны вычислительные системы, содержащие п блоков обработки информации, первый запоминающий блок операндов и результатов вместе с идентифицирующим символом, второй запоминающий блок хранения кода операции, по крайней мере, одного символа для идентификации операнда, хранящегося в первом запоминающем блоке, и одного символа для идентификации результата, также хранимого в первом запоминающем блоке, первые логические схемы передачи кода операции из второго запоминающего блока в один из блоков обработки информации, вторые логические схемы для передачи операнда или результата, считанных из первого запоминающего блока, в один из блоков обработки информации, третьи логические схемы для подачи результатов из блоков обработки информации в первый запоминающий блок в соответствии с идентифицирующим результат символом адресной части слова, переданный в данный блок обработки информации, с хранением результата в первом блоке в соответствии с символом.

граммном режиме, а также сложность структуры устройств управления.

Предлагаемая система отличается тем, что она содержит буферное запоминающее устройство, блок сравнения, подключенный к выходам буферного запоминающего устройства и выходам готовности блоков обработки, схемы передачи, включенные между выходом второго запоминающего устройства над входом первого ЗУ, схемы передачи идентифицирующих результат си.мволов на опрос второго блока, связанные с выходами блоков обработки и схемами опроса второго запоминающего устройства, схемы передачи адресов, подключенные к выходу второго запоминающего устройства и входу буферного запоминающего устройства; первая память содержит запоминающий регистр, связанный со вторыми логическими схемами, а источник данных и символов связан через логические схемы со схемами запроса второго запоминающего блока.

Это позволяет увеличить эффективность работы системы в мультипрограммном режиме и упросгить структуру устройств управления.

Другими отличия.ми является то, что второе запоминающее устройство выполнено ассоциативным, а буферное запоминающее устройство - в виде стэка.

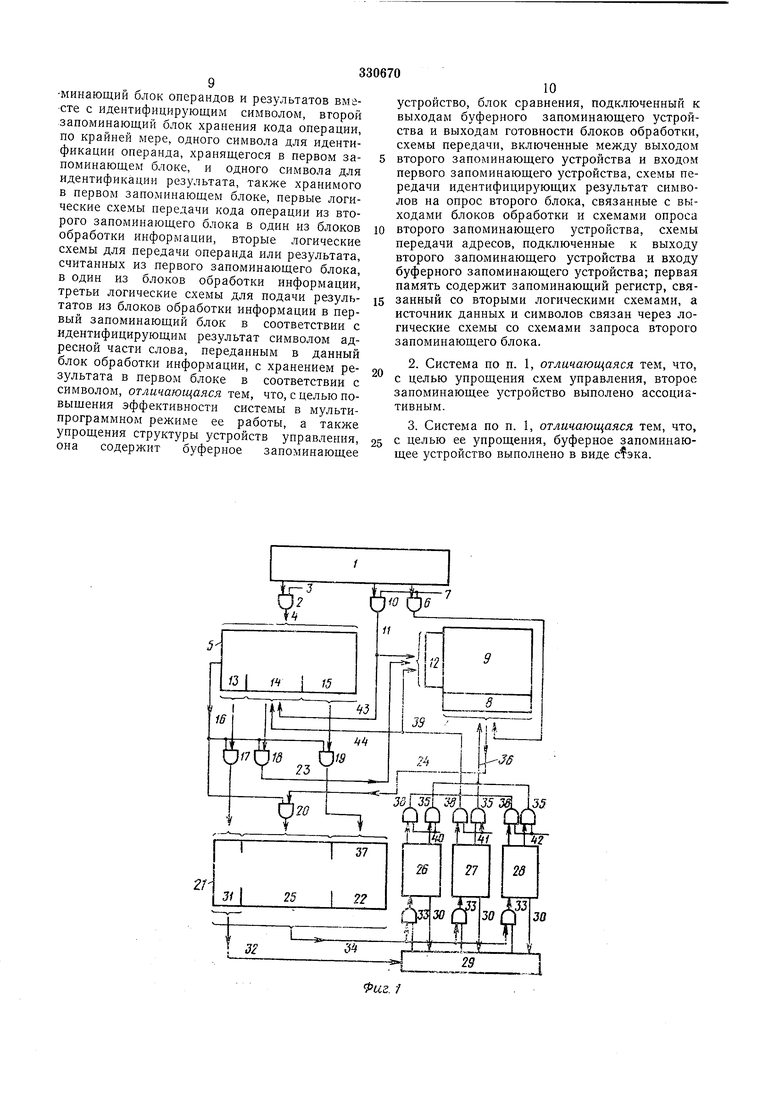

фиг. 2 - модификация системы, изображенной на фи1. 1 для случая, когда команды включают адреса двух операндов.

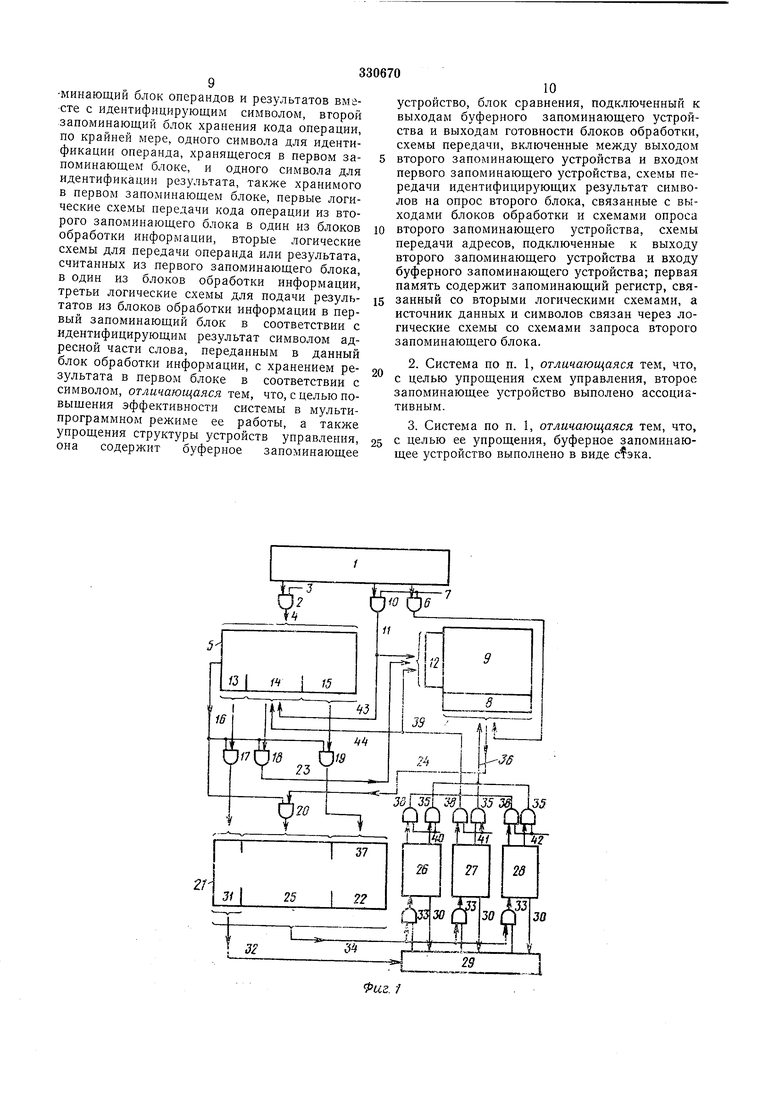

Система содержит источник I команд и данных, нанример блок с магнитной лентой, ценгральный блок вычислительного устройства для обработки информации или основное заноминающее устройство. Команды нодаются из источника 1 через схему 2 совпадения нри нодаче синхронизирующего имнульса по шине 3 ко входу 4 ассоциативной памяти 5 команд. Данные подаются из источника / через схему 6 совпадения нри подаче синхронизирующего импульса по шине 7 к регистру 8 хранения данных памяти 9 операндов. В то же время в течение импульса по щине 7 адрес памяти подается из источника / через схему 10 совпадения но шине П в регистр 12 для хранения адресов памяти. Схемы совпадения и шины представляют собой обычные многоразрядные блокн схем совпадения и проводника, способные передавать параллельно несколько или много информационных двоичных разрядов команды, операнда или адреса. Память 9 является обычной памятью с произвольной выборкой, в которой операнды хранятся в ячейках памяти, определяемых при помощи адреcoBj подающихся в регистр 12 для хранения адресов памяти.

Ассоциативная память 5 команд может быть Bbirfetfi-HSHa как любая обычная ассоциативная память.

Могут быть использованы и другие запоминающие устройства с адресной выборкой. Ассоциативная па.мять 5 команд используется для хранения командных слов, каждое из которых включает область 13, содержащую код операции, адрес операнда или символьную область 14, а также область 15, содержащую адрес результата. Каждая команда мож.ет также включать различные дополнительные обласги или двоичные разряды для констанг переадресации, адресов, индикаторов и т. д.

Ассоциативная память 5 сконструирована таким образом, что ее часть 14, в которой заключается область адреса операнда, может .быть опрошена с целью выяснения, существует ли одно или больше командных слов (в памяти, содержащей область адреса операнда), соответствующее опрашиваемому сигналу. Если такое соответствие обнаружено, то искомое командное слово считывается из памяги по сигналу обычных схем управления. Считанный сигнал по шине 16 подается на схемы совпадения 17-20.

Когда командное слово считано из ассоциативной памяти 5 команд, область 13 кода операции командного слова направляется через схему 17 совпадения к области кода операции в оперативно-операндный куб 21 буферного запоминающего устройства. В то же время область 15 адреса резульгата командного слова считывается из ассоциативной памяти 5 и проходит через схему совпадения 19 к части 22 адреса результата оперативно-операндного

куба 21 запоминающего устройства. Направление выбирается при помощи области 14 адреса операнда из считанной команды. Область 14 адреса операнда из считанной команды проходит через схему 18 совпадения и по линии 23 попадает в регистр 12 для хранения адресов операндной памяти 9. Когда адрес операнда попадает в регистр 12 для хранения адресов, то адресованный операнд считывается

из операндной памяти 9, проходит по линии 24 через схему 20 совпадения к онерандной части 25 куба 21 онеративного запоминающего устройсгва для операндов. Суммируя вышеизложенное, можно заметить, что код операции

в обласги 13 и адрес результата в области 15 командного слова в ассоциативной командной памяти 5 передаются непосредственно в куб 21. Однако адрес операнда командного слова в области 14 используется для выборки самого

операнда и нередачи операнда в куб 21.

Куб 21 может быть обычным устройством для временного хранения информации или буферным запоминающим устройством, способным онеративно хранить множество операндов.

Оперативно-операндный куб запоминающего устройства желательно выполнить в виде стэка с рециркуляцией, который мог бы воспринимать слова в своей верхней части, передавать слова вниз, располагая их в донной части,

и затем осуществлять рециркуляцию слов из донной части или выходной в верхнюю часть, если эти слова не передаются немедленно к другим блокам. Куб 21 запоминающего устройства здесь подробно описываться не

будет, поскольку он может быть сконструирован любым из хорошо известных способов для выполнения буферных функций.

Каждый из множества блоков 26, 27 и 28

вычислительных устройств для обработки информации может выполнять различные функции, такие как сложение, вычитание, умножение, сдвиг и т. д. С другой стороны, два или более вычислительных блока могут выполнять

одну и ту же функцию, например, сложение. Возможен также случай, когда вычислительные устройства для обработки информации одинаковы и могут выполнять все виды арифметических операций. В любом случае множество блоков вычислительных устройств для обработки информации сконструировано таким образом, что они могут работать одновременно, причем каждый выполняет операцию, соответствующую оперативно-операндному слову, которое подается в блок из оперативно-операндного куба 21 запоминающего устройства.

Передача оперативно-операндных слов из куба 21 запоминающего устройства контролируется при помощи блока 29 сравнения. Каждый блок вычислительного устройства для обработки информации после заверщения своей рабогы выдает сигнал готовности, который по соответствующим линиям 30 подается в блок 29 сравнения. Часть 31 кода операции

ба 21 запоминающего устройства по линии 32 подается в блок 29 сравнения.

Таким образом, код операции, подаваемый в блок сравнения, может указывать, что команда па выходе куба 21 запоминающего устройства требует для своего выполнепия наличия, например, сумматора или множительного устройства. Блок 29 сравнения сравнивает код операции с сигналом готовности из вычислительных устройств для обработки информации в целях определения, готов ли соответствующий блок вычислительного устройства для обработки информации к выполнению оперативно-операндного слова. Если блок вычислительного устройства для обработки информации находится в состоянии готовности, то блок сравнения отпирает соответственно одну из схем 33 совпадения (передачи), так что полное оперативно-операндное слово передается из куба 21 запоминающего устройства по линии 54 к соответственно одному из блоков 26-28 вычислительных устройств для обработки информации.

В блок вычислительного устройства для обработки информации подается таким образом оперативно-операндное слово, включающее код операции, операнд и адрес результата, что дает возможность автономно продолжать выполнение оперативно-операндного слова. Когда блок вычислительного устройства для обработки информации заканчивает выполнение операции и содержит готовый результат, этот результат передается через схему 35 совпадения и по линии 36 в регистр 8 памяти для данных операндной памяти 9. В то же самое время часть 37 адреса результата операнда, полученная при помощи блока вычислительного устройства для обработки информации из куба 21 оперативного запоминающего устройства, проходит через схему 38 совпадения и по линии 39 попадает в адресный регистр 12, операндной памяти 9. Пары схем совпадения 35 и 38 отпираются, каждая соответствующим синхронизирующим сигналом по щинам 40-42, синхронизирующие сигналы приходят последовательно для того, чтобы избежать наложений, если результаты двух или более блоков вычислительных устройств для обработки информации будут готовы в одно и то же время. В другом варианте вместо использования синхронизирующей последовательности импульсов по шинам 40-42 операция контроля может быть выполнена при помощи любой хорощо известной селекции и блокирующего устройства.

При помощи обзора операнд, требуемый для выполнения команды, идентифицируется в команде при помощи адреса операнда в операндной памяти 9. Подобным же образом вычисленный результат, который должен быть получен при выполнении команды, идентифицируется в команде при помощи адреса, под которым этот результат хранится в операндной памяти 9. Адреса операндов и вычисленных результатов являются идентифицирующими операнд и результат символами соответственно. Идентифицирующие операнд и результат символы необходимы для адресования памяти, но они удобны в обычно применяемых адресах памяти для дополнительной цели идентификации и сравнения готовых операндов с требуемыми.

Ниже будет описана последовательность, в которой командные слова считываются из ассоциативной командной памяти 5 п приводятся в готовность для использования в блоках вычислительных устройств для обработки информации. Время, при котором командное слово считывается из ассоциативной командной 5 определяется не столько позицией команды в последовательности команд, сколько готовностью операнда, нужного для выполнения команды. Операнд готов, если он хранится в операндной памяти 9. О готовности операнда сигнализируется, когда он сначала передается в операндную память 9 для хранения.

Операнд может быть передан в операндную память 9, как н данные из источника / команд и данных. Когда данные передаются в операндную память 9, адрес данных подается по линий 11 к адресному регистру 12, в то же вре.мя по 43 подается в качестве опрашивающего сигнала в область 14 адресов операндов ассоциативной командной памяти 5. Если адрес данных пли операнда, находящегося в операндной памяти 9, тот же самый, что п адрес операнда командного слова в ассоциативной командной памяти 5, то команда может быть выполнена. Следовательно, командное слово считывается из ассоциативной командной памят 5 в оперативно-операндный куб 21 запоминающего устройства.

Результат вычислений устройством для обработки информации при выполнении команды может быть операндом, требующимся для другой команды в ассоциативной командной памяти 5. Когда результат передается по линии 39 в операндную память 9. то, кроме того, он подается по линии 44 в качестве опрашивающего сигнала в области 14 адресов операндов ассоциативной командной памяти 5. Если адрес, по которому результат из вычислительного устройства для обработки информации подается в операндную память Я тот же самый, что и адрес операнда команды в ассоциативной командной памяти 5, то команда может быть выполнена. Следовательно, команда передается в оперативно-операндный куб 21 запоминающего устройства.

Порядок, в котором выполняется команда программы, определяется не столько ее местом в написанной последовательности команд в программе, сколько готовностью необходимого операнда и готовностью вычислительного устройства для обработки информации к выполнению команды. Действительная последовательность, в которой выполняются команды, может быть и не предписанной и изменяться в зависимости от готовности операндов и вычислительных устройств для обработки информации в те моменты, когда тесты на готовность уже проведены. Однако команды исполняются в последовательности, которая максимизирует использование нескольких вычислительных устройств для обработки информации.

В системе автоматически контролируется последовательность, в которой выполняются команды, способом, обеспечивающим сравнительно быстрое завершение программы или программ, подлежащих выполнению. Когда ассоциативная командная память 5 содержит части ряда различных программ, вычислительные устройства для обработки информации продолжают выполнять команды, которые могут быть вынолнены во всех программах, ие будучи ограничены выполнением команд одной программы. Одновременное выполнение команд различных программ осуществляется при помощи аппаратуры, без потерь , существующих при использовании системы управления для средств программирования.

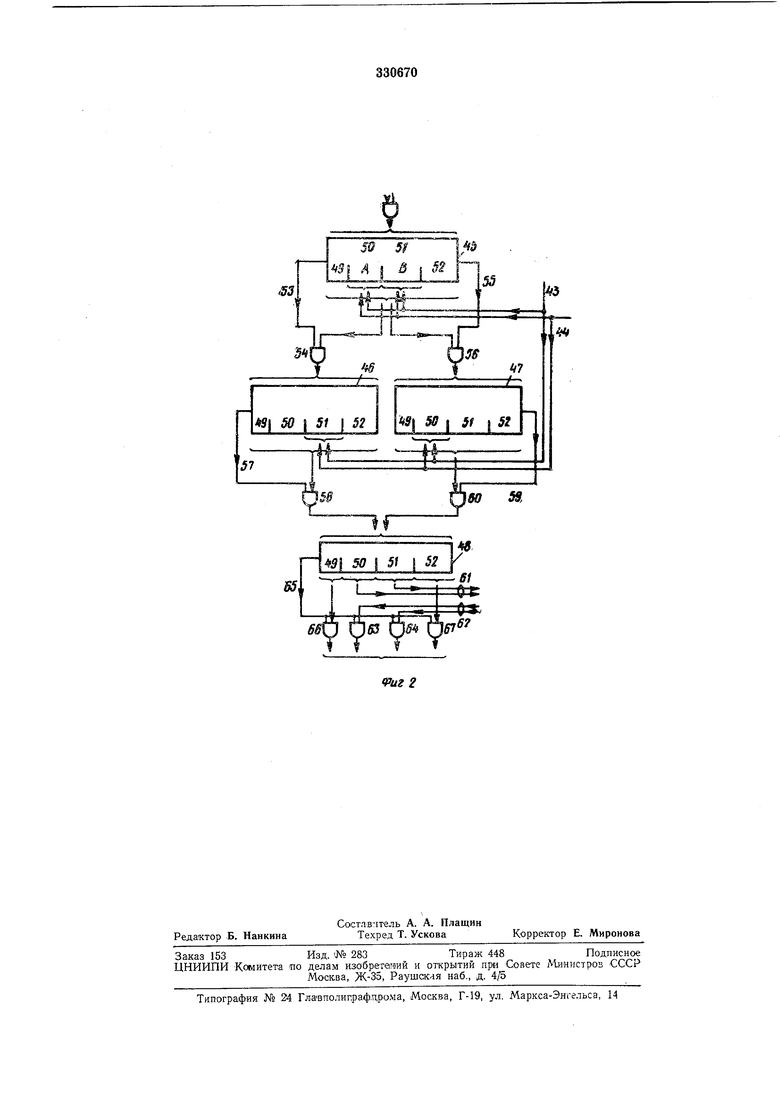

Предлагаемое изобретение, как уже было описано, применяется в такой системе, где каждая команда включает два адреса: адрес операнда и адрес результата. Некоторые вычислительные машины работают с использованием трехадресных команд, причем каждая команда включает: а) адрес операнда и в) адрес операнда и адрес результата. Сист.ма, изображенная па фиг. 2, является модификацией системы, изобрал енной на фиг. , причем в этой модификации используются трехадресные команды, включающие два адреса операнда.

На фиг. 2 показаны три блока 45, 46 и 47 ассоциативный командной памяти, а также сборка 48, которая может быть подставлена вместо ассоциативной командной памяти 5 системы, пзображенной на фиг 1. Блок 45 предназначен для хранения команд, из которых каждая включает часть 49 с кодом операции, часть 50 с адресом первого операнда А, часть 51 с адресом второго операнда В и часть 52 с адресом результата. Дополнительные блоки 46 и 47 ассоциативной командной памяти одинаковы по констр,укции и предназначены для хранения команд, из которых каждая включает перечисленные частн. Операндные адреса, поданные по линиям 43 и 44, приложены в качестве опращивающих сигналов, как в адресной части 50, так и к адресной части 51 блока 45 ассоциативно командной памяти (фиг. 2). Таким образом,, адрес, появляющийся на линии 43, подается одновременно к частям 50 и 51 блока 45, а адрес, появившийся в другое время на линии 44, также подается одновременно к частям 50 и 51 блока 45.

который разрещает считывание из блока 45 памяти полного командного слова и передачу командного слова в блок 46 ассоциативной командной памяти. Аналогично, если опрошепный адрес передан в адресную часть .5/ блока 45 и согласуется с соответствующей частью команды, хранящейся в памяти, то память управляется сигналом на линии 55 и схемы совпадения 56, что вызывает передачу

согласованной команды в блок 47 ассоциативной командной намяти. В результате оказывается, что команды, оставшиеся в блоке 45, являются командами, для которых нет операндов А и В в операндной памяти 9. Для

команды в блоке 46 ассоциативной командной памяти готов только онеранд А, а для команд, содержащихся в блоке 47, готов только операнд В.

В то же время эти опрощенные адреса подаются в адресные части А и В блока 45, одновременно они подаются в качестве опращивающих сигналов в адресную часть 5/ блока и в адресную часть 50 б.юка 47 памяти. Если опращиваемые адреса поданы в В адреспую часть 51 блока 46 и согласуются с соответствующей частью команды в памяти, тогда блок 46 памяти выдает контрольный сигнал на линию 57 и схему 58 совпадения, что вызывает передачу соответствующей

команды в сборку 48. Аналогично, когда опращиваемые адреса поданы в А адресную часть 50 блока 47 и согласуются с соответствующей адресной частью команды в памяти, тогда память выдает сигнал на линию 55 и

схему совпадения 60, что вызывает передачу соответствующей команды в сборку 48. Команда, поданная из блока 46 памяти или из блока 47 памяти в сборку 48, представляет собой команду, которая была определена при

помощи опроса, причем оба из двух требуемых операндов были в состоянии готовности в операндной памяти 9, в системе, показанной на фиг. 1.

Когда команды переданы в сборку 48, она

направляет адресную часть 49 и адресную часть 50 команды по линиям 61 в адресный регистр 12 операндной памяти 9. Это способствует успещному поиску операндов, хранящихся в операндной памяти. Полученные

операнды передаются из регистра 12 для хранения данных операндной памяти по линиям 62 к схемам совпадения 63 и 64. В то же время сборка формирует контрольный сигнал на линии 65, отпирающий схемы совпадения 63,

64 и 66, 67 для передачи результирующего полного оперативно-операндного слова к оперативно-операндному кубу 21 запоминающего устройства. Следовательно, трехадресная система работает так же, как и двухадресная,

показанная на фиг. 1.

-минающий блок операндов и результатов вмасте с идентифицирующим символом, агорой запоминающий блок хранения кода операции, по крайней мере, одного символа для идентификации операнда, хранящегося в первом запоминающем блоке, и одного символа для идентификации результата, также хранимого в первом запоминающем блоке, первые логические схемы передачи кода операции из второго запоминающего блока в один из блоков обработки информации, вторые логические схемы для передачи операнда или результата, считанных из первого запоминающего блока, в один из блоков обработки информации, третьи логические схемы для подачи результатов из блоков обработки информации в первый запоминающий блок в соответствии с идентифицирующим результат символом адресной части слова, переданным в данный блок обработки информации, с хранением результата в первом блоке в соответствии с символом, отличающаяся тем, что, с целью повыщения эффективности системы в мультипрограммном режиме ее работы, а также упрощения структуры устройств управления, она содержит буферное запоминающее

10

устройство, блок сравнения, подключенный к выходам буферного запоминающего устройства и выходам готовности блоков обработки, схемы передачи, включенные между выходом второго запоминающего устройства и входом первого запоминающего устройства, схемы передачи идентифицирующих результат символов на опрос второго блока, связанные с выходами блоков обработки и схемами опроса второго запоминающего устройства, схемы передачи адресов, подключенные к выходу второго запоминающего устройства и входу буферного запоминающего устройства; первая память содержит запоминающий регистр, связанный со вторыми логическими схемами, а источник данных и символов связан через логические схемы со схемами запроса второго запоминающего блока.

2.Система по п. 1, отличающаяся тем, что, с целью упрощения схем управления, второе запоминающее устройство выполено ассоциативным.

3.Система по п. 1, отличающаяся тем, что, с целью ее упрощения, буферное запоминающее устройство выполнено в виде .

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| СИСТЕМА СВЯЗИ С ИСПОЛЬЗОВАНИЕМ СПЕКТРА НА СФЕРИЧЕСКУЮ ПОВЕРХНОСТЬ | 1993 |

|

RU2108672C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1998 |

|

RU2148857C1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

Авторы

Даты

1972-01-01—Публикация