Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки информации.

Известно однокристальное устройство для обработки информации, содержащее взаимосвязанные параллельной шиной операционный блок и блок памяти, а также блоки ввода и вывода информации, ориентированное на организацию обработки двоичных кодов по месту хранения данных [1].

В качестве недостатков устройства можно назвать ограниченные функциональные возможности устройства и невысокое быстродействие вследствие последовательного характера работы устройства.

Известно также устройство для параллельной обработки числовой информации, содержащее память командных ячеек для реализации управления потоками данных, матрицу ожидания готовых командных ячеек с командными ключами, скалярные процессоры, процессор памяти для управления обменом данными между основной памятью и памятью командных ячеек, векторный процессор для обработки векторных команд, блочный процессор для управления загрузкой команд из основной памяти в память командных ячеек, а также блоки ввода и вывода данных [2].

Недостатком устройства является сохранение архитектурной ориентации на традиционное представление команд, свойственное машинам фон Неймана: коды исходных операндов и результатов вычисления хранятся в памяти данных (остается возможность несанкционированного доступа), поле операндов в формате командной ячейки содержит коды указателей на командные ячейки - источники входных данных, а поле данных командной ячейки - код результата выполнения операции и флаг готовности результата, что усложняет процедуру определения готовности командной ячейки к обработке и, как следствие, увеличивает время решения задачи.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для обработки информации, содержащее координатный коммутатор, взаимосвязанный посредством блока буферной памяти скалярных команд и блока буферной памяти данных со скалярными операционными блоками, посредством векторных регистров и блока буферной памяти векторных команд - с векторным операционным блоком, посредством параллельных шин памяти - с блоками оперативной памяти, а посредством шин ввода/вывода - с блоками ввода/вывода данных [3].

В качестве недостатка последнего решения следует отметить последовательный характер программного управления вычислениями: хотя распределение нагрузки между операционными блоками осуществляется в ходе выполнения программы, однако число операционных блоков ограничено, что не позволяет в полной мере реализовать потенциальные возможности распараллеливания процесса решения задачи и, следовательно, уменьшить время решения задачи. Кроме того, в архитектуре последнего устройства для обработки информации отсутствуют аппаратные средства, необходимые для решения задач, свойственных нейросетевому логическому базису, и для автоматического распараллеливания вычислительного процесса.

Задача настоящего изобретения - расширение функциональных возможностей устройства для обработки информации за счет реализации нейросетевых задач, а также ускорение вычислительного процесса за счет архитектурного осуществления параллелизма решаемой задачи.

Поставленная задача достигается тем, что устройство для обработки информации содержит блоки памяти готовности данных с логическими схемами готовности данных, взаимосвязанные с соответствующими параллельными шинами памяти, регистр занятости, соединенный со скалярными операционными блоками и входами логической схемы занятости, информационную шину, которая совместно с регистром занятости образует цепочный интерфейс, а также блок буферной памяти функциональных параметров, который совместно с блоком буферной памяти скалярных команд и блоком буферной памяти данных образуют магазинную память, взаимосвязанную по входам с координатным коммутатором, а по выходам - с информационной шиной, которая соединена со входами скалярных операционных блоков, выходы которых, в свою очередь, взаимосвязаны с координатным коммутатором, а выход логической схемы занятости соединен с магазинной памятью.

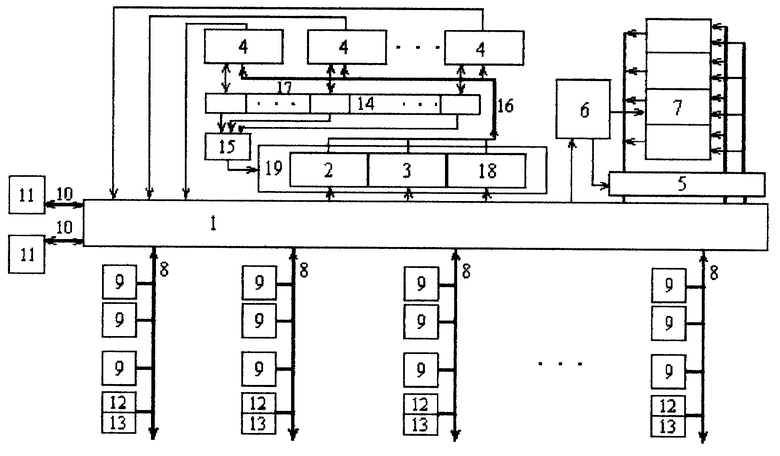

На чертеже представлена структурная схема предлагаемого устройства для обработки дискретной информации.

Устройство для обработки дискретной информации содержит координатный коммутатор 1, соединенный посредством блока буферной памяти команд 2 и блока буферной памяти данных 3 со скалярными операционными блоками 4, посредством векторных регистров 5 и блока буферной памяти векторных команд 6 - с векторным операционным блоком 7, посредством параллельных шин памяти 8 - с блоками оперативной памяти 9, а посредством шин ввода/вывода 10 - с блоками ввода/вывода данных 11, блоки памяти готовности данных 12 с логическими схемами готовности данных 13, регистр занятости 14, выходы которого соединены со входами логической схемы занятости 15, информационную шину 16, которая совместно с регистром занятости образует цепочный интерфейс 17, а также блок памяти функциональных параметров 18, который совместно с блоком буферной памяти команд и блоком буферной памяти данных образуют магазинную память 19.

Предлагаемое устройство для обработки дискретной информации функционирует следующим образом.

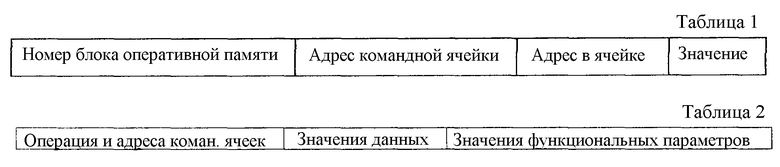

В режиме ввода данных блоки ввода/вывода 11 формируют пакеты данных в формате (см табл. 1).

Пакеты данных через шины ввода/вывода 10 поступают в координатный коммутатор 1, управляемый полем "Номер блока оперативной памяти" пакета. Поле "Значение" данных заносится в ячейку блока оперативной памяти данных 9, адресуемую полями "Адрес командной ячейки" и "Адрес в ячейке". В том же адресном сечении блока памяти готовности данных 12 устанавливается бит готовности. Установка всех битов готовности в некотором адресном сечении блока локальной памяти готовности данных контролируется схемой готовности данных 13, которая в этом случае инициирует обнуление названного адресного сечения блока памяти готовности данных 12, формирование и выборку командного пакета из данного адресного сечения блоков оперативной памяти 9 на соответствующую параллельную шину памяти 8 устройства в следующем форматере (см. табл. 2).

Процесс обработки начинается с момента передачи скалярного командного пакета с параллельной шины памяти 8 через координатный коммутатор 1 в магазинную память 19. Причем значения кодов полей "Операция и адреса командных ячеек", "Значения данных" и "Значения функциональных параметров" скалярного командного пакета заносятся соответственно в блок буферной памяти скалярных команд 2, блок буферной памяти данных 3 и блок буферной памяти функциональных параметров 18. Если хотя бы один из скалярных операционных блоков 4 свободен (хотя бы в одном разряде регистра занятости 14 записан логический ноль), то логическая схема занятости 15 сформирует сигнал разрешения выдачи скалярного командного пакета из магазинной памяти 19 на информационную шину 16. В соответствии с логикой работы цепочного интерфейса 17 скалярный командный пакет будет транслироваться по информационной шине 16 до первого свободного скалярного операционного блока 4. Фиксация скалярного командного пакета во входных цепях скалярного операционного блока удаляет его с информационной шины и устанавливает соответствующий разряд в регистре занятости 14. В случае занятости всех скалярных операционных блоков логическая схема занятости 15 сформирует сигнал запрещения выдачи скалярных командных пакетов из магазинной памяти 19. Вновь поступающие из координатного коммутатора 1 скалярные командные пакеты будут накапливаться в магазинной памяти 19 до момента освобождения одного из скалярных операционных блоков 4 и сброса соответствующего разряда регистра занятости 14. Зафиксированный во входных цепях скалярного операционного блока склярный командный пакет содержит полный набор функциональных параметров и значений данных, подлежащих обработке, реализуемую функцию и коды адресов командных ячеек - приемников результата (источников операндов). Скалярный операционный блок 4 после завершения обработки формирует столько пакетов данных, сколько адресов командных ячеек - приемников результата он содержит и сбрасывает соответствующий разряд регистра занятости 14. Сформированные пакеты данных поступают через координатный коммутатор 1 на параллельные шины памяти 8 и заносятся в соответствующие адресам блоки оперативной памяти 9 аналогично процессу ввода исходных данных.

Процесс обработки векторного командного пакета начинается с момента его передачи с соответствующей параллельной шины памяти 8 через координатный коммутатор 1 в блок буферной памяти векторных команд 6. Причем в полях "Значения данных" и "Значения функциональных параметров" векторного командного пакета содержатся не значения скалярных данных, а начальные адреса и размерность обрабатываемых векторных данных. В процессе обработки через параллельные шины памяти 8 координатный коммутатор 1 и векторные регистры 5 организуются конвейеры для передачи исходных векторных данных в векторные операционные блоки 7 и приема векторов результатов в блоки оперативной памяти 9. В случае упреждающей выборки происходит накопление необработанных векторных командных пакетов в блоке буферной памяти векторных команд 6.

В режиме вывода результаты вычислений оформляются в виде пакетов данных, адресное поле каждого из которых соответствует одному из адресов блоков ввода/вывода данных 10. Пакеты данных поступают с выходов скалярных операционных блоков 4 или параллельных шин памяти 8 через координатный коммутатор 1 на соответствующую шину ввода/вывода 10 и фиксируются во входных цепях блоков ввода/вывода данных 11.

В режиме программирования устройства для обработки дискретной информации необходимо в каждую командную ячейку в соответствующее адресное сечение блока оперативной памяти 9 ввести коды адресов командных ячеек - приемников результата. В этом случае значение адреса командной ячейки - приемника результата (поле "Значение") пакета данных, формируемого в блоке ввода/вывода 11, через соответствующую шину ввода/вывода 10 и координатный коммутатор 1 заносится в адресное сечение (поле "Адрес командной ячейки" и поле "Адрес в ячейке") заданного блока оперативной памяти 9 (поле "Номер блока оперативной памяти"). Программирование устройства осуществляется перед его использованием в вышеперечисленных режимах функционирования.

Режим настройки функциональных параметров устройства для обработки дискретной информации аналогичен рассмотренной последовательности программирования с той лишь разницей, что поле "Значение" пакета данных помещается в адресное сечение блока оперативной памяти 9, соответствующего месту хранения функциональных параметров в названном адресном сечении. Настройка функциональных параметров производится после осуществления программирования заявляемого устройства, но перед его работой в режимах ввода данных, обработки и вывода результатов. Выполнение процедуры настройки после осуществления программирования устройства существенно при решении задач в нейросетевом логическом базисе, т.к. процесс программирования задает связи между элементами нейронной сети, а функциональные параметры подбираются в процессе "обучения" уже сформированной сети. Если же функциональные параметры заранее известны (сеть "обучена"), то порядок программирования и настройки устройства для обработки информации может быть произвольным.

Введение в структуру устройства блока буферной памяти функциональных параметров, который совместно с блоком буферной памяти команд и блоком буферной памяти данных образуют магазинную память, блоков памяти готовности данных с логическими схемами готовности данных, информационной шины, которая совместно с регистром занятости образует цепочный интерфейс, позволяет ускорить процесс распараллеливания вычислений за счет архитектурной самореализации параллелизма решаемой задачи и оперативной передачи готовых к обработке скалярных командных пакетов из магазинной памяти к скалярным операционным блокам. Помещение скалярных командных пакетов в магазинную память и наличие цепочного интерфейса с регистром занятости дает возможность автоматически и с минимальными затратами времени распределять скалярных командные пакеты по свободным скалярным операционным блокам без явного указания операционного блока - получателя пакета. С другой стороны, наличие координатного коммутатора и параллельных шин памяти позволяет осуществлять одновременную передачу значительного количества пакетов данных по высокоскоростным каналам при адресной рассылке результатов обработки в конкретные блоки оперативной памяти 8, что дополнительно повышает производительность устройства. Наличие блоков памяти готовности данных дает возможность использовать механизм самоуправления вычислениями и, следовательно, реализовать в максимальной степени параллелизм, свойственный данной задаче. Блок буферной памяти функциональных параметров существенно расширяет функциональные возможности заявляемого устройства путем обеспечения реализации функции настройки ("обучения") вычислительной сети, что позволяет решать специфические задачи, свойственные нейросетевому логическому базису: классификации образов, аппроксимации, предсказания, оптимизации, организации ассоциативной памяти, управления динамическими системами.

Процесс работы и обучения нейронной сети, реализованной в заявляемом устройстве, может быть существенно ускорен за счет использования векторного операционного блока при проведении значительного числа однотипных расчетов, например, связанных с подстройкой весовых коэффициентов слоев формальных нейронов. Расчеты значений функциональных параметров и выходов нейронной сети хорошо согласуются с концепцией конвейеризации и сцепления конвейеров, т.к. вектор результатов некоторого слоя формальных нейронов сети, получаемый за счет умножения входного вектора на матрицу весовых коэффициентов, в свою очередь является входным вектором для следующего слоя и т.д.

Таким образом, наличие векторного операционного блока позволяет существенно ускорить обработку данных при выполнении фрагментов программ, поддающихся векторизации, а наличие взаимосвязанных вышеописанным образом скалярных операционных блоков дает возможность в максимальной степени распараллелить обработку оставшихся программных фрагментов.

Источники информации

1. Авторское свидетельство СССР N 809190.

2. Компьютеры на СБИС: В 2-х кн. Кн.2: Пер. с япон. /Мотоока Т., Хорикоси X., Сакаути М. и др. - М.: Мир, 1988, - 336 с., сс.78-81.

3. D. Patterson, Т. Anderson, N. Cardwell, et al. Intelligent RAM (IRAM): Chips that remember and compute. Digest of Technical Papers, 1997 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, Feb., 1997.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОСЕТЕВОЕ ДИСКРЕТНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2003 |

|

RU2250501C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| НЕЙРОСЕТЕВОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2008 |

|

RU2394274C2 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2373568C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2331923C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки информации. Технический результат заключается в расширении функциональных возможностей устройства для обработки информации за счет реализации нейросетевых задач, а также ускорения вычислительного процесса за счет архитектурного осуществления параллелизма решаемой задачи. Устройство содержит координатный коммутатор, блок буферной памяти скалярных команд, блок буферной памяти данных, скалярные операционные блоки, векторные регистры, блок буферной памяти векторных команд, векторные операционные блоки, параллельные шины памяти, блоки оперативной памяти, шины ввода/вывода, блоки ввода/вывода данных, блоки памяти готовности данных, логические схемы готовности данных, регистр занятости, логическую схему занятости, информационную шину, цепочный интерфейс, блок буферной памяти функциональных параметров, магазинную память. 1 ил., 2 табл.

Устройство для обработки дискретной информации, содержащее координатный коммутатор, соединенный непосредственно с блоком буферной памяти скалярных команд и с блоком буферной памяти данных, а далее через данные блоки со скалярными операционными блоками, посредством векторных регистров и блока буферной памяти векторных команд - с векторным операционным блоком, посредством параллельных шин памяти - с блоками оперативной памяти, а посредством шин ввода/вывода - с блоками ввода/вывода данных, отличающееся тем, что оно содержит блоки памяти готовности данных с логическими схемами готовности данных, взаимосвязанные с соответствующими параллельными шинами памяти, регистр занятости, соединенный со скалярными операционными блоками и входами логической схемы занятости, информационную шину, которая совместно с регистром занятости образует цепочный интерфейс, а также блок буферной памяти функциональных параметров, который совместно с блоком буферной памяти скалярных команд и блоком буферной памяти данных образуют магазинную память, взаимосвязанную по входам с координатным коммутатором, а по выходам - с информационной шиной, которая соединена со входами скалярных операционных блоков, выходы которых, в свою очередь, взаимосвязаны с координатным коммутатором, а выход логической схемы занятости соединен с магазинной памятью.

| ПАТТЕРСОН Д | |||

| и др | |||

| Доводы в пользу IRAM, журнал Компьютерра, #15, Издательский дом Компьютерра, 1998 | |||

| JP 08185381 А, 16.07.1996 | |||

| JP 63271569 A2, 09.11.1988 | |||

| JP 58149541 А, 05.09.1983. |

Авторы

Даты

2001-12-10—Публикация

2000-05-06—Подача