Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах, работающих в ненозиционных системах счисления, а именно в сумматорах по произвольному модулю для реализации вычитания по этому модулю.

Известно устройство для выполнения операции вычитания на сумматоре обратного кода с дополнительными связами, в котором вычитание заменяется сложением уменьшаемого с до1полнением вычитаемого до модуля сумматора.

Недостатком этого устройства является необходимость перевода вычитаемого в дополнение до модуля сумматора, что значительно увеличивает время выполнения операции вычитания по сравнению с временем выполнения сложения.

Цель изобретения - повысить скорость вычитания.

Указанная цель достигается благодаря тому, что сумматор дополнительно содержит вентили сложения-вычитания, две схемы совпадения, инвертор и схему «ИЛИ, входы вентилей сложения-вычитания соединены с входными шинами подачи первого операнда, а выходы-со входами позиционного сумматора, вторые входы которого соединены с входными шинами подачи второго операнда, выход переноса позиционного сумматора соединен с первым входом первой схемы совпадения и через инвертор с первым -входом второй схемы совпадения, второй вход первой схемы совпадения соединен с выходом инверсии суммы иепозпционного сумматора, второй вход второй схемы совпадения соединен с выходом инверсии суммы позиционного сумматора, выходы схем сов1падения соединены с соответствующими входами схемы «ИЛИ, выход которой соединен с выходной шиной устройства.

При вычитании числа В из числа А могут быть два случая:

А В и А В. Если А В, то результат

.В А + В A-f В.

вычитания равен: Акак Х -X, а Х Действительно, так --X-1,

В- (-А-1) -fB; то АА - В --J-А - 1) - В - 1,

т. е. А -В А+ В.

Например, нужно вычесть 3 из 9 по модулю 13, т. е. А :1001; В 0011 и , тогда:

А 0110

В 0011

Если А ; В, то результат вычитания будет отрицательным. Для того, чтобы сделать его положительным, к нему необходимо добавить значение модуля, т. е.

Sb4 А - В + Р - А + В + Р. Так как: х + у х + у

или: х+у х + у

то: А -В + Р А + В + Р. Например, А 0011; В 1001; Р

А 1100 + В 1001

Р 0011

А+В + Р 1000

А + В + Р 0111

Действительно, (3 - 9) is 7, т. е. 3 - 9 7 (мод 13).

Условие означает, что в позиционной части 1сумматора переноса из последнего т-го разряда нет. Действительно, представим входньге операнды А и В следующим образом:

А 2п-1а; Е , где а и h меньше единицы. Тогда: A 2m-i -2п1-1-а-1, и А +В 2П1-1 - 2Ш-1. а - 1 + 2°1-1-Ь, при этом условие отсутствия переноса из последнего разряда сумматора можно представить в виде:

А + В 2П1-1,

откуда: 2™-i - а - 1 +2«i-i b 2™-; или: 2m-i-b 2п1- -а+1, что полностью соответствует условию А В. Действительно, если А В, то

2m-i..a +, или же А В - 1, т. -е. А В, то: 2m-i.a +l i;2m-i.a + 1,

и т. д., т. е. ори условии А В в позиционной части сумматора будет перенос.

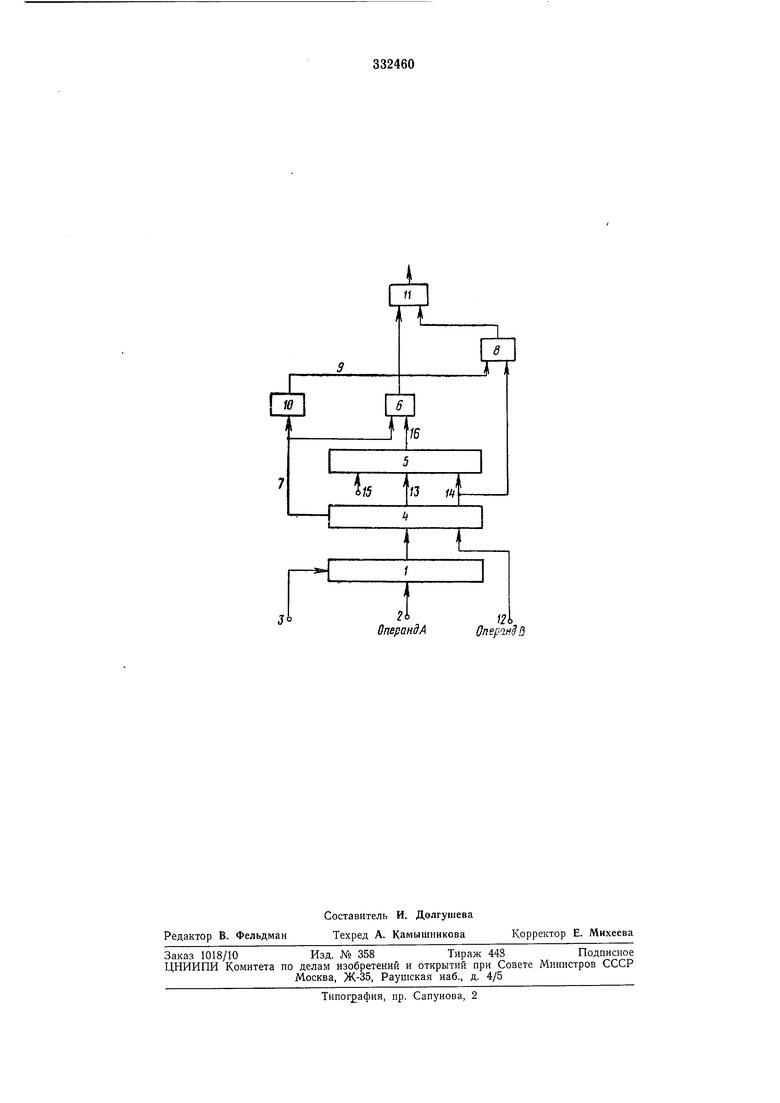

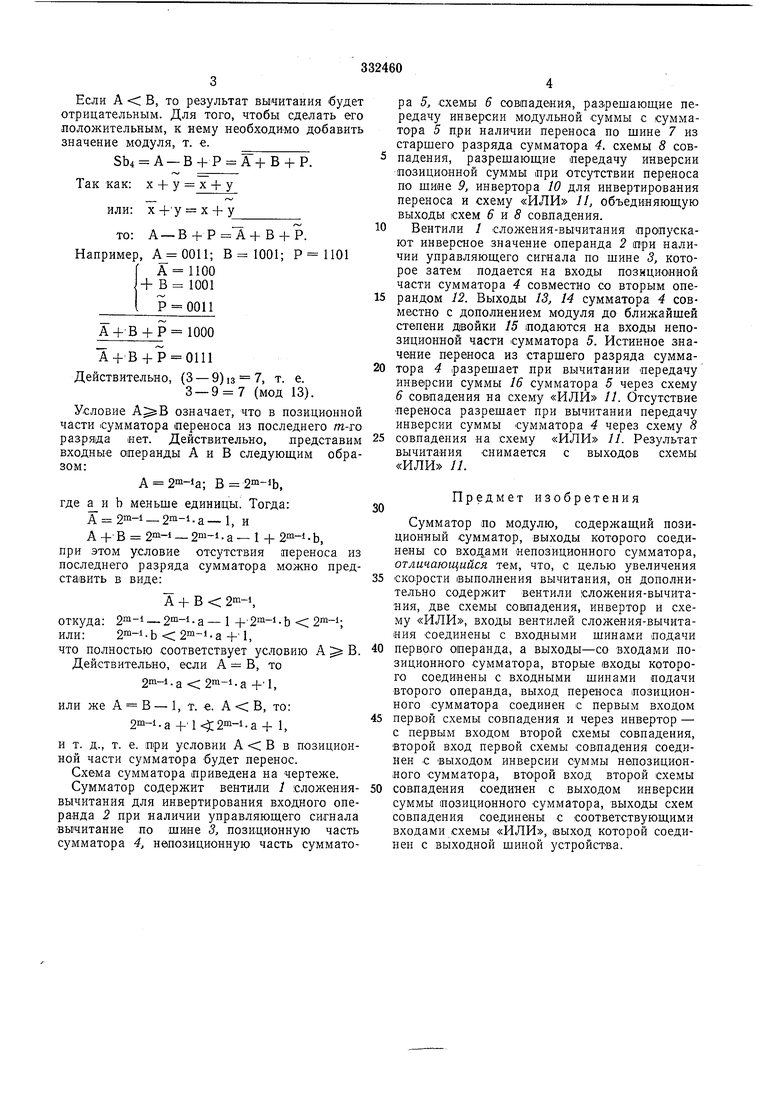

Схема сумматора приведена на чертеже.

Сумматор содержит вентили 1 сложениявычитания для инвертирования входного операнда 2 при наличии управляющего сигнала вычитание по шине 3, позн-ционную часть сумматора 4, нвпозиционную часть сумматора 5, схемы 6 совпадения, раЗ|решающие передачу инверсии модульной суммы с сумматора 5 при наличии переноса по шине 7 из старшего разряда сумматора 4. схемы 5 совпадения, разрешающие передачу инверсии позиционной суммы при отсутствии переноса по шине 9, инвертора 10 для инвертирования переноса и схему «ИЛИ //, объединяющую выходы схем 6 и 8 совладения.

Вентили 1 сложения-вычитания пропускают инверсное значение операнда 2 при наличии управляющего сигнала по шине 3, которое затем подается на входы позиционной части сумматора 4 совместно со вторым операндом 12. Выходы 13, 14 сумматора 4 совместно с дополнением модуля до ближайшей степени двойки 15 подаются на входы непозиционной части сумматора 5. Истинное значение переноса из старшего разряда сумматора 4 разрешает при вычитании передачу инверсии суммы 16 сумматора 5 через схему 6 совпадения на схему «ИЛИ 11. Отсутствие переноса разрешает при вычитании передачу инверсии суммы сумматора 4 через схему 8

совпадения на схему «ИЛИ 11. Результат вычитания снимается с выходов схемы

«ИЛИ /;.

Предмет изобретения

Сумматор по модулю, содержащий позиционный сумматор, выходы которого соединены со входами «епозиционного сумматора, отличающийся тем, что, с целью увеличения

скорости выполнения вычитания, он дополнительно содержит вентили сложения-вычитания, две схемы совпадения, инвертор и схему «ИЛИ, входы вентилей сложения-вычитания соединены с входными шинами подачи

первого операнда, а выходы-со входами позиционного сумматора, вторые входы которого соединены с входными шинами подачи второго операнда, выход переноса позиционного сумматора соединен с первым входом

первой схемы совпадения и через инвертор - с первым входом второй схемы совпадения, второй вход первой схемы совпадения соединен с ВЫХОДОМ инверсии суммы непозиционного сумматора, второй вход второй схемы

совпадения соединен с выходом инверсии суммы позиционного сумматора, выходы схем совпадения соединены с соответствующими входами схемы «ИЛИ, выход которой соединен с выходной шиной устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор-вычитатель по модулю | 1982 |

|

SU1075259A1 |

| Сумматор по модулю | 1982 |

|

SU1134939A1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1972 |

|

SU332459A1 |

| Устройство для сложения по модулю | 1982 |

|

SU1064278A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Сумматор по модулю | 1975 |

|

SU570052A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для сложения чисел в системе остаточных классов | 1980 |

|

SU930317A1 |

| Сумматор по модулю | 1979 |

|

SU855659A1 |

| ОДНОТАКТНЫЙ УМНОЖИТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ | 1988 |

|

RU2012039C1 |

Jb

/3 rV

2Ь

2Ь ОперанЗА

OnepiH B

Даты

1972-01-01—Публикация