(54) СУММАТОР ПО МОДУЛЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выравнивания порядков чисел,представленных в системе остаточных классов | 1973 |

|

SU781812A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Арифметическое устройство в системе остаточных классов | 1979 |

|

SU857992A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1405049A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах, работгиощих в непозиционных системах счисления, в системах контроля передачи дискретной инфор-мации и системах контроля работы вычислительных машин при построении сумматоров по произвольному модулю.

Известен сумматор в системе остаточных классов, в котором вычитание заменяется сложением уменьшаемого с дополнением вычитаемого по модулю, содержащий позиционный и непозиционный сумматоры, блок инвентирования кода, блок переполнения позиционного сумматора, группы элементов И и ИЛИ D-l.

Однако необходимость перевода вычитаемого в дополнение по модулю сумматора значительно увеличивает время вьшолнения операции вычитания по сравнен 1Ю с временем вы-, полнения сложения.

Наиболее близким к предлагаемому является сумматор в системе остаточных классов, содержащий два выходных регистра, операционный блок {матрицу), выполненный на ферритовых сердечниках,и элемент ИЛИ, причем

каждая выходная шина одного регистра через элемент ИЛИ и соответствующую обмотку ферритового сердечника операционной схемы соединена с каждой выходной шиной другого регистра 2,

Однако при представлении чисел в обобщенной искусственной форме знак скрыт в форме представления

10 чисел и нет возможности визуально определить является ли оно положительиьри или отрицательным. Для определения знака необходимо определить интервал, в котором находит15ся число. Но- определение знака значительно увеличивает время выполнения сложения и вычитания чисел.

Цель изобретения - повышение быстродействия сумматора.

20

Поставленная цель достигается тем, что сумматор содержит две группы элементов И, группу элементов ИЛИ, элемент И, четыре элемента ИЛИ, выходной регистр, причем информацион25ные выходы операционного блока соеди нены с первыми входами соответствующих элементов И первой группы, выходы каждых двух элементов И первой группы соединены со входами соответ30ствующего элемента ИЛИ группы, выходы элементов или группы соединены со входами выходного регистра, выходы которого являются информационными выходами устройства, знаковый выход операционного блока соединен с первыми входами четных элементов И второй группы, выход переполнения операционного блока соединен с первым входом элемента И, выход которого является выходом Переполнения устройства, первые входы первого и второго элементов И второй группы соединены между собой и с первым вх дом первого элемента ИЛИ и являются входом ОперандыЧ устройства, первые входы третьего и четвертого элемента И второй группы соединены между собой и со вторым входом первого элемента ИЛИ и являются входом Операнды -устроЕ ства, первые входы пятого и седьмого элементов И второй группы соединены между собой и с первым входом второго элемента ИЛИ и являются входом Л+В -устройства, первые входы шестого и восьмого элементов И второй группы соединены между собой и со вторым входом второго элемента ИЛИ и являются входом А-В +устройства, выходы первого и второго элементов ИЛИ соединены со вторыми входами соответственно четных и нечетных элементов И первой группы, выходы первого, второго, четвертого и восьмого элементов И второй группы соединены со входами третьего элемента ИЛИ, выход которого является выходом Результат -|-устройства, выходы третьего, четвертого, шестого и седьмого элементов И второй группы содинены со входами четвертого элемента ИЛИ, выход которого является выходом Результат -устройства.

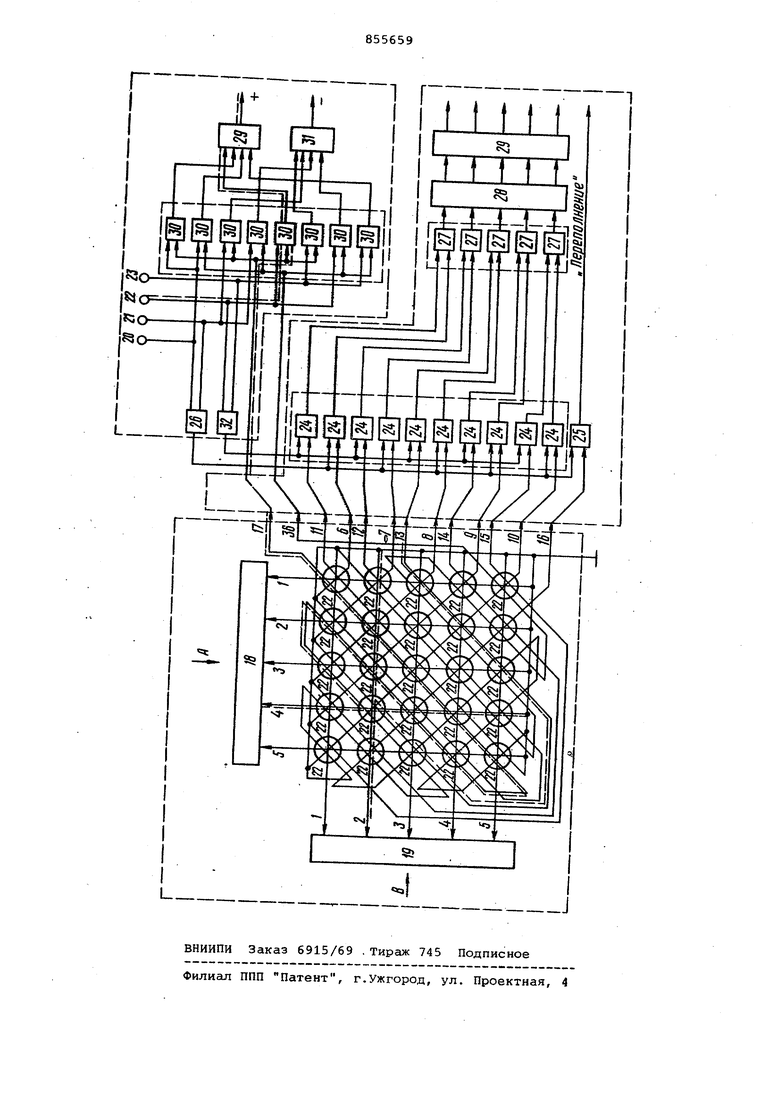

На чертеже представлена блок-схема устройства.

Устройство содержит входные обмотки 1-5 ферритовых сердечников, соответствующие остаткам чисел А и В по модулю пять; выходные обмотки 6-10 ферритовых сердечников результата суммы чисел при одинаковых знаках чисел А и В; выходные обмотки 11-15 ферритовых сердечников резльтата суммы порядка при разных знаках порядков чисел А и в; выходную обмотку 16, вырабатывающую признак переполнения при одинаковых знаках чисел А и В; выходную обмотку 17 определения знака результата сумки чисел при условии, что абсолютная величина числа А больше, чем абсолютная величина числа В или при равенстве абсолютных величин чисел А и в; входные регистры 18 и 19 хранения соответственно чисел А и В в коде 1 из т; вход 20 Операнлы+ ; вход 21 Операнды- ; вход 22 вход 23 первую группу алиментов И 24 для формирования значения суммы чисел при разных и одинаковых знаках чисел/ элемент И 25 для формирования значения суммы чисел при одинаковых знаках чисел (сигнал переполнения); первый элемент ИЛИ 26 для сборки сигналов, соответствующих одновременным знакам чисел А и в; группу элементов .ИЛИ 27 для сборки результатов суммирования чисел при различных комбинациях знаков порядков; третий элемент ИЛИ 29 для сборки сигналов, соответствующих положительному результату; выходной регистр 28 резуль- тата суммирования чисел; вторую группу элементов И 30 для формирования

5 знака результата суммирования чисел; четвертый элемент ИЛИ 31 для сборки сигналов, соответствующих отрицательному результату/ второй элемент ИЛИ 32 для сборки сигна0лов, соответствующих разным знакам чисел А и В.

Устройство работает следующим образом.

При выполнении операции суммирования на регистры 18 и 19 заносят-; ся значения слагаемых в коде 1 из т, а знаки чисел по входам 20-23 поступают на элементы И 30 второй группы и первый и второй элементы ИЛИ 2 и 32. Одна из выходных шин

0 (1-5) входных регистров 18 и 19 возбуждена, что приводит к возбуждению одного вполне определенного ферритового сердечника. Каждый ферритовый сердечник имеет три выходные обмотки, сигналы с которых поступают на входы соответствующих элементов И. В зависимости от знаков чисел формируется результат суммирования, переполнение и знак результата сум0мирования. Результат суммирования чисел в коде 1 из m поступает на , выходной регистр 28, элементы ИЛИ 29 и 31 формируют знак результата, элемент И 25 - сигнал Переполнение. Таким образом, выполнение операции суммирования по любому модулю осуществляется в один такт.

Формулй изобретения

Сумматор по модулю, содержащий два входных регистра, входы которых являются информационными входами суматора и операционный блок, выпол55ненный в виде ферритовой матрицы, инфориационные входы которого соединены с соответствующими выходами входных регистров, отличающийся тем, что, с целью повыtO шения быстродействия, он содержит две группы элементов И, группу элементов ИЛИ, элемент И, четыре элемента ИЛИ, выходной регистр, причем информационные выходы операционного

65 блока соединены с первыми входами

соответствующих элементов И первой группы, выходы каждых двух элементов И первой группы соединены со входами соответствующего элемента ИЛИ группы, выходы элементов ИЛИ группы соединены со входами выходного регистра, выходы которого являются информационными выходами устройства, знаковый выход операционного блока соединен с первыми входами четных элементов И второй группы, выход переполнения операционного блока соединен с первым входом элемента И, выход кот(рого является выходом Переполнения устройства, первые входы первого и второго элементов И второй группы соединены между собой и с первым входом первого элемента ИЛИ и являются входом Операнды+ устройства, первые входы третьего и четвертого элементов И второй группы соединены между собой и со вторым входом первого элемента ИЛИ и являются входом Операнды- устройства, первые входа пятого и седьмого элементов И второ группы соединены между собой и с первым входом второго элемента ИЛИ

и являются входом Л+В- устроПства, первые входы шестого и ьосьмого элементов И второй группы соединены между собой и со вторым входом второго элемента являются е ВХОДОМ А-В+ устройства, выходы первого и второго элементов ИЛИ соединены со вторыми входами соответственно четных и нечетных элементов И первой группы, выходы первого второго, четвертого и восьмого элементов

o И второй группы соединены со входами третьего элемента ИЛИ, выход которого является выходом Результат . устройства, выходы третьего четвертого, шестого и седьмого элементов 5 и второй группы соединены со четвертого элемента ИЛИ, выход которого является выходом Результат- устройства.

0 Источники информации,

принятые во внимание при экспертизе

(прототип).

Авторы

Даты

1981-08-15—Публикация

1979-11-20—Подача