Изобретение относится к аналоговой вычислительной технике и используется в специализированных аналоговых и цифро-аналоговых вычислительных машинах.

Известны аналоговые устройства для вычисления частных производных, содержаш,ие следящие системы независимой переменной и дифференцируемой функции, схему сравнения и блок деления. Однако наличие делительного блока снижает точность вычисления частной производной, так как в делительном устройСТ|ве на динамический диапазон делителя накладываются существенные ограничения.

В предлагаемом устройстве, с целью повыщения точности вычисления применено схемное рещение, при котором .фиксируются приращения функции в моменты возникновения постоянных, наперед заданных, приращений независимой переменной.

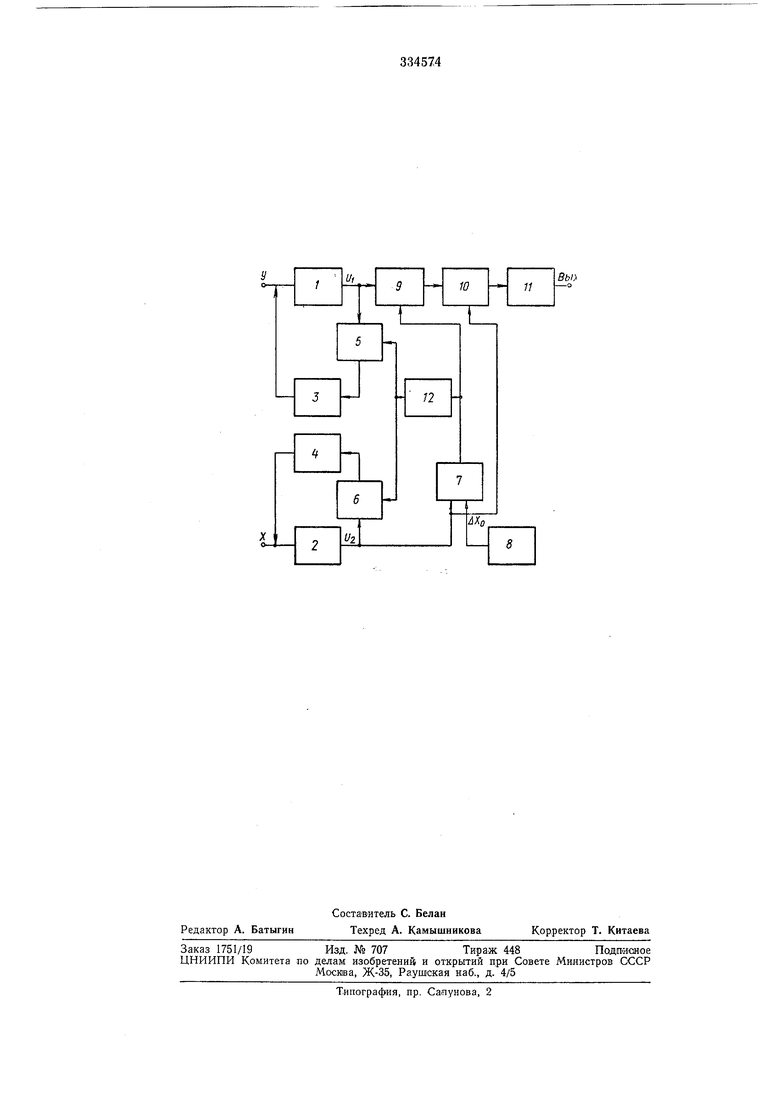

На чертеже приведена блок-схема предлагаемого устройства.

Устройство состоит из двух следящих систем, образованных масщтабнымя устройствами/и 2 интеграторами 3 и 4 соответственно. Выходы масштабных устройств / и 2 соединены со входами интеграторов 3 и 4 через ключи 5 « 6. Выход масштабного устройства 2 соединен с первым входом логического устройства с одним из входов компаратора 7, другой вход которого соединен с опорным источником 8. Выход масштабного устройства / соединен через дополнительный ключ 9 и логическое

устройство 10 с блоком 11 памяти. Выход компаратора 7 соединен с целью управления ключа 9 и через линию задержки 12 с -цепями управления ключей 5 и 6.

Независимая переменная X поступает на

вход масщтабного устройства 2, а функция Y - на вход масщтабного устройства /. Выходом всего устройства служит выход блока 11 памяти. На выходе опорного источника 8 устанавливается постоянное значение выбранного приращения независимой переменной .

Устройство работает следующим образом. При отсутствии импульса с выхода компаратора 7 ключи 5, 6 т 9 разомкнуты. На выходах интеграторов 3 R 4 зафиксированы начальные значения величин У и /f соответственно, на выходе блока // памяти - начальное значение частной .производной, полученное в предыдущем цикле вычисления. При изменеНИИ независимой переменной X на выходе масщтабного устройства 2 появляется сигнал

Одновременно, соответственно виду дифференцируемой функции, на выходе масштабного устройства } появляется сигнал

У ,

где К.1 - коэффициент передачи масштабного

устройства /.

Когда сигнал U-2 станет равным A/Yo, на выходе компаратора 7 появится один импульс, ключ 9 откроется, сигнал U поступит через логическое устройство 10 на вход блока И памяти, и на его выходе будет зафиксирован сигнал

/Ci/Cii-AK,

где /Си - коэффициент передачи блока памяти 11.

Задержанный линией задержки 12 импульс с выхода компаратора поступит в цепи управления ключей 5 и 6. Эти ключи откроются я замкнут следящие системы независимой переменной (блоки 2 и 4) и функции (блоки 1 и 3). Сигналы на выходах интеграторов будут изменяться до тех пор, пока не сравняются со входными сигналами Y и X соответственно. При этом длительность импульса, управляющая работой ключей 5 и &, должна быть достаточной для отработки следящими системами приращений ЛК и AJ соответственно.

При исчезновении управляющего импульса в цепях управления ключей 5 и 6 интеграторы 5 и 4 автоматически оказываются в режиме памяти, а на выходах масштабных устройств / и .2 сигналы равны нулю. При появлении новых приращений независимой переменной цикл работы устройства повторяется.

Запомненный блоком 11 памяти выходной сигнал устройства, равный

,

при достаточно малом значении выбранной величины можно считать точным значением

„ дУ„ „

частной производной . Действительно,

дХ

величина - постоянна, поэтому сигнал на выходе блока // памяти

АГ

/Сг/С„-ДГ /С Д

где

-./С./С„ const.

При достаточно малом

к к.

ДХдХ

Выбор определяется чувствительностью и быстродействием компаратора 7, а также коэффициентом передачи масщтабного устройства 2, так как компаратор 7 выдает импульс при выполнении равенства

/С2АХ AXo+:.,

где t/2 - чувствительность компаратора.

Знак напряжения на выходе блока памяти 0 определяется работой логического устройсгва W, пропускающего сигнал f/i на вход блока 11 памяти, если знаки Х и AF совпадают, и инвертирующего сигнал Ui - при несовпадении знаков и АУ.

гт

Предмет изобретения

Устройство для вычисления частной производной, содержащее следящую систему независимой переменной и следящую систему дифференцируемой функции, выполненные на интеграторах, входы которых через соответствующие ключи соединены с выходами соответствующих масштабных устройств, и компаратор, к одному из входов которого подключен

5 ИСТОЧНИК опорного напряжения, отличающееся тем, что, с целью повышения точности вычисления, оно содержит линию задержки, логическое устройство, блок памяти и дополнительный ключ, причем выход масштабного устройства следящей системы независимой переменной соединен с первым входом логического устройства и другим входом компаратора, выход компаратора соединен с управляющим входом дополнительного ключа, соединяющего

5 выход масштабного устройства следящей системы функции с вторым входом логического устройства, к выходу которого подключен блок памяти, и через линию задержки - с управляющими входами ключей следящих систем.

Вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления частной производной | 1983 |

|

SU1105913A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| ВПТБ | 1973 |

|

SU397941A1 |

| АВТОРУЛЕВОЙ, РЕАЛИЗУЮЩИЙ ПРОПОРЦИОНАЛЬНО- ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ ЗАКОН УПРАВЛЕНИЯ | 1968 |

|

SU213943A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 2007 |

|

RU2359322C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ С ПЕРЕМЕННЫМИ КОЭФФИЦИЕНТАМИ | 2009 |

|

RU2419141C2 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2002 |

|

RU2222828C1 |

| АДРЕСУЕМАЯ ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 2010 |

|

RU2427033C1 |

| Дифференцирующее устройство | 1979 |

|

SU817729A1 |

| Ячейка однородной структуры для решения дифференциальных уравнений в частных производных | 1979 |

|

SU783811A1 |

Даты

1972-01-01—Публикация