Изобретение относится к области цифровых интегрирующих машин и может быть использовано для яостроеНИя основных решающих блоков цифровых дифференциальных анализаторов (ЦДЛ) параллельного типа.

Совершенствоваиие технологических нроцессов, лежащих -в основе цикла производства интегральных схем, создало возможность значительного повышения степени интеграции комлОНентов и перехода к .большим интегральным схемам (БИС), содержащим десятки и даже сотни логических элементов. Широкое использование БИС лри конструировании вычислительной аппаратуры существенно уменьшает ее Габариты и вес, значительно повышает ее надежность, снижает затраты в пересчете на один логический элемент, позволяет повысить быстродействие логических элементов и снизить потребляемую ими мощность.

Однако подготовка и налаживание производства каждого нового типа БИС является трудоемким процессом, требующим большой затраты в-ремени, поэтому БИС могут быть изготовлены только для тех вычислительных устройств, которые имеют широкое применение и могут быть построены с помощью БИС небольшого числа типов.

Главная проблема при проектировании больших интегральных схем для основания решающих блоков ЦДЛ параллельного типа.

каК и для любых других вычислительных устройств, заключается в необходимости предельной минимизации числа типов БИС. Известны схемы основных решающих блоков на дискретных компонентах: цифрового интегратора, реализующего численное интегрирование по методу прямоугольников или трапеций, следящего интегратора, масштабного интегратора и сумматоров приращений

для цифрового и следящего интегратора.

Полное выполнение принципа максимальной интеграции (т. е. минимизация общего количества БИС) для ЦДЛ параллельного типа означает необходимость изготовления

пяти специальных БИС (по числу основных решающих блоков), не считая последовательного регистра сдвига, который является схемой общего назначения. Известно, что по такому принципу для

ЦДЛ параллельного типа разработаны специальные БИС на МОП-транзисторах, используемые совместно с регистрами сдвига: логический блок МЕМ5021 цифрового интегратора, реализующего численное интегрирование по э.кстраполяционной формуле прямоугольников, логический блок MEAVSOSl следящего интегратора и сумматор двух приращений МЕМ5035 для цифрового интегратора (первая и вторая БИС содержат всю логичеторов, управляющую работой регистров сдвига).

Однако в этом комплекте отсутствуют в настоящее время сумматор приращений для следящего интегратора и логический -блок масштабного интегратора, хотя использовать вместо последнего логический блок цифрового интегратора неэкономично.

При разработке БИС для построения основных решающих блоков ЦДА параллельного типа необходимо изготавливать пять типов специальных BPiC (не считая регистра сдвига) ,и нестандартные громоздкие корпуса с 24 выводами для герметизации БИС цифрового и следящего интеграторов.

Степень интеграции, необходимая для изготовления логического блока цифрового и следящего интеграторов, довольно высока. Например, при .изготовлении больщой интегральной схемы МЕМ5021 требуется 240 компонентов- МОП-транзисторов. Такое требование является довольно жестким для сегоднящнего уровня развития микроэлектронной технологии.

Целью изобретения являются:

уменьшение с пяти до двух числа типов специальных БИС, необходимых для построения .пяти основных решающих блоков ЦДА параллельного типа: масштабного, .цифрового и следящего интеграторов, сумматоров приращений для цифрового и следящего интеграторов, что приводит к сокращению расходов на подготовку и налаживание производства БИС такого назначения, и на изготовление и обслуживание аппаратуры на них;

улучшение технологичности производства специальных БИС благодаря снижению требований к необходимой максимальной степени интеграции (требуется около 150 компонентов - МОП-транзисторов при производстве наиболее сложной из двух специальных БИС) и возможности использования для герчетизации всех БИС только ста:Нда|ртных, ;ерийно выпускаемых корпусов с 14 выводами;

расширение технических возможностей комплекта БИС для реализации на них численного интегрирова.ния не только по экстраноляционной формуле прямоугольника, но и по более точной экстраполяционной формуле трапеций.

Сущность изобретения состоит в том, что в качестве основы для двух специальных субсистем использованы сумматор двух приращений и логический блок масщтабного интегратора, в введены новые элементы и схемы коммутации, позволяющие менять режим работы специальных субсистем при построении из них различных реш:ающих блоков.

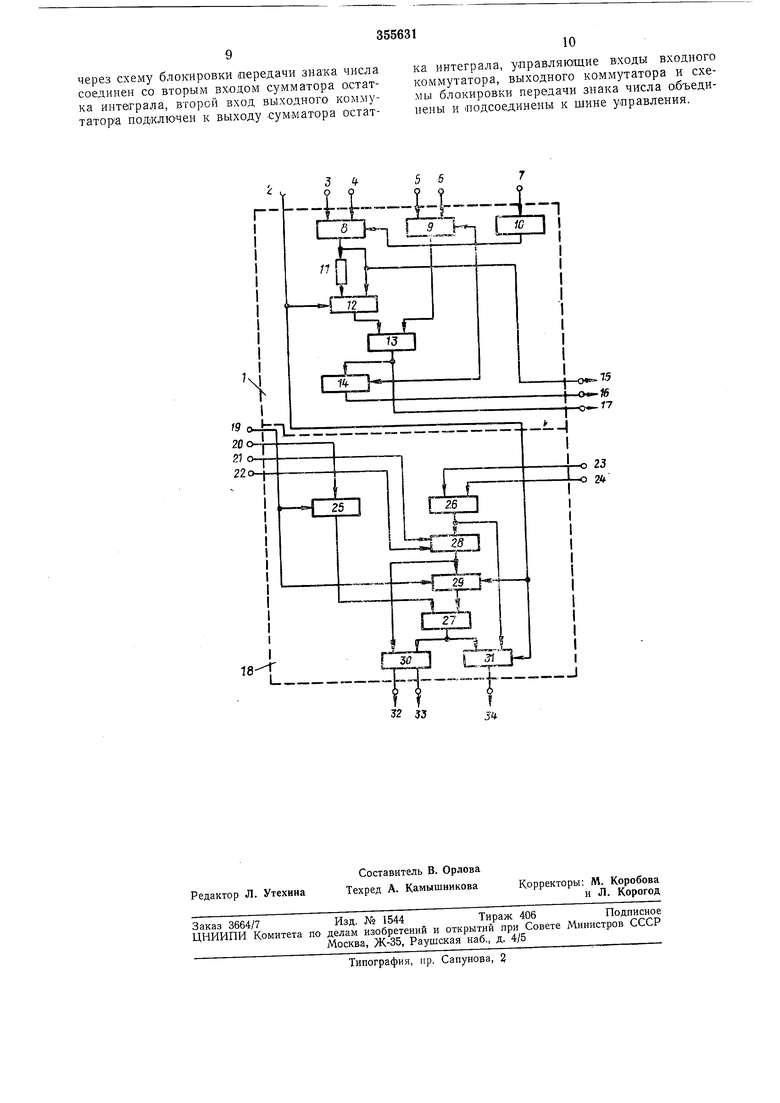

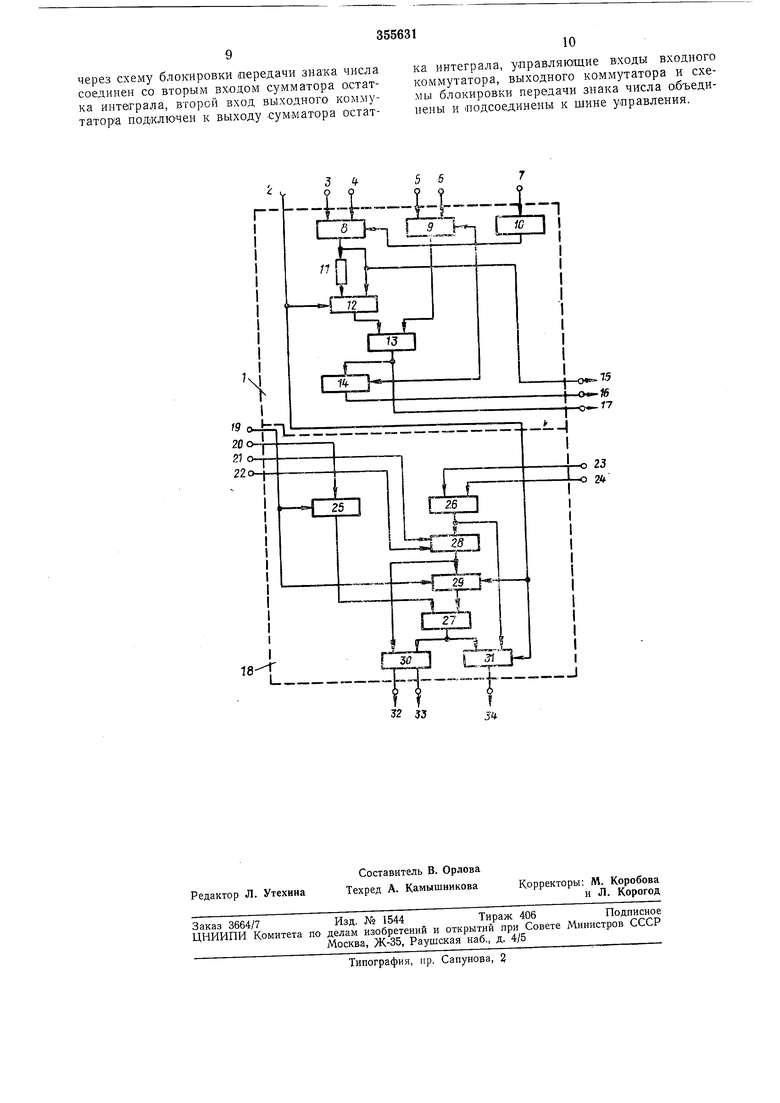

Обработка информации в субсистемах осуществляется последовательно разряд за разрядом в двоичной системе счисления. Отрицательные числа записываются дополнительным кодом. Для записи знака числа выделяется один разряд. Работа всех субсистем синхронизируется главными импульсами (ГИ), совпадающими по в-ремени с поступлением из регистра знаковых разрядов чисел. 5 Используется тернарная система кодирования приращений и способ квантования приращений интеграла, при котором содержимое / -регистра всегда положительно и ограничивается величинами О и 1 (.). 10 Иа чертеже изображена блок-схема решающего блока ЦДА параллельного типа, где: 1-первая специальная субсистема, 2 - вход управления, 3, 4 - входы -Дг/, 5, 6 - и входы -fAz/, 7 - вход схемы синхропизации, 15 8, 9 - схемы преобразования приращений, 10 - схема синхропизации, 11 - элемент задержки на один такт, 12 - входной коммутатор, 13 - сумматор подынтегральной функции, 14 - схема стирания начального им20 пульса, 15 - выход выдачи половины приращения подынтегральной функции, 16 - выход выдачи нового значения подынтегральной функции без начального импульса, 17 - выход полного сумм.атора 13, 18 - вторая спе5 циальная субсистема, 19-вход подачи главного импульса (ГИ), 20-вход подачи остатка интеграла, 21, 22-входы приращений независимой переменной, 23, 24-входы сумматора 27, 25 - схема восстановления знака 0 остатка и.нтеграла, 26 - дополнительный сумматор, 27-сумматор для полного остатка интеграла, 28 - множительное устройство, 29 - схема блокировки передачи зпака числа, 30-схема выделения приращения интеграла, 5 31 - выходной коммутатор, 32, 33 - выходы схемы 30, 34 - выход коммутатора 31.

Первая специальная субсистема построена на основе сумматора двух приращений, в состав которого входят схемы преобразования 0 приращения 8 и 9, схемы синхронизации 10 и полный последовательный сумматор 13. В сумматор приращений введены дополнительные схемы: элемент задержки 11, схема коммутации 12, схема 14 стирания начального 5 импульса, и, кроме того, система имеет дополнительные выходы: выход 15 со схемы преобразования приращения 8 и выход 16 со схемы 14 стирания начального импульса.

Субсистема имеет два режима работы, 0 выбор каждого из которых осуществляется подачей соответствующего напряжения на вход управления 2 схемой коммутации 12. В одном режиме эта субсистема может быть использована как сумматор двух приращений 5 на входе цифрового или следящего интеграторов и как составная часть следящего интегратора, а в другом - как составная часть цифрового интегратора, реализующего численное интегрирование по экстраполяционным 0 формулам прямоугольников или трапеций.

Схема синхронизации 10 управляет работой схем 8, 9 и 14. Схема синхронизации содержит элемент памяти - триггер, который к началу каждой итерации устанавливается главными импульсами в «нулевое состояние,

а затем переходит в «единичное состояние после подачи на вход 7 напряжения t/i, соответствующего логической единице (напряжение, соответствующее логическому нулю, обозначается через UQ).

Схемы 8, 9 преобразуют приращения, задаваемые на входы 3-6 потенциалами в тернарной системе кодирования, в соответствующие последовательные коды.

Выдача этих кодов начинается одиовремен.но с приходом логической единицы на вход 7 схемы сиихронизации 10. Приращение }, задаваемое напряжениями (/i на входе -Дг/ (3 или 4) и напряжениями UQ на парном ему входе +Аг/ (5 или 6} можно рассматривать как последовательный код 1, 11 ... 11 на .входе -At/, пропускаемый без изменения через схему преобразования приращения. Поэтому функции, выполняемые схемами 8 и 5, легко могут быть расширены. Эти схемы могут пропускать последовательный код i6e3 изменения при подаче его на вход -Дг/, если на парный ему вход +ДУ подается напряжение UQ. Это позволяет обойтись без двух дополнительных входов, необходимых при подаче в эту субсистему последовательных кодов.

При напряжении Ь на входе управления 2 коммутатор 12 пропускает па вход сумматора 13 информацию непосредственно с выхода схемы 8, а при напряжении UQ - эту же информацию, задержанную иа один такт элементом задержки 11. Схема 14 осуществляет стирание начального имиульса числа, поступаюпхего с выхода сумматора 13 на выход 16 субсистемы.

Вторая специальная субсистема построена на основе логического блока масщтабного интегратора, в состав которого входят схемы 25 восстановления знака остатка интеграла, множительное устройство 28, сумматор для полного остатка интеграла 27 и схемы 30 выделения приращения интеграла. В этот блок введены дополнительные схемы: сумматор 26, схема 29 блокировки передачи знака числа и выходной коммутатор 31, а схема 25 восстановления остатка интеграла перенесена с выхода сумматора 27 на его вход 20.

Вторая специальная субсистема также имеет два режима работы, выбор каждого из которых осуществляется подачей соответствующего напряжения на вход управления 2. В одном режиме эта субсистема может быть использована как составная часть следящего интегратора, а в другом - как логический блок масщтабного интегратора или как составная часть интегратора, реализующего численное интегрирование по экстраПОЛЯ1ЦИОННЫМ формулам прямоугольников или трапеций.

Схема 25 восстанавливает знак остатка интеграла в момент поступления на ее вход 19 главного импульса. Схема 28 умножает число, поступающее с выхода сумматора 26 на приращение независимой переменной , которое подается на входы 21, 22 субсистемы. При напряжении t/i, на входе управления 2 схема 29 блокирует передачу знака числа с выхода множительного устройства 28, записывая всегда на месте знакового разряда логический нуль, а при напряжении t/o пропускает это чИСло без изменения.

Схема 30 формирует приращение Дг на выходах 32, 33 .субсистемы после анализа знакового разряда неокругленного приращения интеграла на выходе множительного устройства 28 и знакового разряда суммы неокругленного приращения интеграла и остатка интеграла предыдущего шага интегрирования,

которая образуется на выходе сумматора 27. При напряжении t/i на входе управления 2 коммутатор 31 пропускает на выход 34 субсистемы информацию с выхода сумматора 26, а при напряжении UQ-информацию с выхода сумматора 27.

При использовании первой специальной субсистемы для суммирования двух приращений на вход 2 подается напряжение U и поэтому выход схемы 8 связан непосредственно с входом сумматора 13. Суммируемые приращения поступают на входы 3-6. Результат суммирования снимается с выхода 17 субсистемы, а выходы 15 и 16 при суммировании приращений не используются.

В сумматоре приращений, работающем на входе цифрового интегратора, на вход 7 подается информация с выхода У-регистра.

Поэтому суммирование начинается одновременно с поступлением на вход 7 начального импульса. В сумматоре приращений, работающем на входе следящего интегратора, на вход 7 .подается напряжение LJi, и поэтому суммирование начинается всегда в первом же такте очередного щага вычислений (в следующем также после прихода главного импульса). Поскольку в структуру следящего интегратора входит сумматор приращений, первая специальная субсистема, работающая в таком режиме, является составной частью

следящего интегратора.

Первая специальная субсистема позволяет сум Мировать приращения более, чем от двух источников путем наращивания этих субсистем. При этом результат промежуточного

суммирования в виде последовательного кода подается на вход 3 или 4 (вход -Ду) следующей субсистемы, причем на парный ему вход +Аг/подается напряжение Uf,.

Первая специальная субсистема может быть использована и как составная часть цифрового интегратора, в которой образуется новое значение подынтегральной функции. В этом случае на входы 2 и б подается напряжение f/o, а на входы 4 и 7 - старое значение подынтегральной функции с выхода У-регистра, которое проходит без изменения через схему 9. Входы 5 и 5 используются для подачи очередного приращения или суммы

пает на вход сумматора 13 через элемент задержки 11.

С выхода 17 снимается новое значение подынтегральной функции вместе с начальным импзльсом, которые подаются на вход У-регистра, а с выхода 16 - только новое значение .подынтегральной функции, которое подается во вторую специальную субсистему для суммирования с остатком приращения интеграла предыдущего шага интегрирования. На выход 15 поступает последовательный код, соответствующий половине поданпого па входы 3, 5 приращения или суммы приращений.

Сигналы с -ВЫХОДОВ 15 и 16 суммируются во второй -специальной субсистеме при реализации численного интегрирования -по экстраполяционной формуле трапеций.

При использовании второй специальной субсистемы в качестве логического блока масштаб-ного интегратора или составной части цифрового интегратора на -вход управления 2 полается напряжение f/o, Поэтому число с выхода множительного устройства 28 проходит на вход сумматора 27 без всяких изменений. В масштабном интеграторе на один Из входов 23. 24 сумматора 26 подается информация с выхода У-регистра, а на другой - напряжение Ur,. В цифровом интеграторе на один из ВХОДОВ 23, 24 сумматора 26 подается новое значение подынтегральной функции с выхода 16 первой специальной субсистемы, на другой - или напряжение f/o (интегрирование по формуле -Прямоугольников) или половина приращения подынтегральной функции с выхода J5 первой специальной субсистемы Синтегоирование по формуле траиеций). На вход 20 в масштабном и -цифровом интеграторах поступает содержимое / -регистра, которое складывается на сумматоре 27 с числом, поступающим с выхода множительного устройства 28.

Новое значение остатка интеграла с выхода сумматора 27 поступает через выходной коммутатор сЗ/ на вход / -регистра. а НОВОР значение приращения интеграла снимается с выходов 32, S3.

При использовании второй специальной субсистемы в качестве составной части следящего интегратора на вход управления 2 подается напряжение C/i. Схема 29 блокирует передачу знака числа на выходе сумматора 26, записывая всегда «а месте знака логический нуль. На один из входов 2S, 24 -подается содержимое накапливающего регистра следящего интегратора, на другой - сумма приращений с выхода 17 первой специальной субсистемы. На вход 20 подается напряжение f/j, которое преобразуется схемой 25 ъ последовательный код О, 11 ... 11.

Наличие на выходе сумматора 26 любой величины, отличной от нуля, в результате сложения с кодом О, И ... 11 на сумматоре 27 всегда вызывает перенос из старшего оазряда в знаковый разряд- Поскольку передача кода

ЗНакового разряда числа на выходе множительнОГо зстройства 28 блокируется схемой 29, то обеспечивается однообразие в определении переполнений для цифрового и следящего интеграторов. Новое значение содержимого накапливающего регистра поступает в пего с выхода сумматора 26 через выходной коммутатор 31, а новое приращение снимается с выходов 32, 33.

Таким образо.м, введение сумматора 26 и схемы блокировки 29 в структуру логического блока масштабного интегратора дает -возможность Эффективно использовать вторую специальную субсистему не только в масштабном

интеграторе и цифровом интеграторе, реализующем численное интегрирование по экстраполяционной формуле прямоугольников, но и в следящем интеграторе, и в цифровом интеграторе, реализующем численное интегрирование по экстраполяционной формуле трапеций. Перенесение схемы 25 восстановления знака остатка интеграла с выхода сумматора 27 на его вход позволяет наиболее простым способом, без затрат дополнительного оборудования (регистра сдвига) организовать подачу на .вход сумматора 27 кода О, 11 ... 11, необходимого при использовании Этой субсистемы в следящем интеграторе.

Введение дополнительного выходного коммутатора 31 сокращает на один число выводов « мощных выходных «аскадов субсистемы.

Предмет изобретения

Решающий блок для цифрового дифференциального анализатора, содержащий схему синхронизации, выход которой подсоединен к управляющим входам первой и второй схем преобразования приращений и схемы стирания начальных импульсов, сумматор подынтегральной функции, выход которого подключен ко входу схемы стирания начальных импульсов, а первый вход - к выходу второй схемы преобразования приращений, множительное

устройство, выход которого соединен с первым входом схемы выделения приращений интеграла, и схему восстановления знака остатка интеграла, выход которой соединен с первым ВХОдом сумматора остатка интеграла, выход которого подключен ко второму входу схемы выделения приращения интеграла, отличающийся тем, что, с целью расщирения его функциональных возможностей, он содержит дополнительный сумматор, схему блокировки

передачи знака числа, выходной коммутатор, линию задержки и входной коммутатор, выход которого подключен ко второму вход сумматора подынтегральной функции, выход первой схемы преобразования приращений

подключен к первому Входу входных коммутаторов и через линию задержки ко второму входу вход71ого коммутатора, выход дополнительного сумматора .подсоедине) к первому входу выходного коммутатора и ко входу

через схему блокировки передачи знака числа соединен со вторым входом сумматора остатка интеграла, второй вход выходного коммутатора подключен к выходу сумматора остатка интеграла, управляющие входы входного коммутатора, выходного коммутатора и схемы блокировки передачи знака числа объединены и подсоединены к шине управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU328482A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО АНАЛИЗАТОРА | 1968 |

|

SU217075A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| ДЕТЕРМИНИРОВАННО-ВЕРОЯТНОСТНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU428412A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Цифровой интегратор | 1979 |

|

SU805362A1 |

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU291216A1 |

| Цифровой интегратор | 1974 |

|

SU519735A1 |

3 Ч5 6

ifcrab ичди жщд-цЛ

1

Авторы

Даты

1972-01-01—Публикация