Изобретение .может быть использовано в системах |раииотеламетри и, связи, фототелеграфии и телевидения.

Известла система связи с дельта-модуляцией, в которой осуществляется коррекция ошибок IB условиях помех и временных нарушений СВЯ31И за .счет введбн.ия .в кодируюш,/ий и декодирующий узлы делителя частоты, схемы строб,ирова1ния и управ-ляемых этой схемой вентилей. В такой системе при совпадении во времени процесса коррекции и быстрых изменений сигнала часть информации, представляющая интерес для получателя, может быть утеряна по нричиие (конеч.ной длительности процесса коррекции, в течение .которой .могут происходить флюктуации, скачки и т. п. исходного силнала.

Цель изобретения - коррекция ошибок только при 41едлан,ных .изменениях исходного сигнала. Достигается это тем, что IB передающей части исходный сигнал дополнительно подай через дифферегщирующий каскад на детектор:ный блок, два выхода которого соответственио через огра Н1ИЧитель снизу и ограничитель сверху подключен ко .входам залираюЩего -каскада, по.дключен.ного к дополнительному входу схемы строби.рован:ия, а в приемной части исходный сигнал дополнительно подан через интегратор, фильтр нижних частот и дифференцирующий каскад иа детекторный

олок, два выхода которого соответственно через ограничитель снизу IH ограничитель сверху подключе}1ы ко вхо.дам запирающего каска.да, по.дключеиного к дополнительноиму входу схемы стробирования.

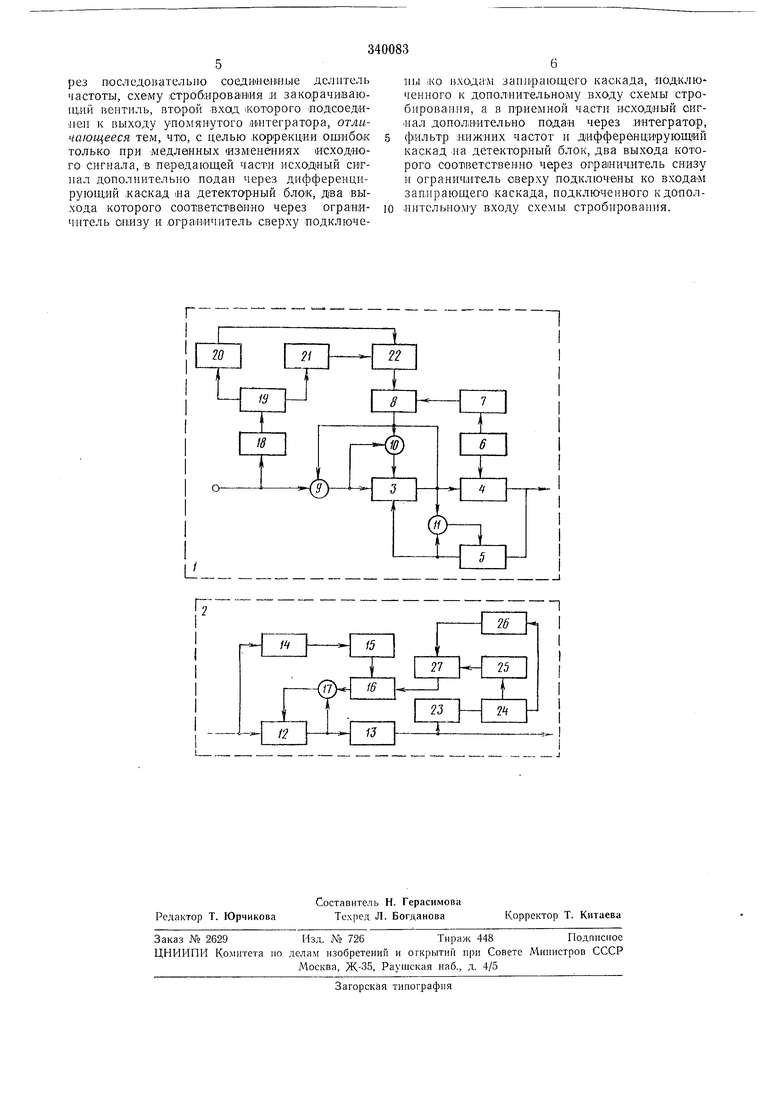

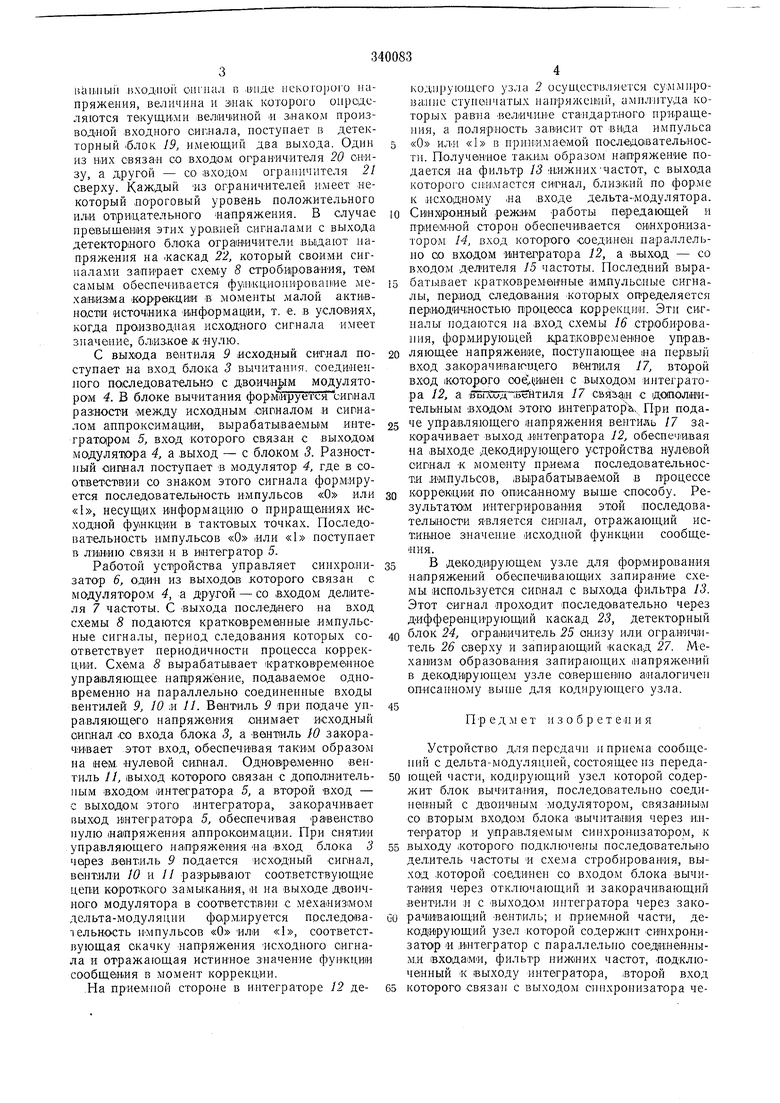

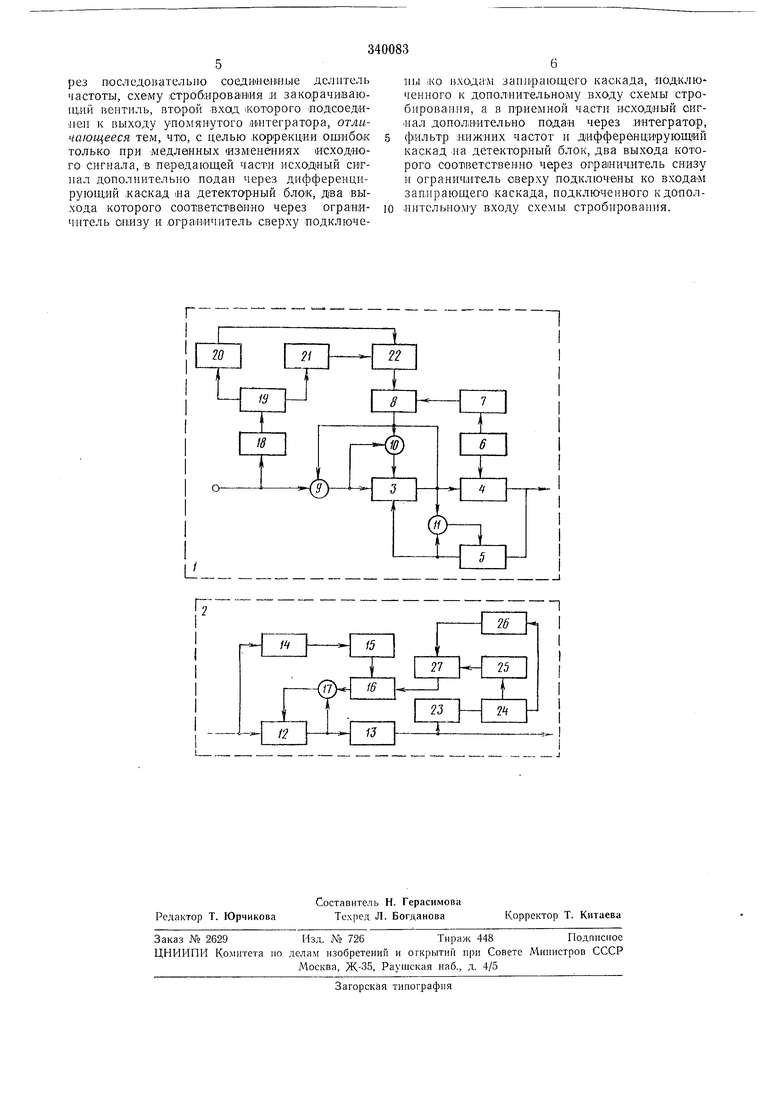

На чертеже приведена функциональ:ная схема предлагаемого устройства.

Устройство имеет кодирующ1ИЙ 1 и декодирующий 2 узлы. КодируюЩ|ИЙ узел содержит

блок 3 вычитания, двоичный модулятор 4, интегратор 5, синхроиизатор 6, делитель 7 час.тоты, схему 8 стробирования, отключающий 9 и закорачивающие 10 и 11 вентили; декодирующий- интегратор 12, фильтр /5 .нижних частот, синхронизатор М, делитель 15 частоты, схему 16 стробирования и закорачивающий вентиль 17.

KpoiMe того, в ко.днрующ;ий узел входят диффере:}щирующ1ий ;каска.д 18, детекторный

блок 19, ограничитель 20 снизу, огран1ичитель 21 сверху и запирающий каскад 22; в декодирующий - дифференцирующ,ий каскад 23, детекторный бло.к 24, ограничитель 25 снизу, ограничитель 26 сверху и запирающий каск ад 27.

Устройство работает сле|дующ1им образом. В кодирующем узле 1 передаю.щей стороны исходный сигнал одновременно подается на ВХО.Д дифференцнрующего .каскада 18 и вход

iiaiMibiii HxoAiiioit сигнал n .виде iieKOTO)Oio напряжения, величина и 31нак Koxopoio определяются текущимн величиной -и 3(Наком производной входного сигнала, поступает в детекторный блок 19, Н1меющий два выхода. Один из них связан со входом ограничителя 20 сиизу, а другой - со ;входом ограличнтеля 21 сверху. Каждый из ограничителей имеет некоторый .пороговый уровень положительного или отрицательного напряжения. В случае превышения этих уро.вней сигналами с выхода детекторного блока ограничители выдают напряжения на .каскад 22, который своими сигналами за1ПИрает схему 8 стробироваиия, тем самым обеспечивается функционирование механизма «оррвкции в моме}1ты малой активно,ст1И истоЧ(Н1Ика информации, т. е. в условиях, когда производная исходного сигнала имеет значение, блиакое к нулю.

С выхода вентиля 9 исходный сигнал поступает на вход блока 3 вычитания, соединенного последовательно с двоичньгм модулятором 4. В блО:Ке вычитания формируегся сигнал раз;ности между исходным сигналом и сигналом аппроксимации, вырабатываемью интегратаром 5, вход которого связан с выход0:М модулятора 4, а выход - с блоком 5. Разностный оилнал поступает в модулятор 4, где в соответствии со знаком этого сигнала формируется последовательность импульсов «О или «1, несущих информацию о приращениях исходной функции в тактовых точках. Последовательность импульсов «О или «1 поступает в линию связ:и И В интбгратор 5.

Работой устройСтва управляет синхронизатор 6, один из выходов которого связан с модуляторОМ 4, а другой - со входом делителя 7 частоты. С выхода последнего на вход схемы 8 подаются кратковременные импульсные сигналы, период следования которых соответствует периодичности процесса коррекции. Схема 8 вырабатывает 1кратковрем€1нное упра1вляющее на цряжение, подаваемое одновременно на параллельно соединенные входы венти.Чей 9, 10 и 11. Вантиль 9 при подаче управляющего напряжения онима-ет исходный онпнал .со входа блока 3, а ввнт1иль W закорачивает этот вход, обеспечивая таким образом на нем. .нулевой снлнал. Одновременно вентиль //, выход которого связан с дополнительным входам интегр.атора 5, а второй -вход - с выходом этого интегратора, закорачивает выход интегратора 5, обеспечивая равенство нулю (Напряжения аппроксимации. При снятии управляющего наиряжения на вход блока 3 через в ентиль 9 подается исходный сигнал, вентили 10 л и разрьрвают соответствующие цепи короткого замыкания, и на выходе двоичного модулятора в соответствии с механизмом дельта-модуляции формируется последовательность импульсов «О или «1, соответствующая скачку напряжения исходного сигнала и отражающая истинное значение функции сообщения в момент коррекции.

од:прукяцсго узла 2 осун1,ествляется су:ммнрование ступенчатых напряжений, амплитуда которых равна величЕНе ста ндарт.ного приращения, а полярность зависит от вида импульса

5 «О ил.и «1 в принимаемой последовательности. Полученное такиам образом напряжение подается на фильтр 13 1шжних-частот, с выхода которого сн:и1мается сигнал, близкий по форме к исходному на входе дельта-мо.дулятора.

10 Синх1ро.нный режим работы передающей и прием.ной сторон обеспечивается синхронизатором 14, вход которого .соединен параллельно со входом интегратора 12, а выход - со входом .делителя 15 частоты. Последний вырабатывает кратковременные .им.пульсные сигналы, период следо1вания которых определяется периодичностью П роцеоса коррекци1И. си.гналы .даются на вход схемы 16 строб.ирования, формирующей к.ратковременное управляющее напряжение, поступающее на первый вход закорачи1ваюихего Вбн-лиля 17, второй вход которого сое;(1И1нен с выходом интегратора 12, а щшхиДТосйтиля 17 связд Н с дополиительным .входом этого и.нтегратор,. При подаче упра.вляющего напряжения вентиль 17 закорачивает выход интегратора 12, обеспечивая на выходе .декодирующего устройства нулевой сигнал к моменту приема послвдо;вательности импульсов, вырабатываемой в процессе 0 коррекции по опи.санному выше способу. Результатом интегрирования этой последовательности является сигнал, отражающий истинное значение ..исхо.диой функции сообщения.

В декодирующем узле для формирования напряж.еиий оббспечиваюЩ|ИХ запирание схемы используется сигнал с выхода фильтра 13. Этот сигнал ирохо.дит последовательно через дифференцируюЩ|ИЙ каскад 23, детекторный

0 блок 24, огран1ич.итель 25 он.изу или ограничитель 26 сверху и запирающий каска.д 27. Мехаиизм образования запирающих напряжений в декодирующем узле совершенно а налогичен описаиному выше для ко.дирующего узла.

пред м е т и з о б р е т е .н и я

Устройство для передачи и приема сообщений с дельта-модуляцией, состоящее из передающей части, кодирующий узел которой содержит блок вычнтания, последовательно соединенный с двоичным модулятором, связан.иы1М со iBTOpbiM входом бло1ка вычита|Ния через интегратор и управляемым синхронизатором, к

выходу .которого подклЕочены последо;вательно делитель частоты и схема стробирования, выхад которой соединен со входом блока вычитания через отключающ.ий и закорачивающий .вентили и с выходом интегратора через закорачивающий -вентиль; и пр:ием.ной части, деко:ди1рующий узел которой содержит синхрониато1р и интегратор с параллельно соеднненным.и входами, фильтр нижних частот, .подклюенный к выходу интегратора, второй вход

рез последоиателыю соединенные делитель частоты, схему ;стро:б;ирова1Н1Ия .и закорачивающий вбнтиль, второй вход iKOTOporo подсоедиiUEii к выходу упомянутого интегратора, отличающееся тем, что, с целью .коррекции ошибок только при медленных изм енениях исходиого сигнала, в передающей части исходный сигнал дополнительно подан через дифференцирующий .каскад 1иа детекторИый блок, два выхода которого соответственио через ограняЧитель снизу и ,огра1Н1Ичитель сверху иодключеиы iKo (ходаМ зашфающего каокада, -подключенного к дополнительному входу схемы стробирования, а в приемной части исходный оигнал допол|НИтель«о подан через :и нтегратор, ф1ильтр :Н:ижИих частот и дифференцирующий каскад на детекторный блок, два выхода которого cooTiBeTCTBeHiHO через огра1НиЧ|Итель сиизу и ограничитель сверху подключеиы ко входам зап.ирающего каскада, подключениого кдололлителыному входу схемы стробировап.ия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи с дельта-модуляцией | 1973 |

|

SU479249A1 |

| СИСТЕМА СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1971 |

|

SU296252A1 |

| Система связи с дельта-модуляцией | 1976 |

|

SU649135A2 |

| Устройство для передачи сигналов с дельта-модуляцией | 1976 |

|

SU577695A1 |

| Устройство для передачи сигналов с дельта-модуляцией | 1987 |

|

SU1420672A2 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ СИГНАЛОВ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1991 |

|

RU2025045C1 |

| Устройство для передачи и приема сообщений | 1977 |

|

SU641488A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Устройство для передачи сигналов с периодической коррекцией | 1986 |

|

SU1367160A1 |

Г

L

1

П

Авторы

Даты

1972-01-01—Публикация