нижних частот 18, синхронизатор 19, делитель частоты 20, схему стробирования 21, закорачивающий вентиль 22, дифференцирующий каскад 23, детекторный блок 24, ограничитель снизу 25, ограничитель сверху 26 и запирающий каскад 27.

Кроме того, в кодирующий узел входят детектор последовательности 28 и схема запрета 29. Схема запрета имеет два входа; основной, связанный с выходом схемы стробирования 8, и запрещающий, связанный с выходом детектора последовательности.

Устройство работает следующим образом.

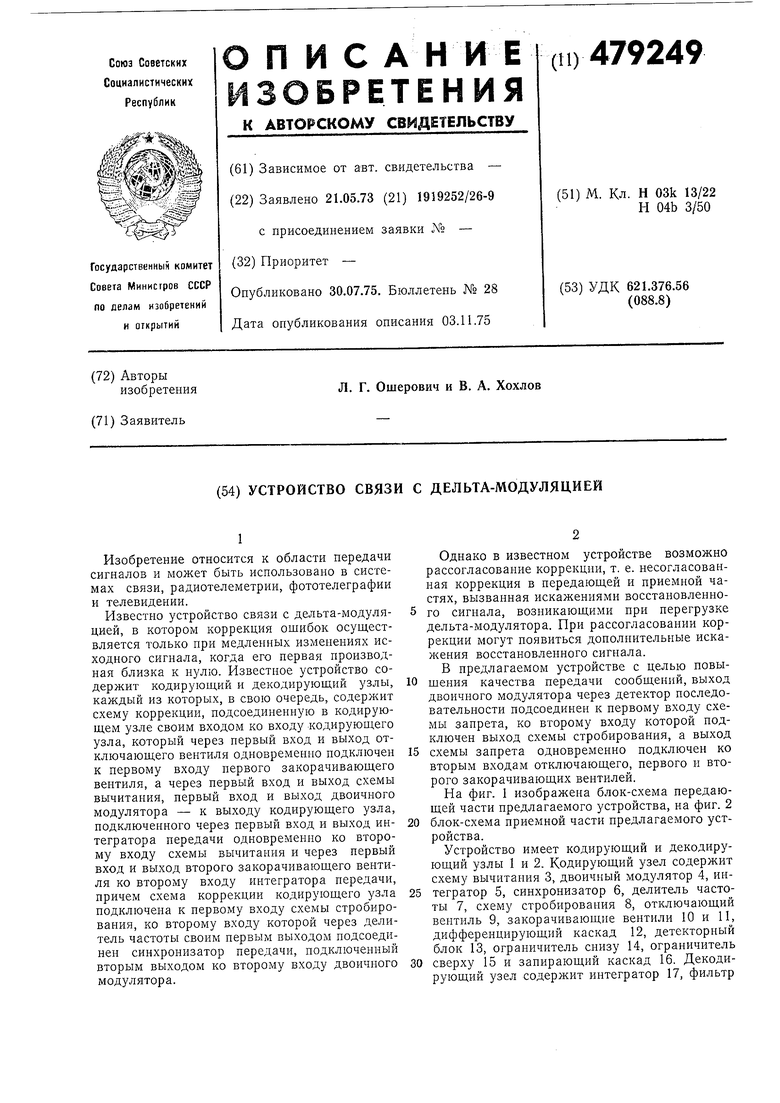

В кодирующем узле 1 передающей части исходный сигнал t/i одновременно подается на вход дифференцирующего каскада 12 и вход отключающего вентиля 9. Продифференцированный входной сигнал в виде некоторого напряжения, величина и знак которого определяются текущими величиной и знаком производной входного сигнала, поступает в детекторный блок 13, имеющий два выхода. Один из них связан со входом ограничителя снизу 14, а другой - со входом ограничителя сверху 15. Каждый из ограничителей имеет пороговый уровень положительного или отрицательного напряжения. В случае превышения этих уровней сигналами с выхода детекторного блока ограничители выдают напряжения на запирающий каскад 16, который своими сигналами запирает схему стробирования 8. Если же первая производная исходного сигнала имеет значение, близкое к нулю, то сигнал с выхода детекторного блока не достигает порогового уровня ограничителей, и ограничители не выдают напряжение на запирающий каскад, который при этом открывает схему стробирования 8. Таким образом осуществляется управление работой механизхма коррекции в кодирующем узле самим исходным сигналом.

С выхода вентиля 9 исходный сигнал поступает на вход схемы вычитания 3, соединенной последовательно с двоичным модулятором 4. В схеме вычитания формируется сигнал разности между исходным сигналом L/i и сигналом аппроксимации Us, вырабатываемым интегратором 5, вход которого связан с выходом двоичного модулятора 4, а выход - со схемой вычитания 3. Разностный сигнал поступает в двоичный модулятор 4, где в соответствии со знаком этого сигнала (формируется последовательность ,импульсов «-1 или «+1, несущих информацию об изменении исходного сигнала. Последовательность t/4 импульсов «-1 и «+1 поступает в линию связи, в интегратор Бив детектор последовательности 28, выход которого связан с запрещающим входом схемы запрета 29.

Детектор последовательности запоминает несколько последних импульсов с выхода двоичного модулятора 4 и в том случае, если все они имеют одинаковую полярность, что свидетельствует о перегрузке дельта-модулятора, выдает сигнал на схему запрета 29. При этом схема запрета отключает схему стробирования 8 от вентилей 9, 10 и И. 1аким образом обеспечивается прекращение функционирования механизма коррекции в кодирующем узле при перегрузке дельта-модулятора. Работой устройства управляет синхронизатор 6, один из выходов которого связан с модулятором 4, а другой - со входом делителя

частоты 7. С выхода последнего на вход схемы стробирования 8 подаются кратковременные импульсные сигналы Uz, период следования которых соответствует периодичности процесса коррекции. В открытом состоянии

схема стробирования 8 вырабатывает кратковременное управляющее напряжение, подаваемое одновременно через схему запрета 29 на параллельно соединенные входы вентилей 9, 10 и И.

Вентиль 9 при подаче управляющего напряжения снимает исходный сигнал со входа схемы вычитания 3, а вентиль 10 закорачивает этот вход, обеспечивая на нем нулевой сигнал. Одновременно вентиль 11, выход которого связан с вспомогательным входом интегратора 5, а второй вход - с выходом этого интегратора, закорачивает выход интегратора 5, обеспечивая равенство нулю напряжения аппроксимации. При снятии с вентилей

управляющего напряжения на вход схемы вычитания 3 через вентиль 9 подается исходный сигнал, вентили 10 и 11 разрывают соответствующие цепи короткого замыкания, и на выходе двоичного модулятора 4 в соответстВИИ с механизмом дельта-модуляции формируется последовательность импульсов «-1 или «+1. соответствующая скачку напряжения исходного сигнала и отражающая истинное значение последнего в момеит коррекции.

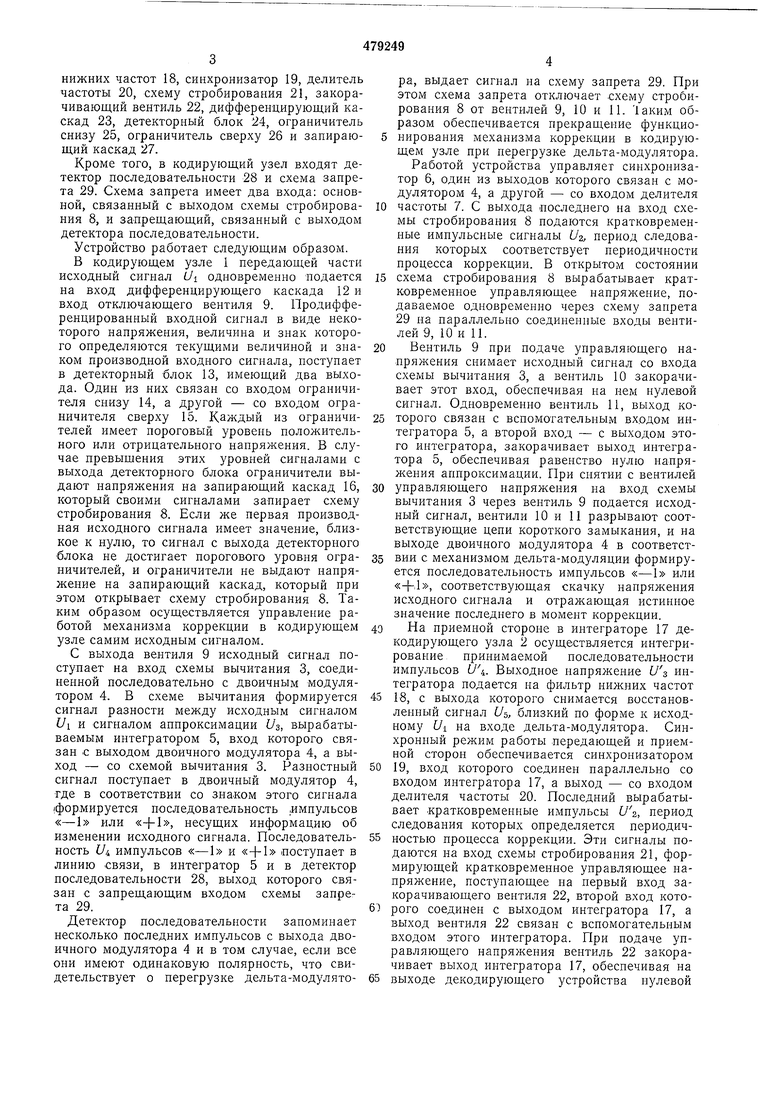

На приемной стороне в интеграторе 17 декодирующего узла 2 осуществляется интегрирование принимаемой последовательности импульсов Ui. Выходное напряжение (Уз ннтегратора подается на фильтр нижних частот

18, с выхода которого снимается восстановленный сигнал i/5, близкий по форме к исходному L/i на входе дельта-модулятора. Синхронный режим работы передающей и приемной сторон обеспечивается синхронизатором

19, вход которого соединен параллельно со входом интегратора 17, а выход - со входом делителя частоты 20. Последний вырабатывает кратковременные импульсы Uz, период следования которых определяется периодичностью процесса коррекции. Эти сигналы подаются на вход схемы стробирования 21, формирующей кратковременное управляющее напряжение, поступающее на первый вход закорачивающего вентиля 22, второй вход которого соединен с выходом интегратора 17, а выход вентиля 22 связан с вспомогательным входом этого интегратора. При подаче управляющего напряжения вентиль 22 закорачивает выход интегратора 17, обеспечивая на

выходе декодирующего устройства нулевой

сигнал к моменту приема последовательности однополярных импульсов, вырабатываемой в кодирующем узле после коррекции по описанному выше способу. Результатом интегрирования этой последовательности импульсов является сигнал, отражающий истинное значение исходного сигнала.

В декодирующем узле для формирования напряжения, обеспечивающего запирание или отпирание схемы стробирования 21, используется восстановленный сигнал с выхода фильтра нижних частот 18. Этот сигнал проходит последовательно через дифференцирующий каскад 23, детекторный блок 24, ограничитель снизу 25, ограничитель сверху 26 и запирающий каскад 27. Механизм образования напряжения, управляющего работой вентиля 22, аналогичен описанному выще для кодирующего узла при отсутствии перегрузки дельта-модзлятора.

Предмет изобретения

Устройство связи с дельта-модуляцией, содержащее кодирующий и декодирующий узлы, каждый из которых, в свою очередь, содержит схему коррекции, подсоединенную в кодирующем узле своим входом ко входу кодирующего узла, который через первый вход и выход отключающего вентиля одновременно подключен к первому входу первого закорачивающего вентиля, а через первый вход и

выход схемы вычитания, первый вход и выход двоичного модулятора - к выходу кодирующего узла, подключенного через первый вход и выход интегратора передачи одновременно ко второму входу схемы вычитания и

через первый вход и выход второго закорачивающего вентиля ко второму входу интегратора передачи, причем схема коррекции кодирующего узла подключена к первому входу схемы стробирования, ко второму входу которой через делитель частоты своим первым выходом подсоединен синхронизатор передачи, подключенный вторым выходом ко второму входу двоичного модулятора, отличающееся тем, что, с целью повыщения

качества передачи сообщений, выход двоичного модулятора через детектор последовательности подсоединен к первому входу схемы запрета, ко второму входу которой подключен выход схемы стробирования, а выход

схемы запрета одиовремеино подключеи ко вторым входам отключающего, первого и второго закорачивающих вентилей.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СООБЩЕНИЙ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1972 |

|

SU340083A1 |

| СИСТЕМА СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1971 |

|

SU296252A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| Устройство для передачи и приема сообщений | 1977 |

|

SU641488A1 |

| Система связи с дельта-модуляцией | 1976 |

|

SU649135A2 |

| Устройство для передачи сигналов с дельта-модуляцией | 1987 |

|

SU1420672A2 |

| Устройство для передачи сигналов с дельта-модуляцией | 1976 |

|

SU577695A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ СИГНАЛОВ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1991 |

|

RU2025045C1 |

| Устройство для передачи сигналов с периодической коррекцией | 1986 |

|

SU1367160A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

п

Lcb

Г- .г

о

i/j

фиг. 2

Авторы

Даты

1975-07-30—Публикация

1973-05-21—Подача