Изобретение относится к технике передачи сообщений и может быть использовано в системах связи, телеметрии и телевидения.

Известны устройства, в которых с целью повышения точности передачи сообщений и устранения накопления ошибок в условиях помех и временных нарушений связи осуществляется периодическая коррекция сигнала приемной части по сигналу передающей части. В устройстве (1) коррекция осуществляется за счет введения в передающей и приемной частях делителя частоты, схемы стробирования и управляемых ею вентилей. Но в этом устройстве при совпадении во времени процесса коррекции и быстрых изменений сигнала часть информации может быть потеряна. Для устранения этого недостатка были разработаны устройства.

Из существующих аналогов наиболее близким по своей технической сущности к заявляемому устройству является устройство для передачи сигналов с дельта-модуляцией (2). Устройство содержит вычитающий блок, выход которого соединен с входом двоичного модулятора, подключенного выходом через интегратор к первому входу вычитающего блока, и последовательно соединенные генератор тактовых импульсов, делитель частоты и блок стробирования, первый выход которого подключен к управляющим входам вентилей, при этом выход первого вентиля соединен с входом второго вентиля, а выход интегратора подключен к входу третьего вентиля, элемент НЕТ, триггер и последовательно соединенные умножитель частоты и элемент И, второй вход которого соединен с запрещающим входом элемента НЕТ и с выходом триггера, к первому входу которого подключен второй выход блока стробирования, причем второй и третий выходы генератора тактовых импульсов соединены соответственно с входом умножителя частоты и входом элемента НЕТ, выход которого подключен к выходу элемента И и к второму входу двоичного модулятора, блок задержки, двоичный кодер, переключающий блок и элемент ИЛИ, к входам которого подключены выход блока задержки, входом соединенного с первым выходом переключающего блока, и информационный выход двоичного кодера, счетный выход которого подключен к второму входу триггера выходом подключенного к управляющему входу переключающего блока, информационный вход и второй выход которого соединены соответственно с выходом двоичного модулятора и с входом двоичного кодера.

Однако в условиях работы по каналам передачи с переменными параметрами (с замираниями сигнала) это устройство не обеспечивает достаточной эффективности коррекции сигнала при возникающих случайным образом ухудшениях качества канала, что приводит к наличию ошибки в принимаемом сигнале в течение времени между моментами восстановления качества канала передачи и очередным циклом коррекции. Кроме того, поскольку коррекция в устройстве производится периодически независимо от изменений качества канала, в том числе и в те моменты времени, когда в сигнале не присутствует ошибка, в передаваемый сигнал будут внесены дополнительные шумы.

Цель изобретения - повышение помехоустойчивости системы.

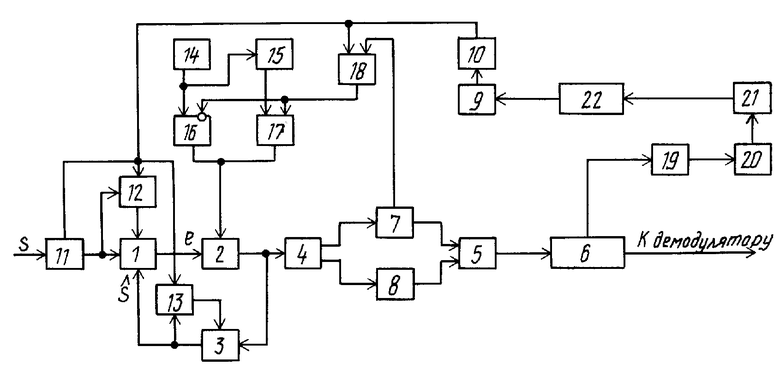

На чертеже представлена структурная схема предлагаемой системы, содержащей вычитатель 1, двоичный модулятор 2, интегратор И, переключатель 4, элемент ИЛИ 5, прямой канал 6 связи, двоичный кодер 7, элемент задержки 8, приемник 9 команд, блок 10 стробирования, первый, второй и третий ключи 11, 12, 13 соответственно, синхронизатор 14, умножитель 15 частоты, первый и второй элементы И 16, 17 соответственно, триггер 18, детектор 19 ВЧ-сигнала, пороговый блок 20, датчик 21 команд, обратный канал 22 связи.

Система работает следующим образом.

Исходный сигнал S подается на первый вход первого ключа 11, с выхода которого он поступает на второй вход вычитателя 1, соединенного с двоичным модулятором 2. В вычитателе 1 осуществляется формирование сигнала разности l между исходным сигналом S и сигналом аппроксимации  , вырабатываемым интегратором 3. Разностный сигнал поступает в двоичный модулятор 2, где в соответствии со знаком этого сигнала формируется последовательность Z символов "1" и "0", несущих информацию о приращениях исходного сигнала в тактовых точках. Эта последовательность проходит в канал 6 связи и поступает на вход интегратора 3.

, вырабатываемым интегратором 3. Разностный сигнал поступает в двоичный модулятор 2, где в соответствии со знаком этого сигнала формируется последовательность Z символов "1" и "0", несущих информацию о приращениях исходного сигнала в тактовых точках. Эта последовательность проходит в канал 6 связи и поступает на вход интегратора 3.

Работой системы управляет синхронизатор 14, импульсы основной частоты f которого определяют тактовые точки или моменты квантования, и блок 10 стробирования.

Тактовые импульсы с выхода синхронизатора 14 через открытый элемент 16 поступают на тактовый вход двоичного модулятора 2, а импульсы с частотой nf c выхода умножителя 15 частоты поступают на первый выход запертого второго элемента И 17 и дельта-поток Z поэтому формируется на основной частоте f. Через переключатель 4 дельта-поток поступает на элемент 8 задержки, а с его выхода через элемент ИЛИ 5 в канал 6 связи.

Находящийся на приемной стороне детектор 19 ВЧ-сигнала измеряет уровень принимаемого сигнала в высокочастотной части канала передачи. Уменьшения уровня сигнала ниже порогового U пор (устанавливаемого пороговым блоком 20), происходящие, например, в результате замирания, фиксируются, и после превышения уровнем принимаемого сигнала значения Uпор датчик 21 команд выдает команду на коррекцию сигнала, передаваемую через обратный канал 22 на приемник 9 команд, находящийся на передающей стороне. При этом в блоке 10 стробирования, соединенном с выходом приемника 9 команд, формируется кратковременное управляющее напряжение, подаваемое одновременно на первый вход триггера 18 и на управляющие входы ключей 11, 12 и 13. Первый ключ 11 при подаче управляющего напряжения снимает исходный сигнал S с второго входа вычитающего блока 1, а второй ключ 12 закорачивает этот вход, обеспечивая тем самым нулевой сигнал на входе вычитающего блока 1. Одновременно третий ключ 13 закорачивает выход интегратора 3, обеспечивая равенство нулю аппроксимирующего напряжения. Триггер 18 формирует напряжение, которое поступает на второй (инвертированный) вход первого элемента И 16 и второй (прямой) вход второго элемента И 17. При этом первый элемент 16 И отключает выход синхронизатора 14 от двоичного модулятора 2, прекращая тем самым формирование дельта-потока Z на основной частоте f, а второй элемент И 17 обеспечивает прохождение на двоичный модулятор 2 синхросигналов с выхода умножителя 15 частоты.

При снятии сигнала блока 10 стробирования на вход вычитающего блока 1 через вентиль 11 подается исходный сигнал S1, ключи 12 и 13 разрывают соответственно цепи короткого замыкания и на выходе двоичного модулятора 2 в соответствии с механизмом дельта-модуляции будет формироваться последовательность импульсов "1" (если значение сигнала S в данный момент больше нуля) или "0" (при S<0), следующих с частотой, в n раз превышающей основную частоту синхронизации f. Эта последовательность поступает на информационный вход переключателя 4. При поступлении на ее управляющий вход напряжения с выхода триггера 18 импульсы с выхода двоичного модулятора 2 поступают на вход двоичного кодера 7, где количество импульсов подсчитывается, кодируется двоичным К-разрядным числом и затем это число посылается в канал 6 связи через элемент ИЛИ 5 с частотой fкор=log2nf (при этом максимально возможное число шагов коррекции n). По истечении n-шагов коррекции на счетном выходе двоичного кодера 7 появляется импульс, переводящий триггер 18 в первоначальное состояние. Это ведет к прекращению подачи в двоичный модулятор 2 синхросигналов с увеличенной частотой через второй элемент И 17 и к возврату всей системы в основной режим, в котором в двоичный модулятор 2 через первый элемент И 16 поступают тактовые импульсы с основной частотой f от синхронизатора 5, а дельта-поток Z с выхода двоичного модулятора 2 через переключатель 4 поступает на вход элемента 8 задержки. С выхода элемента 8 задержки дельта-поток через время t=k/f через элемент 5 ИЛИ подается в канал 6 связи. За время t, пока дельта-поток не появился на выходе элемента 8 задержки, происходит вывод в канал 6 связи К-разрядного двоичного числа из двоичного кодера 7 с частотой fкор=Кf=log2nf. На приемной стороне датчик 20 команд через время после передачи команды о начале коррекции на приемник 9 команд подготавливает приемную часть дельта-кодека к декодированию К-разрядного корректирующего числа, после чего вновь происходит демодуляция дельта-потока Z на частоте f.

При использовании устройства с периодической коррекцией сигнала (прототип) время, в течение которого в принятом сигнале присутствует ошибка, внесенная в результате временного нарушения связи (пакета ошибок), складывается из длительности нарушения связи времени между моментом восстановления связи и момента коррекции. При этом величина второй составляющей изменяется случайным образом от нуля до значения периода коррекции. Значительно уменьшать период коррекции нецелесообразно, так как при увеличении частоты коррекции возрастает и мощность шума, вносимого ею в сигнал. Применение предложенной системы позволяет сократить время, в течение которого в принятом сигнале присутствует ошибка за счет устранения второй из названных составляющих этого времени. Кроме того, существенно уменьшается частость коррекции, которая производится теперь только в моменты восстановления связи после замираний сигнала, следовательно, снижаются и шумы, вносимые в сигнал процессом коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи сигналов с дельта-модуляцией | 1987 |

|

SU1420672A2 |

| Устройство для передачи сигналов с периодической коррекцией | 1986 |

|

SU1367160A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Устройство для передачи сигналов с дельта-модуляцией | 1976 |

|

SU577695A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Устройство связи с дельта-модуляцией | 1973 |

|

SU479249A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| ЦИФРОВОЙ АВТОМАТИЧЕСКИЙ КОРРЕКТОР СИГНАЛОВ | 1992 |

|

RU2106062C1 |

| Дискретный адаптивный дельта-модулятор | 1976 |

|

SU641647A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ ПО ВОКОДЕРНОМУ ТРАКТУ | 1991 |

|

RU2010439C1 |

Изобретение относится к технике передачи сообщений, телеметрии, телевидения. Изобретение позволяет повысить помехоустойчивость системы. Для достижения этой цели в устройство, содержащее вычитатель 1, двоичный модулятор 2, интегратор 3, переключатель 4, элемент ИЛИ 5, двоичный кодер 7, элемент задержки 8, блок 9 стробирования, первый 11, второй 12 и третий 13 ключи, синхронизатор 14, умножитель 15 частоты, первый элемент И 17, триггер 18, введены: на передающей стороне - приемник 9 команд, второй элемент И 16, а на приемной стороне - детектор 19, пороговый блок 20 и датчик команд 21, соединенный с приемником команд через обратный канал 22 связи. 1 ил.

СИСТЕМА ДЛЯ ПЕРЕДАЧИ СИГНАЛОВ С ДЕЛЬТА-МОДУЛЯЦИЕЙ, содержащая на передающей стороне синхронизатор, выход которого через умножитель частоты соединен с первым входом первого элемента И, выход которого соединен с первым входом двоичного модулятора, первый ключ, информационный вход которого является входом системы, выход первого ключа соединен с первым входом вычитателя и информационным входом второго ключа, выход которого соединен с вторым входом вычитателя, выход которого соединен с вторым входом двоичного модулятора, выход которого соединен с входом переключателя и первым входом интегратора, выход интегратора соединен с третьим входом вычитателя и информационным входом третьего ключа, выход которого соединен с вторым входом интегратора, первый выход переключателя соединен с входом двоичного кодера, первый выход которого соединен с первым входом триггера, выход которого соединен с вторым входом первого элемента И, блок стробирования, выход которого соединен с вторым входом триггера и управляющими входами первого - третьего ключей, второй выход переключателя через элемент задержки соединен с первым входом элемента ИЛИ, второй выход двоичного кода соединен с вторым входом элемента ИЛИ, выход которого подключен к прямому каналу связи, отличающаяся тем, что, с целью повышения помехоустойчивости системы, в нее введены обратный канал связи, на передающей стороне - приемник команд и второй элемент И, первый и второй входы и выход которого подключены соответственно к выходу синхронизатора и выходу триггера и к входу двоичного модулятора, вход и выход приемника команд подключены соответственно к обратному каналу связи и входу блока стробирования, на приемной стороне введены детектор, порговый блок и датчик команд, вход детектора подключен к прямому каналу связи, выход детектора через пороговый блок соединен с входом датчика команд, выход которого подключен к обратному каналу связи.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для передачи сигналов с дельта-модуляцией | 1987 |

|

SU1420672A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-12-15—Публикация

1991-07-04—Подача