Изобретение отнооитея к облаети вычислителмюй техники.

Извести, норогов е ло -ичеекие элеме1 Т л, обладающие больн1ИМ11 лог11 ес1 1ими воз.можиостями по еравие11)о с клаес11ческ. схемалги «И, «ИЛИ, «ИЕ. Булевы фу1 кц11и, не роализуем ле а пороговом элементе, реализуются сетями из нороговь х элементов, кш1фи1-ура и1я оторых выбирается зара1 ее. Так, например, порогово-кон7 опктивная (или порО ово-дизъ онкт11 М ая) О11фи -урац)я нредставляет собой двух аекад1 ую сеть, входной к.аскад сети состоит из об лчиых норого(ых элементов, а выход 1оГ является схемой «И лн «или.

Целью изобретения является повыше П е

ЛОГИЧеС НХ ВОЗМОЖ1 ОСТе 1 и б з СТрОДеЙС,

элемента а компо 1ентах, реализуемых в ннтвграл 1ом иснолнеиии, .выполня ощего фу Клию, реализуему 0 .ю из порогоB JX элементов. Это достн1 -ается тем, что , иа «весов э х резисторах и управляемый входными диодами, через смеш, диод с объедниенными катодами присоединен к «суммиру ошему резистору и одному из Э.МНТТерОВ МПО ОЭМИТтерного транзистора, коллекто 5 которо о под«Л 0че 1 к дискри И атору ia двух каскадно объеди ен 1ых транзисторах с заземлеипы.мп эмиттерами, а к эмиттерам шюгоэмиттер 101-о тра1 зистора рисоеди1 е 1 т дололииТеЛЫ1Ь е сумматор, с СОбсТВе 1)МИ

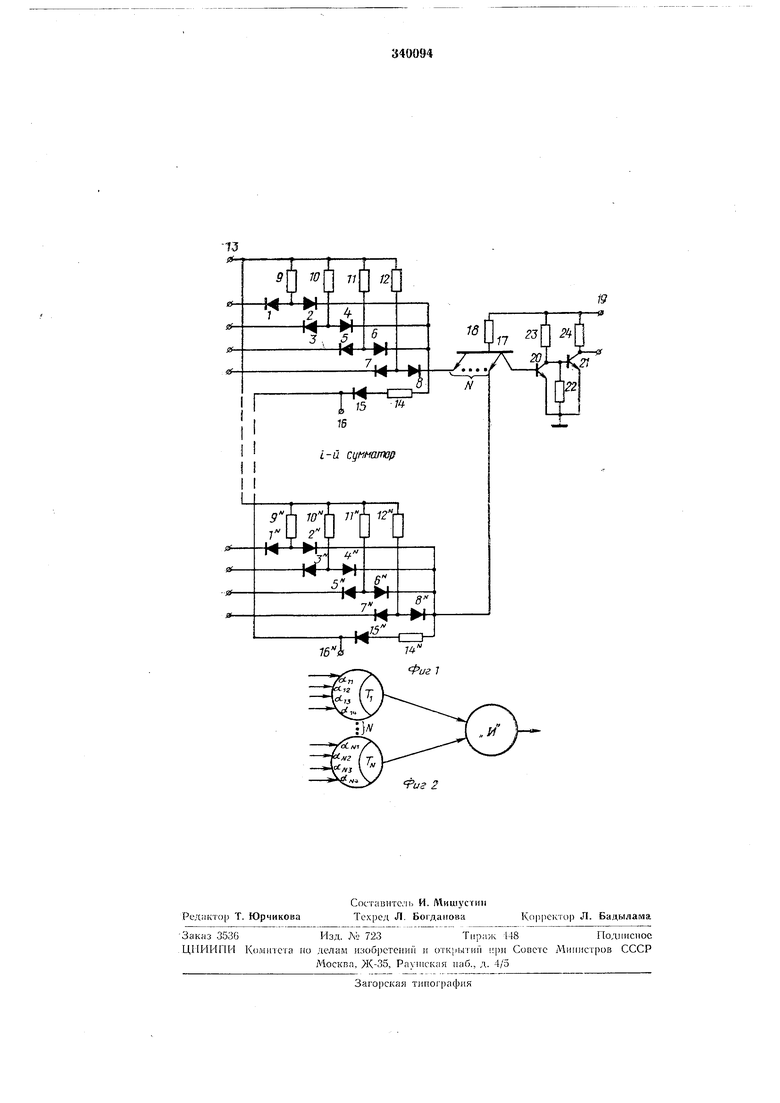

«весов ми Н ,нми рсзисторамн. Иа . 1 изобра ке 1а лрнипиниальная схема предлагаемо 0 иорогово о логическо О эле ента; ia i|)H 2 -Э ;в валент1 ая норогоиоК011,0 1ктив ая ссть на ,х элсмснтах без 11сиол)3ова111 я мно1-оэл птерного транзистора.

)Й лоппмеский обт-еднняеч по схеме «И Л су,маторов с «несоВ МИ. «СуММНру 01Ц л ; реЗ СТОра М 1, 1 еЛНчины -оторых 0 ределя отсп эквивале1 Т ой иорогово-ко 1Ъ1он т 1БИОй .

ЛннеЙ ьн еум.атор (ia ф 1 показаны лм11е |1,е на чет,ре входа) еодержнт нонар1 о ре. д гоД1) / Н 2, 3 и 4, 5 п 6, 7 и 8. Каждая пара диодов в точках Х соедине ия подкл очена через

«весов)1е резистор, 9-/2 к положител)1ому 1сточ нка 13 питания. Катоды диодов /, 3, 5 и 7 соедииень со .входами, а катоды диодов 2, 4, 6 и 8 совмеетно подкл очены к «суммиру О дсл у резнстору 14, соедн еи ому

с термокомпенсиру10 цим диодом /5 в цепи отрицательного 16 1еточ И1ка . Общая точка «атодов диодов 2, 4, 6 и 8 является в,ходом раесматривае 0 0 сумматора, лрисоеда 1еи ого к эмитэтого rpauj-ncropd через резистор 18 подключена к положительПому зажиму 9 источника питания, а ко.члектор - к базе транзистора 20, которьи сов:мсстио с тра:11зисторо,м 2/ и резисторами 22, 23 и 24 составляет усилительную схему - дискриминатор.

В .нижней части фиг. 1 изображена с.хема Л-:Ного лниейиото су.мматора, идентичная, как и с.хема /-НОГО линейного сумматора, с.чсме BI Iшеописаииого лашей пого сумматора, .выход которой присоединен к Л-ио.му элгиттеру тра нзнстора 17.

Па фнГ. 2 приияты следуюпи1е обозиачсиия: aij -относительный «вес /-го входа /-го элемента (i 1, 2,..., Л ,), / 1,2, ..., к, ); к - число 1 ХОДОБ /-ГО элемента; TI -отиосггельиая величина иорога /-го элемента.

Лагическнн элемент работает следующим образом.

В нс.ходном состоянни элемента диоды /, 3, 5 А 7 1-1 аналогичные диоды остальных линейных су.мматоров проводят ток от общего источзгнка 13 пнтания. На г.ыходе имеет место уровеиь логического нуля. Входиьш сигналы li фор..ме полож;11телыны.х нерепадов и.апряжения занирают -в любых ко.мбмнаииях диоды /, 3, 5 и 7, переключая точки через «BecoBi ie резисторы в «суммирующей н изменяя потенциал ла первом эмиттере транзистора 17. Когда на всех ;V эмиттерах этого транзистора, обьедн 1яю1цего линейные сумматоры, потенциал оказывается :выше срабатывания диокр.им.ииатора на транзистОрах 20 и 21, что эквииалеитио включанию всех пороговых эле-меито15,

вы.ходе устана.вливается уровень логической единицы.

Эквивалентная порогово-конъюнктивная сеть реализуется па пороговых эле.меитах того же типа без нснользования лпюгоэмнттериого транзнстора, обт,единенных на гл ьходе, что сн;ижает допустимую емкостную нагрузку выхода . Предлагаемая схема по cpaiiHeHiiiio с эквивале1ггной сетью содержнт меньшее количество компонентов, может бьггь выполнена в иитегральиом нсполнеили, имеет более высокую нагрузочную способиость и способна работать на более длинные линии связи.

П р е д м е т изо б р е т е н и я

15

Пороговый ло1ичеекий эле.мент, содержащий липейпый сумматор, вьтполиеииый на резисторах, подключенных к сигнальным гнинам

через входные диоды и через смеп а1ощие диоды с обт единеинь м,и катодами, присоединеп 1ыми к днскримннатору, выполненному па двух каскадно соеди 1енных транзнсторах с заземленными эмиттерами, кол;1ектор первого из

которых гюдк.тючен к базе второго транзистора, ко.тлектор которого является выходол1 элемента, отличающийся тем, что, с нелыо повыП1еиия логических возможностей и быстродействия элемента, к базе первого транзистора

дискриминатора присоедииеи коллектор многоэмнттерного транзистора, к эмиттерам которого нодключены дополннтельные линейные сумматоры с собствеииыми «весовым.и и «суммиру1ОИ1,ими резисторами.

-73

J8

РП m N

тiA15

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕИТ | 1971 |

|

SU318163A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU319077A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU370728A1 |

| СЧЕТЧИК ЭНЕРГИИ ПОСТОЯННОГО ТОКАВСЕСОЮЗНАЯПАТЕНТНО-][ХНГ:^"КАЯБИБЛИОТЕКА | 1970 |

|

SU283394A1 |

| ВСЕСОЮЗН.^Я I | 1973 |

|

SU372686A1 |

| Пороговый логический элемент | 1973 |

|

SU473293A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Селектор импульсов по длительности | 1972 |

|

SU459849A1 |

| Многоканальный стабилизированный источник питания | 1988 |

|

SU1529199A1 |

7б47«

7

fus 2

Авторы

Даты

1972-01-01—Публикация