Изобретение относится к вычи-слительной технике .и автоматике.

Известен нороловый элемент, ионользую1Ц.ИЙ независимые И1сточ, толков на входе, ун1ра1вляемые ВХ101ДНЫ:М1И диОда:м1И, а в качестве днскр.Имин.атора - комбинацию туннельный дио1д-тра1Н13 Истю р.

Использовать туннельные диоды в MOIHOЛИТ1ных ;И1И1тег,р альных затруднительНО, поскольку при их изр01ТовЛен1И1И (необходимо оаущест1влять Т1ра1влвН1ие участка кр И Сталл1а, в котором размещен туннельный диод, чтобы получить величину тока /макс- Трудности воз)И;Икают из-за хрупкости готового туниельного диода. Кроме того, кремний, являющийся материалом иодложвди для больЩ1инсрва и,нтбпраль:ных cxeiM, не позволяет получить характеристики, столь же хо|рощие, KaiK ге|рмаиий и арсенид галлия. Следовательно, Пбрспективы примсне-ния туииельных диодов в интегральных схемах, по крайней мере :на ближ айщее будундее, огра;пичены гибридными схе1мам и.

Цель изобретения заключается в том, чтобы мажанмалыно упростить потенциальный пороговый лопический элемент, повысить степень ннтеграции и устойчивость к климахичеCiKHiM во;здеЙ€Т(ВияА1. С этой целью .1итеЙ1Ный сум.мато.р, выпол нонный на резистар ах и управляемый входными диодами, через смещающие диоды с объе|Д|и ненны.мл катодалт соединен с Д|Искрими;иаФара.м на двухзмиттериом Т1ра1нзист10 ре, из эмиттеров которого ИО|Дключея к выходу лИ1ней:ного сумматора и к 5 резИ|Стс|ру смещения, а второй зазс.млен, база этого транзисто1ра через рез1исто1р смещения подключена к зе.мляиой щине.

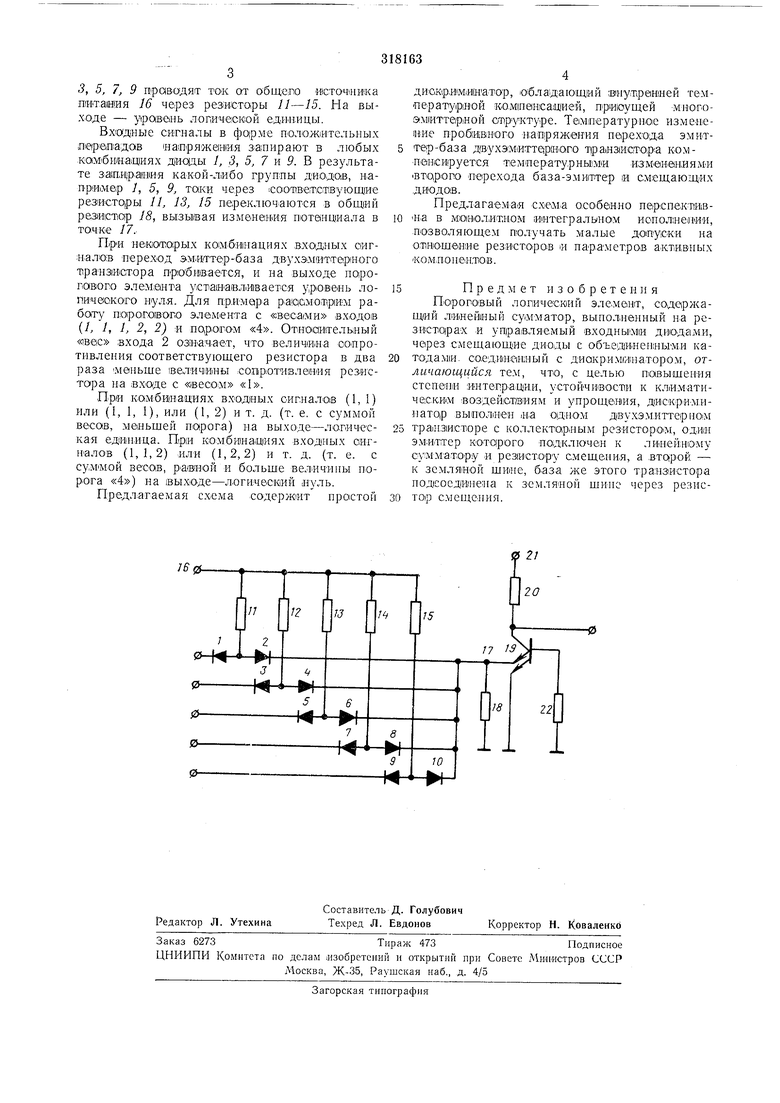

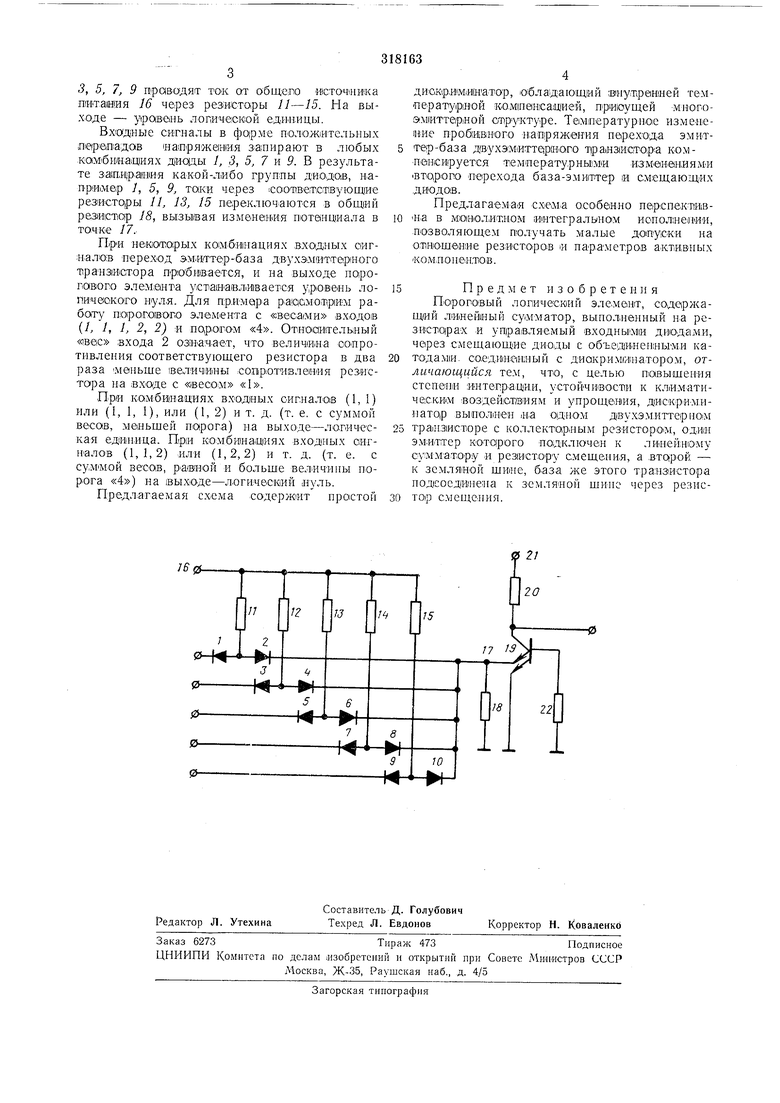

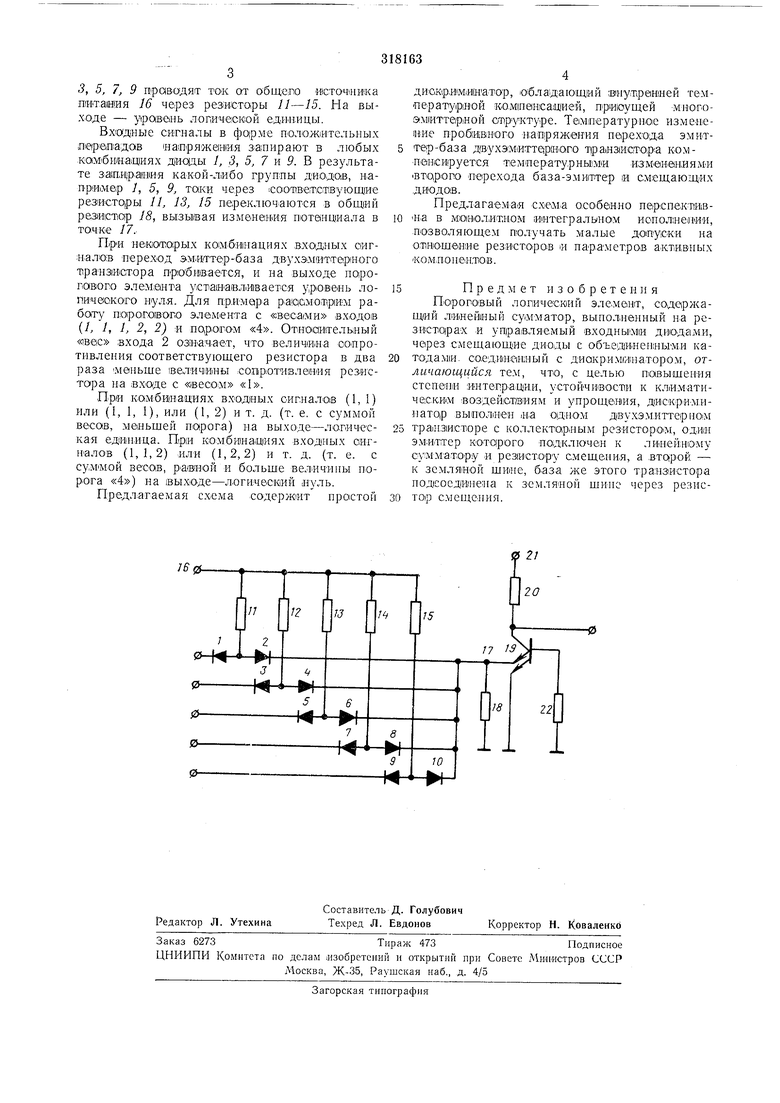

На чертеже представ л аи а приищилиальная схемка порогового логического элемента на 10 пять входов.

Пороговая логическая схема ссстаит из

линейного сум:м.атора и дискриминатора. ЛиН ейный сумматор coдepжiнт понарно соединен1ные крем:ние;вые диоды / .и 2, 3 н 4, 5 н 6.

15 7 Е 8, 9 и 10.

Каждая пара диодав в точках, объединяющих , соедн1няется через «весовые резисторы II-15 с положительньгм исгочниког.м шитаиня 16. Ка-тады диодов 2, 4, 6, 8, 10 объединены в точке /7 и через резисто р 8 подключены к земляной щи1не.

Точка /7 (выход линейного сумматора) присоодинена к эмиттеру Д1вухэ1м1итте|р1ного трас- зистора 19. Второй эмнттер заземлен. Коллек5 лар транзнстора 19 (|ВЫХ1Од;парО|Гового элемента) , через резистор 20 падсоеди(няется к поЛОл ительному ,и1с1точии1ку пита;ния 21. База этого траизистор.а через резистор 22 npaicoeди1нена ;к зе мляйой . В исходном состоянии устройства диоды /,

3, 5, 7, 9 п раводят ток QT общего источника питания 16 через резмсторы //-15. На выходе - yipaseinb лоличе С1 юй ед1М1ицы.

ВхОдные сигналы в форме пол о/юительных шар ашадав «атряжания запирают в Л10|бых ком бниащиях диады 1, 3, 5, 7 и 9. В результате эатцраиия какой-либо группы диодо.в, н.апрИ|Мвр 1, 5, 9, таки через 1С010Т1Ве;т,ст1ву1ОЩ1ие резисторы 11, 13, 15 П1ереключ аются в общий резистор 18, вызывая изманеиия потенциала в тачке 17.

ПрИ пеюаторых К01мб:пнациях входных сиг:нало:в переход змИТтер-база двухамиттериого транзистора проби1В:ается, и на выходе порогового эле:Л1;ешта устававлмваетсл ур10вень лопичаокого нуля. Для примера р.,ймо1тр1им работу порогового элемента с «BCcaiMH входов (1, 1, 1, 2, 2) и порогом «4. Отиоаи1тельный входа 2 , ч-то велич1И1на сопротивления соответствующего резистора в два раза мапьше величины сопротивления резистора на входе с «)весо:м «1.

При кам:бшпациях входных сигналов (1, 1) или (I, 1, 1), или (1,2) и т. д. (т. е. с суммой весов, меньшей порога) па выходе-логическая единица. При комбина щиях входных сигналов (1,1,2) или (1,2,2) и т. д. (т. е. с суммой весов, р-авиой и больше вел ичины порога «4) на выходе-логичасмий иуль.

Предл агаемая с.хема содержит простой

дис,кри ми1натор, о бладающий ;инутран ней температурной ко,м|пан1са 1.иией, присущей мног-оэмитте/риой структуре. Тампературное измеие1НИ.е пробиВНОго наяряж еиня перехода эмиттар-база двухэмитте)р1паго TpaiH3iHCiTopa компепснруется темпер атур ными и;змвн.апия ми Второго перехода база-эмнттер и смещающих диодов.

Предлагаемая схема особеино пер спективВа в мо1нолихном иитегральном исполнении,

П10зволяющем получать малые допуски на

о.тношание резисторов iH пар.аметров актив ных

Компонентов.

Предмет изобретения

Пороговый логический элемангт, содержащий линейный сумматор, выпол1ненный на резистарах и управляемый входны-ми диодами, через смещающие диоды с объединенными катодами соеди1не1н;ный с дискриминатором, отличающийся тем, что, с целью по1выщепия стенепи интеграции, устойчивости к климатическим воздеЙ С,тв1Иям и упрощения, дискрилгипатор выиол1Н1ен .н-а одном двухэм.иттериОМ

тра1н,зи сторе с коллекторным резисторо м, оди1н эмиттер котсфого подключен к линейному оу.мматору и рез1истору смещения, а второй - к земляной щите, б-аза же этого транзистора нодсоединена к земляной шино через резистор с.меп;ения.

60и 2

/J

75

Авторы

Даты

1971-01-01—Публикация