1

Изобретение относится к вычислительной технике и автоматике. Устройство иредназначено для преобразования периодической последовательности входных импульсов со скважностью, равной двум, в четыре одинаковые последовательиости импульсов, частота следования которых в два раза ниже частоты следова п-1я входных импульсов, а временной сдвНГ между импульсами в соседних выходных каналах равен длительности входных импульсов.

Известен распределитель импульсов с парафазным входом и четырьмя выходами.

Цель изобретения - упрощение конструкции и уменьшение потребляемой мош,ности устройства. Достигается она тем, что предлагаемый распределитель выполнен на однонороговом и двухпороговом пороговых элементах с общим для них диодио-резистивным сумматором, парафазные выходы которых являются выходами распределителя, причем нрямой выход двухпорогового иорогового элемента соединен через диоды с двумя входами сум.матора, один из которых нодключен к щине инверсного , а прямой выход однопорогового порогового элемента соединен через диод со входом сумматора, подключенным к щине прямого сигнала.

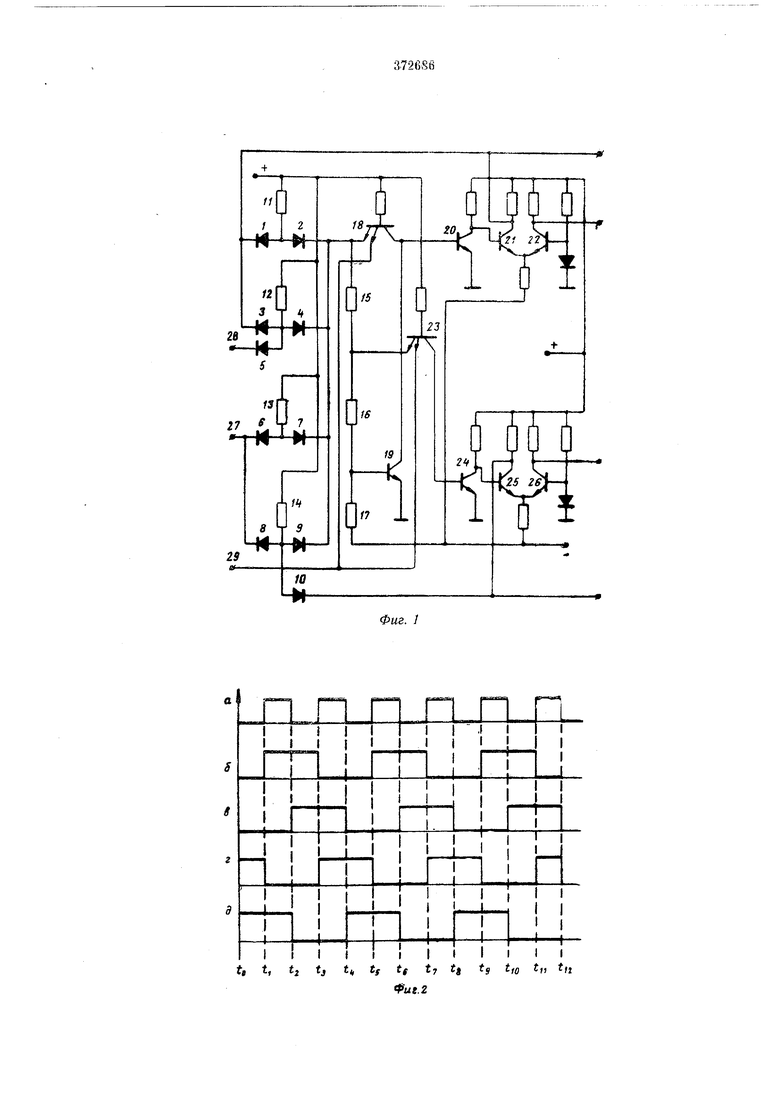

На фиг. 1 представлена приипиниальная схема распределителя импульсов; на фиг. 2 - временная диаграмма его работЕз.

2

Распределитель выполнен на однопороговом ii двухиорогсвом иороговых элементах с общим для них диодно-резистивным сумматором.

Сумматор содержит диоды /-10, весовые резисторы 11 -14 и суммируЕОН ие резисторы 15-/7. Сопротивления резисторов // -14 обратно ироиорниональны их весам. Веса резисто;)(.;в // и 13 равны едииЕще, розисгора 12 -

двум, ije3HCTOpa 14-трем.

/1вухиороговый иороговый э;1емепт собран на транзисторах 18-22, однопороговый - на транзисторах 23-26. Однонороговый нороговый элемент срабатывает, когда через суммируЕощие резисторы течет ток, равный тpe весовы.м или больще их. При этом един.ичньЕЙ снимается с коллектора транзистора 25 (прямой выход). Соответственно Eia коллекторе транзистора 26 (инверсный выход) ирнсутствует Е улевой сигнал.

Двухпороговый пороговый элемент срабатывает, когда через еуммируЕОЩие резисторы течет ток от одного до трех весовых. При этом , сигнал снимается с коллектора

транзистора 21 (нрямой выход), Е1улевой - с коллектора транзистора 22 (НИверсн :.ЕЙ BE Iход). С помощью транзистора 19 двухлороговый иоротовый элемент возвращается в исходное состояние, когда через суммирующие

резисторы течет ток, больщий четырех весовых. На вход 27 распределителя подается входной сигнал (фиг. 2,а), на вход 28 - и«версня входного сигнала. Вход 29 служит для возвращения схемы в исходное состояние. Для установки распределителя в исходное состояние (нулевые сигналы на нрямых выходах пороговых элементов и единичные на инверсных) необходимо нодать }1из-кие потенциалы на входы 27 и 29 (на входе 28, соответственно, присутствует единичный сигнал). При этом суммарный весовой ток через резисторы 15-17 равен нулю. Раснределитель подготавливают к работе подачей на вход 29 высокого потенциала. В момент ti на вход 27 поступает высокий потенциал. При этом в суммирующие резисторы через резистор 13 течет ток, величина которого равна одному весу, двухпороговый элемент срабатывает, на его прямом вы.чоде появляется единичный сигнал (фиг. 2,6), переключающий ток диода 1 в резисторы 15- 17, суммарный весовой ток через резисторы 15-17 становится равен двум весовым. Такое состояние сохраняется до тех пор, пока прямой входной сигнал равен единице. В момент /2 прямой входной сигнал становится равным нулю. При этом ток в резисторы 15-17 поступает через резисторы 11 к 12, т. е. равен трем весовым, двухпороговый элемент не меняет состояния, а однопороговый срабатывает, что приводит к появлению единичного сигнала на его прямом выходе (фиг. 2,б), но поскольку сигнал на входе 27 равен нулю, ток через резисторы не изменяется. В момент t сигнал на входе 27 снова становится единичным. При этом в резисторы 15-17 через резисторы //, 13 « 14 поступает ток, равный пяти весовым. Однопороговый элемент не меняет своего состояния, двухлороговый переходит в нротивоноложное состояние, при котором па прямом выходе сигнал равен пулю. Это приводит к переключепию тока через резистор 11 в диод /, и, следовательно, уменьшает ток через резисторы 15-17 на единицу весового тока, что не нрнводит к дальнейшему изменению состояния схемы. Таким образом, после момента /з единичные сигналы присутствуют на прямом выходе однопорогового элемента и инверсном выходе двухпорогового. В момент t сигнал на входе 27 равен нулю, и на прямых выходах пороговых элементов появляются нулевые сигналы. Такое состоя-ние сохраняется до момента t, после чего цикл работы распределителя импульсов повторяется. Предмет изобретения Распределитель импульсов с парафазным входом и четырьмя выходами, отличающийся тем, что, с целью его упрощения и уменьшения потребляемой мощности, он выполнен на однопороговом и двухпороговом пороговых элементах с общим для них диодно-резистивным сумматором, парафазные выходы которых являются выходами распределителя, причем прямой выход двухпорогового порогового элемента соединен через диоды с двумя входами сумматора, один из которых подключен к шине инверсного сигнала, а прямой выход одпопорогового порогового элемента соединен через диод со входом сумматора, подключенньш к шине прямого сигнала.

Авторы

Даты

1973-01-01—Публикация