Изобретение относится к области автоматики, вычислительной техники и кибернетики.

Известны элементы с настраиваемой структурой (элементы вычислительной среды и элементы однородных структур), содержащие логический элемент, блок памяти и адресный блок, в которых логический элемент может настраиваться на выполнение одной или нескольких функций из заданного набора логических функций.

Недостатком всех известных элементов является то, что устройство с настраиваемой структурой неспособно воспроизводить требуемое количество одинаковых автоматов в самом устройстве но описанию одного автомата. Это обусловлено тем, что настройка (перестройка) известных устройств с настраиваемой структурой может быть осуществлена только с помощью внешних управляющих устройств, функции которых могут выполнять, в частности ЦВМ или запоминающие устройства. При этом для настройки устройства с настраиваемой структурой необходимо в блоки памяти управляющих устройств записать всю информацию о настройке устройства. Это требует больщого количества запоминающих элементов, так как емкость блоков памяти внешнего запоминающего устройства должна быть не меньше суммарной емкости блоков памяти всех элементов с настраиваемой

структурой. Таким образом, для управления устройством с настраиваемой структурой требуется управляющее устройство, которое по сложности не меньше первого.

Целью изобретения является создание такого элемента с настраиваемой структурой, который позволяет в устройстве с настраиваемой структурой, выполненном на его основе, нутем элементарных действий воспроизвести требуемое количество однотипных автоматов по описанию одного автомата (по информации настройки одного автомата).

Предлагаемый элемент обладает способностью выдавать на свои выходы как информацию, поступающую на его входы с выходов смежных элементов, так и свое собственное описание, т. е. выдавать на свои входы информацию с выходов собственных запоминающих

элементов. Чтобы описание элемента было полным, необходимо и достаточно, чтобы, вопервых, элемент выдавал на свои выходы всю информацию со своих ячеек памяти, и, вовторых, эта информация должна однозначно

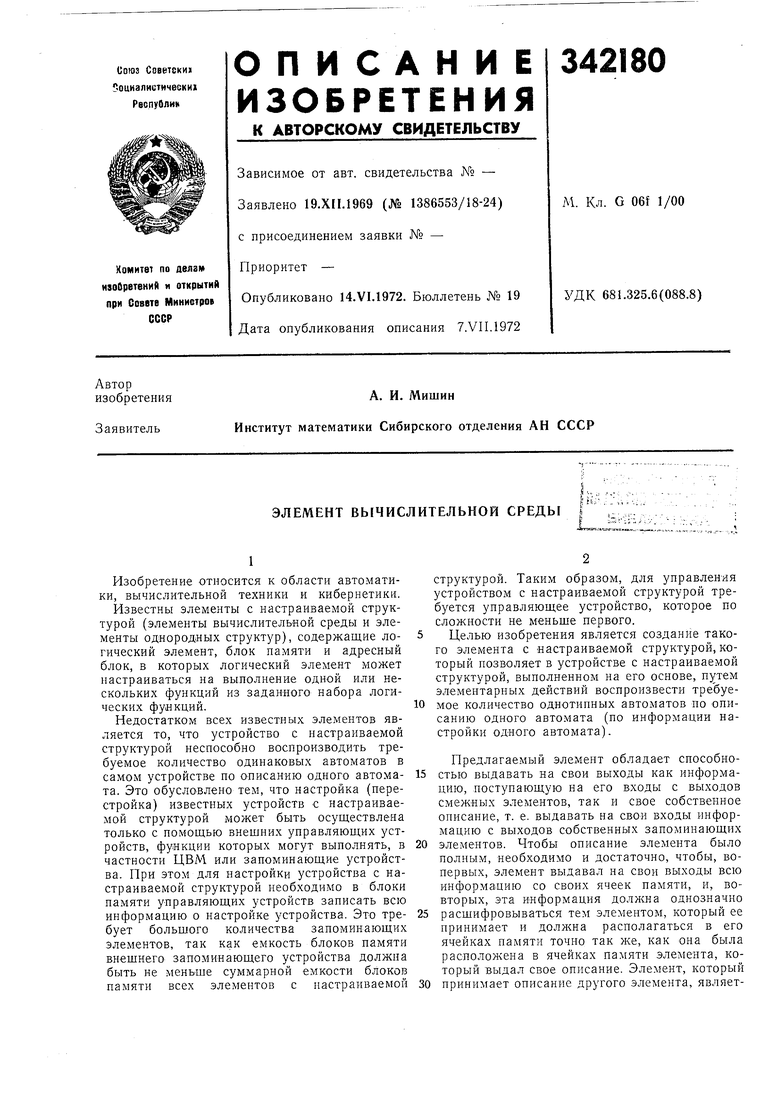

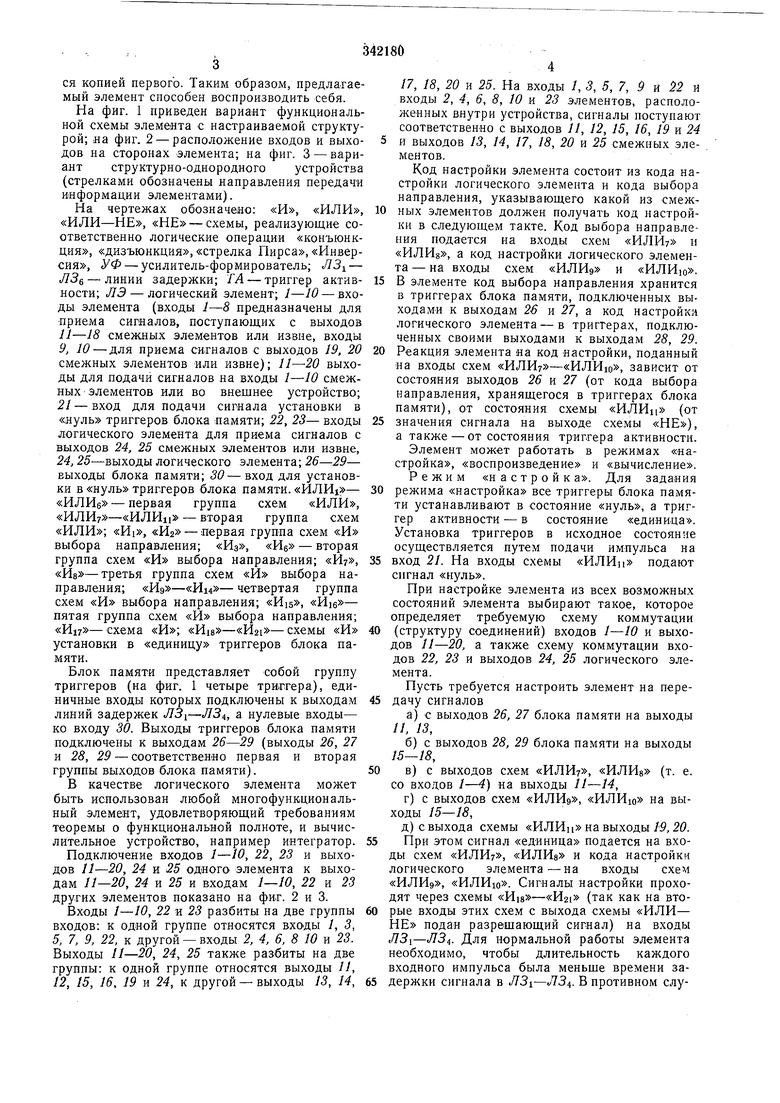

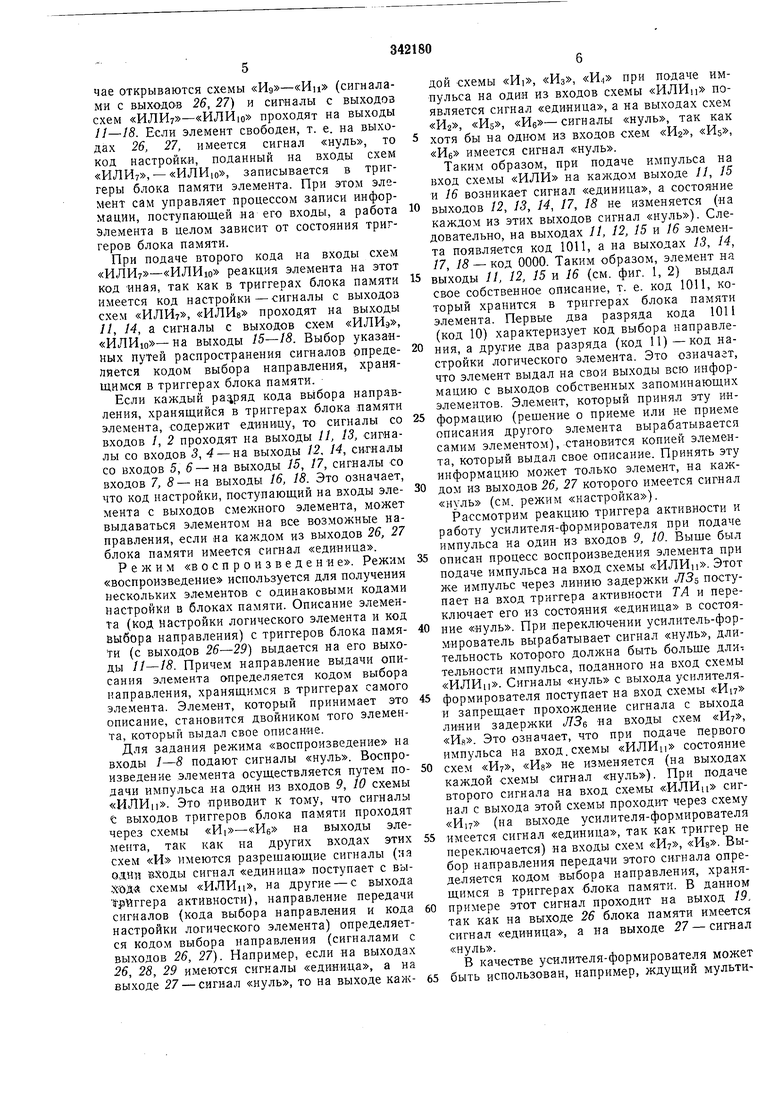

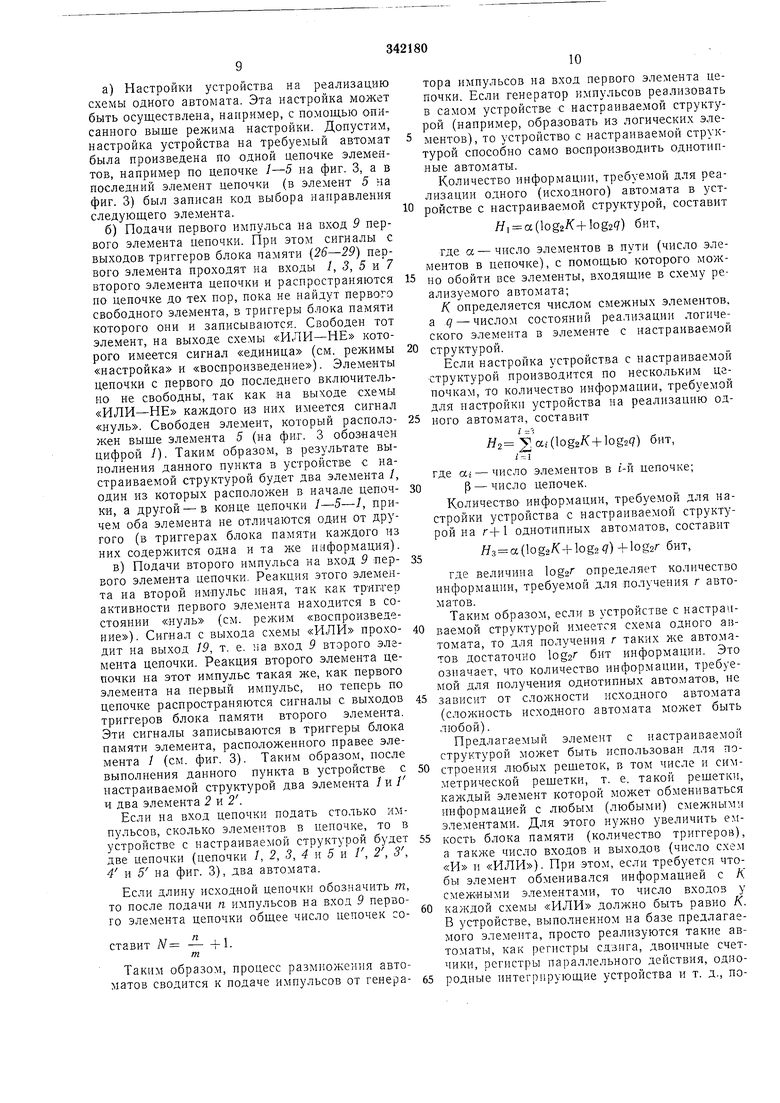

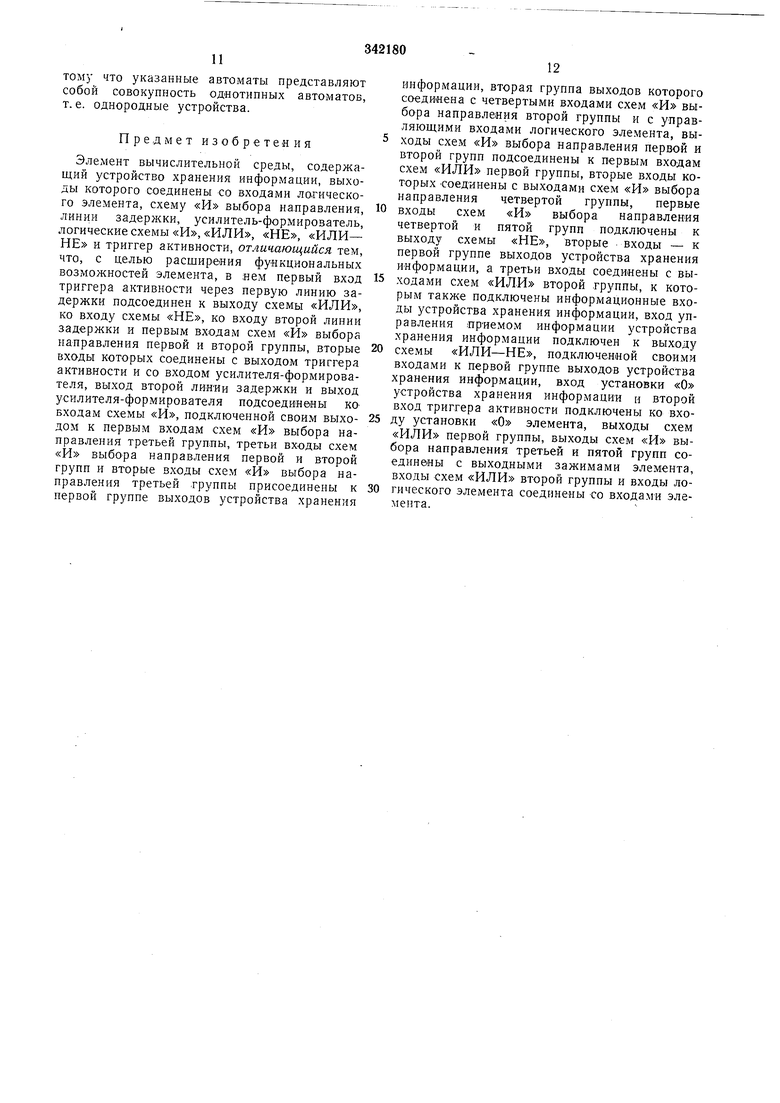

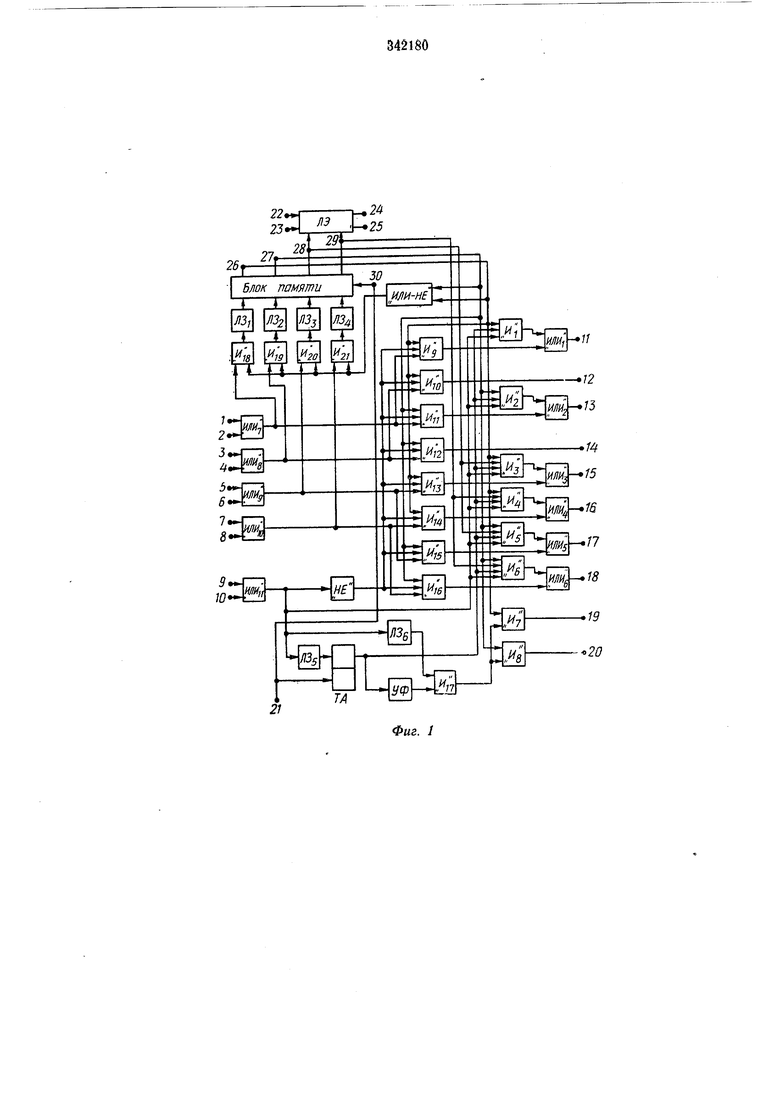

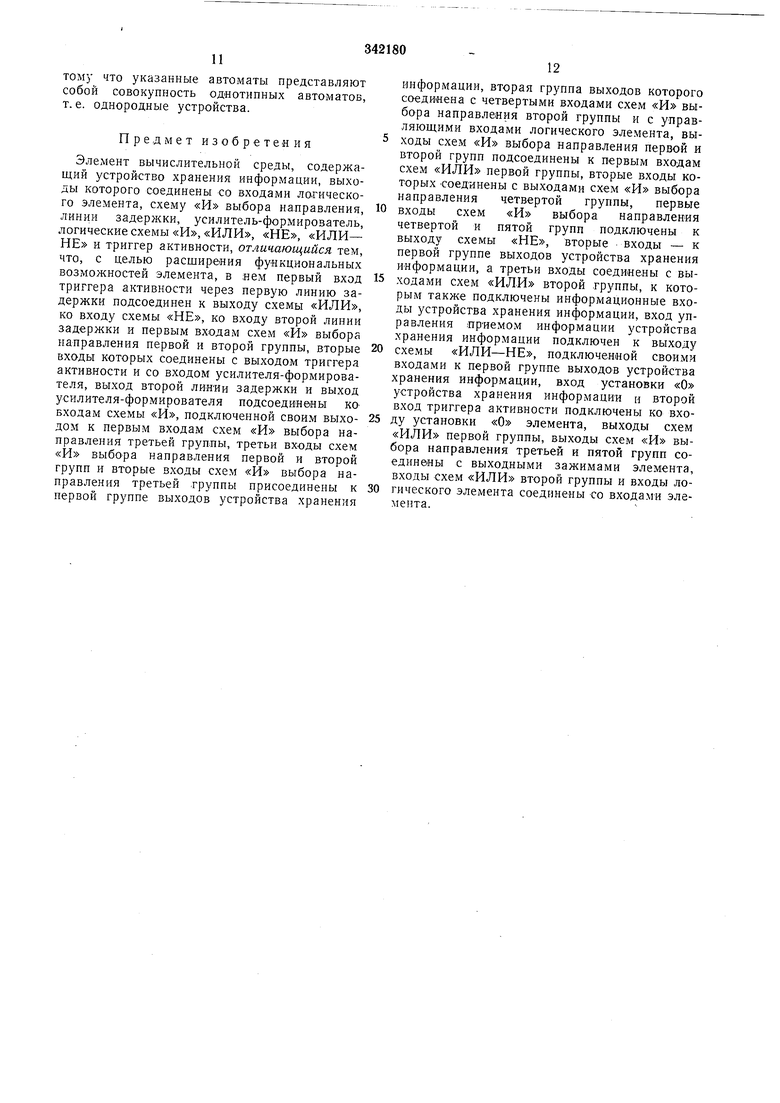

расшифровываться тем элементом, который ее принимает и должна располагаться в его ячейках памяти точно так же, как она была расположена в ячейках памяти элемента, который выдал свое описание. Элемент, который ся копией первого. Таким образом, предлагаемый элемент способен воспроизводить себя. На фиг. 1 приведен вариант функциональной схемы элемента с настраиваемой структурой; на фиг. 2 - расположение входов и выходов на сторонах элемента; на фиг. 3 -вариант структурно-однородного устройства (стрелками обозначены направления передача информации элементами). На чертежах обозначено: «И, «ИЛИ, «ИЛИ-НЕ, «НЕ -схемы, реализующие соответственно логические операции «конъюнкция, «дизъюнкция, «стрелка Пирса, «Инверсия, УФ - усилитель-формирователь; ЛЗ - ЛЗб - линии задержки; ТА - триггер активности; ЛЭ - логический элемент; 1-10 - входы элемента (входы 1-8 предназначены для приема сигналов, поступающих с выходов 11-18 смежных элементов или извне, входы Я 10 - для приема сигналов с выходов 19, 20 смежных элементов или извне); выходы для подачи сигналов на входы /-10 смежных элементов или во внещнее устройство; 21 - вход для подачи сигнала установки в «нуль триггеров блока памяти; 22, 23- входы логического элемента для приема сигналов с выходов 24, 25 смежных элементов или извне, 24,25-выходы логического элемента; 26-29- выходы блока памяти; 30-вход для установки в «нуль триггеров блока памяти. «ИЛИг - «ИЛИб - первая группа схем «ИЛИ, «ИЛИу -«ИЛИц - вторая группа схем «И1, «Иа - первая группа схем «И выбора направления; «Из, «Ие - вторая группа схем «И выбора направления; «И, «Ив -третья группа схем «И выбора направления; «Иэ -«Hi4 - четвертая группа схем «И выбора направления; «His, пятая группа схем «И выбора направления; «Ип -схема «И18 -«И21 - схемы «И установки в «единицу триггеров блока памяти. Блок памяти представляет собой группу триггеров (на фиг. 1 четыре триггера), единичные входы которых подключены к выходам линий задержек Л31-ЛЗ, а нулевые входы ко входу 30. Выходы триггеров блока памяти подключены к выходам 26-29 (выходы 26, 27 и 28, 29 - соответственно первая и вторая группы выходов блока памяти). В качестве логического элемента может быть использован любой многофункциональный элемент, удовлетворяющий требованиям теоремы о функциональной полноте, и вычислительное устройство, например интегратор. Подключение входов /-10, 22, 23 и выходов 11-20, 24 и 25 одного элемента к выходам 11-20, 24 л 25 к входам 1-10, 22 и 23 других элементов показано на фиг. 2 и 3. Входы /-10, 22 и 23 разбиты на две группы входов: к одной группе относятся входы /, 3, 5, 7, 9, 22, к другой - входы 2, 4, 6, 8 10 23. Выходы 11-20, 24, 25 также разбиты на две группы: к одной группе относятся выходы 11, 17, 18, 20 и 25. На входы /, 3, 5, 7, 9 и 22 и входы 2, 4, 6, 8, 10 и 23 элементов, расположенных внутри устройства, сигналы поступают соответственно с выходов 11, 12, 15, 16, 19 и 24 и выходов 13, 14, 17, 18, 20 и 25 смежных элементов. Код настройки элемента состоит из кода настройки логического элемента и кода выбора направления, указывающего какой из смежных элементов должен получать код настройки в следующем такте. Код выбора направления подается на входы схем «ИЛИ и «ИЛИв, а код настройки логического элемента - на входы схем «ИЛИд и «ИЛИю. В элементе код выбора направления хранится в триггерах блока памяти, подключенных выходами к выходам 26 и 27, а код настройка логического элемента-в триггерах, подключенных своими выходами к выходам 28, 29. Реакция элемента на код настройки, поданный на входы схем «ИЛИу -«ИЛИю, зависит от состояния выходов 26 и 27 (от кода выбора направления, хранящегося в триггерах блока памяти), от состояния схемы «ИЛИп (от значения сигнала на выходе схемы «НЕ), а также - от состояния триггера активности. Элемент может работать в режимах «настройка, «воспроизведение и «вычисление. Режим «настройк а. Для задания режима «настройка все триггеры блока памяти устанавливают в состояние «нуль, а триггер активности - в состояние «единица. Установка триггеров в исходное состояние осуществляется путем подачи импульса на вход 21. На входы схемы «ИЛИц подают сигнал «нуль. При настройке элемента из всех возможных состояний элемента выбирают такое, которое определяет требуемую схему коммутации (структуру соединений) входов /-10 и выхоов //-20, а также схему коммутации входов 22, 23 и выходов 24, 25 логического элемента. Пусть требуется настроить элемент на передачу сигналов а)с выходов 26, 27 блока памяти на выходы б)с выходов 28, 29 блока памяти на выходы 15-18, в)с выходов схем «ИЛИу, «ИЛИв (т. е. со входов /-4) на выходы 11-14, г)с выходов схем «ИЛИэ, «ИЛИю на выходы 15-18, д)с выхода схемы «ИЛИц на выходы 19,20. При этом сигнал «единица подается на вхоы схем «ИЛИ, «ИЛИз и кода настройки огического элемента-на входы схем ИЛИэ, «ИЛИю. Сигналы настройки прохоят через схемы «И18 -«И21 (так как на вторые входы этих схем с выхода схемы «ИЛИ- НЕ подан разрешающий сигнал) на входы /73i-Л34. Для нормальной работы элемента еобходимо, чтобы длительность каждого ходного импульса была меньще времени заЧае открываются схемы (сигналами с выходов 26, 27) и сигналы с выходов схем «ИЛИу -«ИЛИю проходят на выходы iJ-18. Если элемент свободен, т. е. на выходах 26, 27, имеется сигнал «нуль, то код настройки, поданный на входы схем «ИЛИ, - «ИЛИю, записывается в триггеры блока памяти элемента. При этом элемент сам управляет процессом записи информации, поступающей на его входы, а работа элемента в целом зависит от состояния триггеров блока памяти. При подаче второго кода на входы схем «ИЛИ -«ИЛИю реакция элемента на этот код -иная, так как в триггерах блока памяти имеется код настройки-сигналы с выходов схем «ИЛИу, «ИЛИв проходят на выходы //, 14, а сигналы с выходов схем «ИЛИэ, «ИЛИю -на выходы 15-18. Выбор указанных путей распространения сигналов определяется кодом выбора направления, хранящимся в триггерах блока памяти. Если каждый разряд кода выбора напр.чвления, хранящийся в триггерах блока памяти элемента, содержит единицу, то сигналы со входов /, 2 проходят на выходы 11, 13, сигналы со входов 3, 4 - на выходы 12, 14, сигналы со входов 5, 6 - на выходы 15, 17, сигналы со входов 7, 8 - на выходы 16, 18. Это означает, что код настройки, поступающий на входы элемента с выходов смежного элемента, может выдаваться элементом на все возможные направления, если на каждом из выходов 26, 27 блока памяти имеется сигнал «единица. Режим «в о с п р о и 3 в е д е в -и е. Режим «воспроизведение используется для получения нескольких элементов с одинаковыми кодами настройки в блоках памяти. Описание элемента (код настройки логического элемента и код выбора направления) с триггеров блока памяти (с выходов 26-29) выдается на его выходы 11-18. Причем направление выдачи описания элемента ОПределяется кодом выбора направления, хранящимся в триггерах самого элемента. Элемент, который принимает это описание, становится двойником того элемента, который выдал свое описание. Для задания режима «воспроизведение на входы /-8 подают сигналы «нуль. Воспроизведение элемента осуществляется путем подачи импульса на один из входов 9, 10 схемы «ИЛИц. Это приводит к тому, что сигналы С выходов триггеров блока памяти проходят через схемы на выходы элемента, так как на других входах этих схем «И имеются разрешающие сигналы (на одни входы сигнал «единица поступает с вы.хам схемы «ИЛИц, на другие -с выхода tpttrrepa активности), направление передачи сигналов (кода выбора направления и кода настройки логического элемента) определяется кодом выбора направления (сигналами с выходов 26, 27). Например, если на выходах 26, 28, 29 имеются сигналы «единица, а на дои схемы «И, «Из, «И.1 при подаче импульса на один из входов схемы «ИЛИц появляется сигнал «единица, а на выходах схем «И2, «Ид, «Иб -сигналы «нуль, так как хотя бы на одном из входов схем «Иг, «Из, «Иб имеется сигнал «нуль. Таким образом, при подаче импульса на вход схемы «ИЛИ на каждом выходе 11, 15 и 16 возникает сигнал «единица, а состояние выходов 12, 13, 14, 17, 18 не изменяется (на каждом из этих выходов сигнал «нуль). Следовательно, на выходах 11, 12, 15 и 16 элемента появляется код 1011, а на выходах 3, 14, 17, 18 - код 0000. Таким образом, элемент на выходы 11, 12, 15 и 16 (см. фиг. 1, 2) выдал свое собственное описание, т. е. код 1011, который хранится в триггерах блока памяти элемента. Первые два разряда кода 1011 (код 10) характеризует код выбора направления, а другие два разряда (код 11) -код настройки логического элемента. Это означает, что элемент выдал на свои выходы всю информацию с выходов собственных запоминающих элементов. Элемент, который принял эту информацию (рещение о приеме или не приеме описания другого элемента вырабатывается самим элементом), становится копией элемента, который выдал свое списание. Принять эту информацию может только элемент, на каждом из выходов 26, 27 которого имеется сигнал «нуль (см. режим «настройка). Рассмотрим реакцию триггера активности и работу усилителя-формирователя при подаче импульса на один из входов 9, 10. Выще был описан процесс воспроизведения элемента при подаче импульса на вход схемы «ИЛИц. Этот же импульс через линию задержки ЛЗд поступает на вход триггера активности ТА и переключает его из состояния «единица в состояние «нуль. При переключении усилитель-формирователь вырабатывает сигнал «нуль, длительность которого должна быть больще длительности импульса, поданного на вход схемы «ИЛИц. Сигналы «нуль с выхода усилителяформирователя поступает на вход схемы «И и запрещает прохождение сигнала с выхода линии задержки ЛЗе на входы схем «И, «И8. Это означает, что при подаче первого импульса на вход, схемы «ИЛИц состояние схем «И, «Ив не изменяется (на выходах каждой схемы сигнал «нуль). При подаче второго сигнала на вход схемы «ИЛИц сигнал с выхода этой схемы проходит через схему «И (на выходе усилителя-формирователя имеется сигнал «единица, так как триггер не переключается) на входы схем «И, «Ив. Выбор направления передачи этого сигнала определяется кодом выбора направления, хранящимся в триггерах блока памяти. В данном примере этот сигнал проходит на выход 9, так как на выходе 26 блока памяти имеется сигнал «единица, а на выходе 27 - сигнал «нуль. В качестве усилителя-формирователя может

вибратор. Единичный выход ждущего мультивибратора должен быть подключай ко входу схемы «Hi7. При переключении триггера активности из состояния «единица в состояние «нуль на выходе мультивибратора появляется сигнал «нуль, который запрещает прохождение сигнала с выхода схемы «ИЛИц на входы схем «Иу, «Ив. Для нормальной работы элемента необходимо, чтобы запрещающий сигнал на вход схемы «Hi поступал раньше разрешающего сигнала с выхода линии задерлски ЛЗ.

Функции каждой линии задержки может выполнять ждущий мультивибратор. Если элемент однажды выдал свое описание на выходы //-18, то повторно выдать свое описание он не может, так как на входы схем , подключенных к выходу триггера активности, действует сигнал «нуль.

Многократной выдачи своего описания элементом достигают двумя путями:

отсоединением единичного входа триггера активности от полюса 21 и подключением к источнику установки триггера активности в состояние «единица и применением вместо триггера активности мультивибратора, который после запуска способен возвращаться в исходное состояние.

В устройстве с настраиваемой структурой, выполненном на базе элемента, показанного на фиг. 1, входы 21 всех элементов могут быть соединены вместе и подключены через ключ к схеме, вырабатывающей переключательную функцию «константа единица. Функции такой схемы может выполнять источник питания. При замыкании ключа триггеры блоков памяти, всех элементов устанавливаются в состояние «нуль, а триггеры активности - в состояние «единица.

Вход 21 у элемента может отсутствовать, если он выполнен иа запоминающих эле.ментах, которые при подаче питания на элемент сами устанавливаются в исходное состояние, например на несимметричных триггерах и переключающих элементах с вольтамперной характеристикой 5-типа.

Режим «вычисление. В режиме «вычисление на входы /-10, 22 н 23 подается информация, подлежащая обработке элементом, а с выходов //-20, 24 и 25 снимается рез5льтат обработки.

В комбинированном режиме «вычисление могут быть использованы режим «настройка и режим «воспроизведение.

При этом любая переключательная функция может быть реализована в устройстве с настраиваемой структурой, выполненном на базе предлагаемого эле.мента, даже если логический элемент в элементе с настраиваемой структурой отсутствует. Схема «ИЛИц и схема «НЕ могзт выполнять функции логического элемента, настройка которого на выполнение той или иной коммутационной функции осуществляется кодом выбора направления. При этом схемы «ИЛИд, «ИЛИю,

«И|6, , «ИЛИ| -«ИЛИб, «И20, «И21, ЛЗз, ЛЗ., а триггеры блока памяти, подключенные к выхода.м 28 и 29, в элементе могут отсутствовать. Для этого нужно из элемента изъять указанные схемы, схемы «И1, «И2 снабдить четвертыми входами, а схему «И|7 -третьи.м входом, которые нужно соединить вместе и подключить к источнику для задания режима работы эле.мента. В режиме «настройка и «воспроизведение на этот полюс нужно подать сигнал «единица, а в режиме «вычисление - сигнал «нуль.

Рассмотрим некоторые режимы работы устройства с настраиваемой структурой на примере структурио-однородного устройства.

Р е ж им «н а с т р о и к а. Пусть требуется настроить элементы, входящие в цепочку 1, 2, 3, 4, 5 иа фиг. 3. Один из возможных алгоритмов настройки устройства включает:

а) Установку в «нуль триггеров блока памяти всех элементов и установку в «единицу триггеров активности всех эле.ментов (для этого подается сигнал на вход 21).

б) Подачу кода настройки на входы 1, 3, 5, 7 первого элемента цепочки. Сигналы со входов Л 5, 5 и 7 проходят через схемы на входы линий .,, а с выходов линий- на входы триггеров блока памяти первого элемента цепочки. Пусть на вход «1 этого элемента был подан сигнал «единица, а на вход «3 - сигнал «нуль. Это означает, что в следующем такте код настройки нолучит второй элемент цепочки (элемент 2 на фиг. 3).

Направления передачи сигналов каждым элементом цепочки /-5 на фиг. 3 обозначено стрелка.ми, помещенными внутри элементов (квадратов).

в)Подачу кода настройки второго элемента на входы /, 3, 5, 7 первого эле Мента цепочки.

Код настройки второго элемента со входов /, 3,.5, 7 первого элемента проходит на входы /, 3, 5, 7 второго элемента и записывается в триггеры блока памяти этого эле.мента. Пусть

на вход / первого элемента был подан сигнал «единица, а на вход 3 - сигнал «нуль. Это означает, что в триггеры блока памяти второго элемента был нодан такой же код выбора направления, что и при настройке первого элемента цепочки. В следующем такте код настройки получает третий элемент цепочки /-5.

г)Подачу кода настройки третьего элемента цепочки на входы ., 3, 5, 7 первого элемента

цепочки. Этот код проходит на входы 1, 3,5, 7 третьего элемента и записывается в триггерах блока памяти эле.мента. Настройка следующего элемента цецочки осуществляется в соответствии с пунктом б) и т. д. до тех пор, пока

не будзт настроены все элементы, входящие в схему реализуемого автомата.

Режим «размножение автоматов. Один из возможных алгоритмов размножения автоматов в устройстве с настраиваемой структурой

а)Настройки устройства на реализацию схемы одного автомата. Эта настройка может быть осуществлена, нанример, с помощью олисанного выше режима настройки. Допустим, настройка устройства на требуемый автомат была произведена по одной цепочке элементов, например по цепочке 1-5 на фиг. 3, а в последний элемент цепочки (в элемент 5 на фиг. 3) был записан код выбора направления следующего элемента.

б)Подачи первого импульса на вход 9 первого элемента цепочки. При этом сигналы с выходов триггеров блока памяти (26-29) первого элемеита проходят на входы /, 5, 5 и 7 второго элемента цепочки и распространяются по цепочке до тех пор, пока не найдут первого свободного элемента, в триггеры блока памяти которого они и записываются. Свободен тот элемент, на выходе схемы «ИЛИ-НЕ которого имеется сигнал «единица (см. режимы «настройка и «воспроизведение). Элементы цепочки с первого до последнего включительно не свободны, так как на выходе схемы «ИЛИ-НЕ каждого из них имеется сигнал «нуль. Свободен элемент, который расположен выше элемента 5 (на фиг. 3 обозначен цифрой /). Таким образом, в результате выполнения данного пункта в устройстве с настраиваемой структурой будет два элемента /, один из которых расположен в начале цепочки, а другой - в конце цепочки /-5-1, причем оба элемента не отличаются один от другого (в триггерах блока пал1яти каждого из них содержится одна и та же информация).

в)Подачи второго импульса на вход 9 первого элемента цепочки. Реакция этого элемента на второй импульс иная, так как триггер активности первого элемента находится в состоянии «нуль (см. режим «воспроизведение). Сигнал с выхода схемы «ИЛИ проходит на выход 19, т. е. на вход 9 второго элемента цепочки. Реакция второго элемента цепочки на этот импульс такая же, как первого элемента на первый импульс, но теперь по цепочке распространяются сигналы с выходов триггеров блока памяти второго элемента. Эти сигналы записываются в триггеры блока памяти элемента, расположенного правее элемента / (см. фиг. 3). Таким образом, после выполнения данного пункта в устройстве с настраиваемой структурой два элемента /и / и два элемента 2 и 2.

Если на вход цепочки подать столько импульсов, сколько элементов в цепочке, то в устройстве с настраиваемой структурой будет две цепочки (цепочки 1, 2, 3, 4 и 5 и /, 2, 3, 4 и 5 на фиг. 3), два автомата.

Если длину исходной цепочки обозначить т, то после подачи п импульсов на вход 9 первого элемента цепочки общее число цепочек составит .

тора импульсов на вход первого элемента цепочки. Если генератор импульсов реализовать в самом устройстве с настраиваемой структурой (например, образовать из логических элементов), то устройство с настраиваемой структурой способно само воспроизводить однотипные автоматы.

Количество информации, требуемой для реализации одного (исходного) автомата в устройстве с настраиваемой структурой, составит

Я| a(log2K -Iog2) бит,

где а - число элементов в пути (число элементов в цепочке), с помощью которого можно обойти все элементы, входящие в схему реализуемого автомата;

/С определяется числом смежных элементов, а q - числом состояний реализации логического элемента в элементе с настраиваемой структурой.

Если настройка устройства с настраиваемой структурой производится по нескольким цепочкам, то количество информации, требуемой для настройки устройства на реализацию одного автомата, составит

i -;

.i(logzK+logzq} бит,

1

где аг - число элементов в t-й цепочке; Р - число цепочек.

Количество информации, требуемой для настройки устройства с настраиваемой структурой на г+1 однотипных автоматов, составит

Яз a(logo(+log2«7)-log2r бит,

где величина logo определяет количество информации, требуемой для получения г автоматов. Таким образом, если в устройстве с настраиБаемой структурой имеется схема одного автомата, то для получения г таких же автоматов достаточно loga бит информации. Это означает, что количество информации, требуемой для получения однотипных автоматов, не

зависит от сложности исходного автомата (сложность исходного автомата может быть любой).

Предлагаемый элемент с настраиваемой структурой может быть использован для построения любых решеток, в том числе и симметрической решетки, т. е. такой решетки, каждый элемент которой может обмениваться информацией с любым (любыми) смежными элементами. Для этого нужно увеличить емкость блока памяти (количество триггеров), а также число входов и выходов (число схем «И и «ИЛИ). При этом, если требуется чтобы элемент обменивался информацией с К смежными элементами, то число входов у

каждой схемы «ИЛИ должно быть равно К. В устройстве, выполненном на базе предлагаемого элемента, просто реализуются такие автоматы, как регистры сдвига, двоичные счетчики, регистры параллельного действия, однотому что указанные автоматы представляют собой совокупность однотипных автоматов, т. е. однородные устройства.

Предмет изобретения

Элемент вычислительной среды, содержащий устройство хранения информации, выходы которого соединены со входами логического элемента, схему «И выбора направления, линии задерл ки, усилитель-формирователь, логические схемы «И, «ИЛИ, «НЕ, «ИЛИ- НЕ и триггер активности, отличающийся тем, что, с целью расширения функциональных возможностей элемента, в нем первый вход триггера активности через первую линию задержки подсоединен к выходу схемы «ИЛИ, ко входу схемы «НЕ, ко входу второй линии задержки и первым входам схем «И выбора направления первой и второй группы, вторые входы которых соединены с выходом триггера активности и со входом усилителя-формирователя, выход второй линии задержки и выход усилителя-формирователя подсоедииеиы ковходам схемы «И, подключеиной своим выходом к первым входам схем «И выбора направления третьей группы, третьи входы схем «И выбора направления первой и второй групп и вторые входы схем «И выбора направления третьей труппы присоединены к первой группе выходов устройства хранения

12

информации, вторая группа выходов которого соединена с четвертыми входами схем «И выбора направления второй группы и с управляющими входами логического элемента, выходы схем «И выбора направления первой и второй групп подсоединены к первым входам схем «ИЛИ первой группы, вторые входы которых Соединены с выходами схем «И выбора направления четвертой группы, первые

входы схем «И выбора направления четвертой и пятой групп подключены к выходу схемы «НЕ, вторые входы - к первой группе выходов устройства хранения информации, а третьи входы соединены с выходами схем «ИЛИ второй группы, к которым также подключены информационные входы устройства хранения информации, вход управления приемом информации устройства хранения информации подключен к выходу

схемы «ИЛИ-НЕ, подключенной своими входами к первой группе выходов устройства хранения информации, вход установки «О устройства хранения информации и второй вход триггера активности подключены ко входу установки «О элемента, выходы схем «ИЛИ первой группы, выходы схем «И выбора направления третьей и пятой групп соединены с выходными зажимами элемента, входы схем «ИЛИ второй группы и входы логического элемента соединены со входами элемента.

Фиг. 1

;- 5

-

шттг

73 К 77 75 20 25

Mllll

;

.2 ./5 76 .75 24

f « 5 J W J Фг/&.2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1969 |

|

SU255654A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU267183A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1970 |

|

SU259475A1 |

| СО АН СССР | 1969 |

|

SU239661A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИМВОЛЬНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010319C1 |

| Генератор псевдослучайных кодов | 1980 |

|

SU951301A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU266361A1 |

| Устройство синтаксически управляемого перевода | 1986 |

|

SU1399767A1 |

Фб/г.З

Даты

1972-01-01—Публикация