Ч

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть ис- пользовано дпя программирования бло-, ков постоянной памяти.5

Цель изобретения - увеличение количества выхода годньк блоков порто- явной памяти.

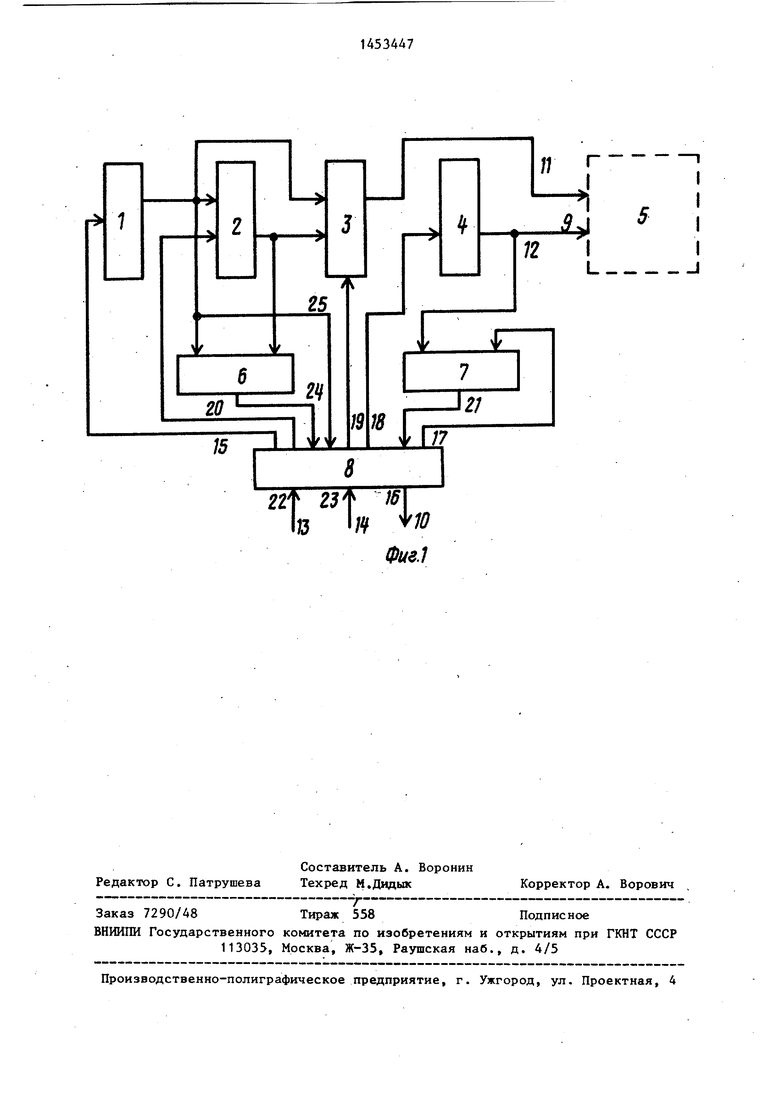

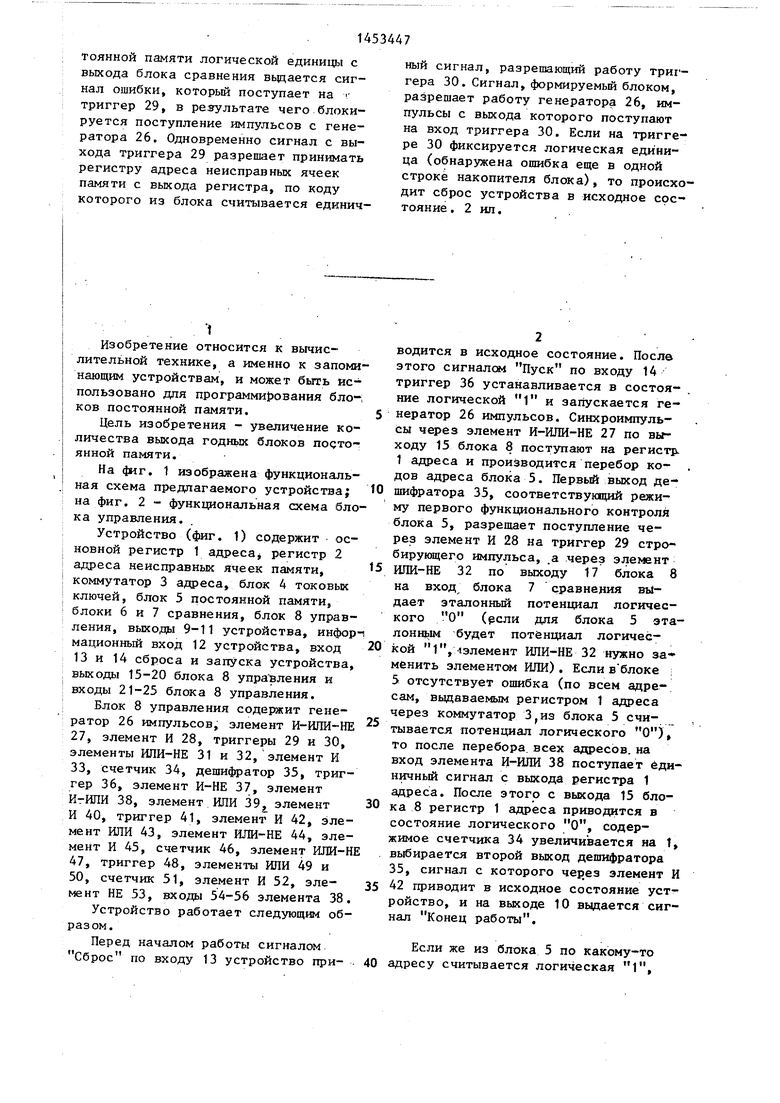

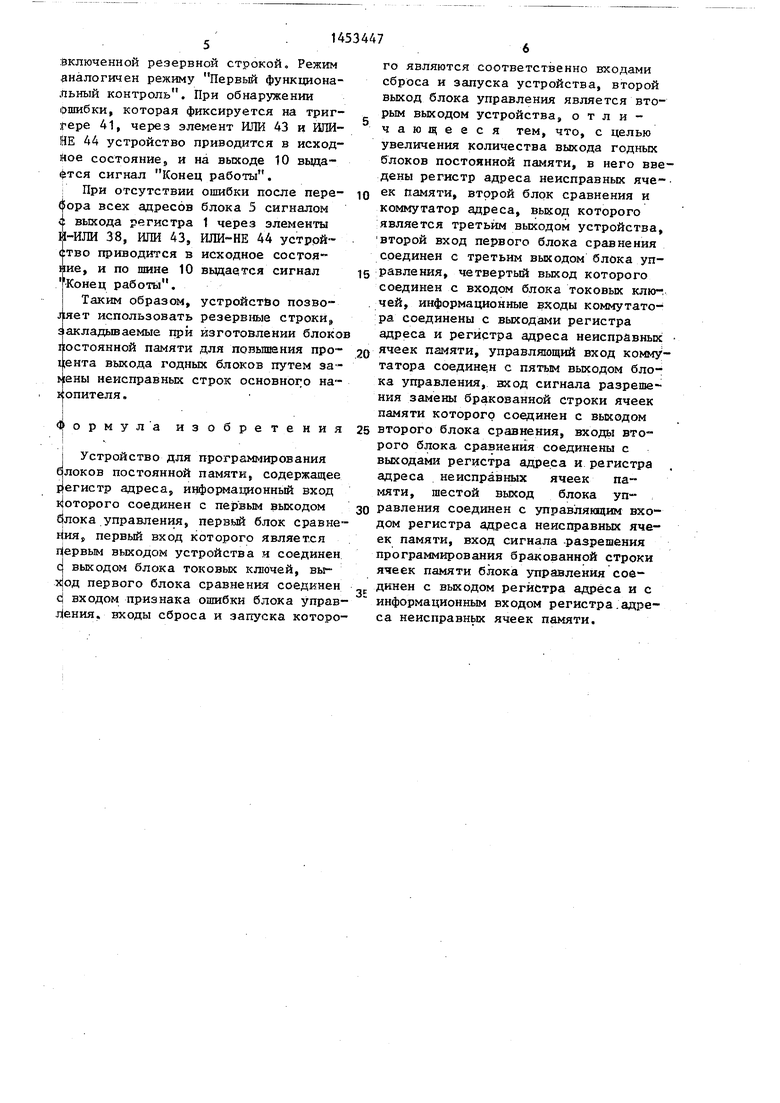

На фиг. 1 изображена функциональная схема предлагаемого устройства; Ю на фиг. 2 - функциональная схема блока управления.

Устройство (фиг. 1) содержит основной регистр 1 адреса регистр 2 адреса неисправных ячеек памяти,

коммутатор 3 адреса, блок 4 токовых ключей, блок 5 постоянной памяти, блоки б и 7 сравнения, блок 8 управления, выходы 9-11 устройства, инфорч мационный вход 12 устройства, вход 20 13 и 14 сброса и запуска устройства, выходы 15-20 блока 8 управления и входы 21-25 блока 8 управления.

Блок 8 управления содержит генератор 26 импульсов, элемент И-ИЛИ-НЕ 5 27, элемент И 28, триггеры 29 и 30, элементы Ш1И-НЕ 31 и 32, элемент И 33, счетчик 34, дешифратор 35, триггер 36, элемент И-НЕ 37, элемент Ит-ИПИ 38, элемент ИЛИ 39, элемент30

И 40, триггер 41, элемент И 42, элемент ИЛИ 43, элемент ИЛИ-НЕ 44, элемент И 45, счетчик 46, элемент ИЛИ-НЕ 47, триггер 48, элементы ИЛИ 49 и 50, счетчик 51, элемент И 52, эле- 35 мент НЕ 53, входы 54-56 элемента 38. Устройство работает следующим обазом.

Перед началом работы сигналом Сброс по входу 13 устройство при- . 40

водится в исходное состояние. После этого сигналом Пуск по входу 14 триггер 36 устанавливается в состояние логической 1 и запускается генератор 26 импульсов. Синхроимпульсы через элемент И-ИЛИ-НЕ 27 по выходу 15 блока 8 поступают на регистр. 1 адреса и производится перебор кодов адреса блока 5. Первьй выход дешифратора 35, соответствующий режиму первого функционального контроля блока 5, разрешает поступление через элемент И 28 на триггер 29 стро- бирующего импульса, .а через элемент ИЛИ-НЕ 32 по выходу 17 блока 8 на вход блока 7 сравнения выдает эталонный потенциал логического О (рели для блока 5 эта- лонньш будет потенциал логической 1,элемент ИЛИ-НЕ 32 нужно заменить элементом ИЛИ). Если в блоке 5 отсутствует ошибка (по всем адресам, выдаваемым регистром 1 адреса через коммутатор блока 5 считывается потенциал логического О), то после перебора, всех адресов, на вход элемента И-ИЛИ 38 поступает единичный сигнал с выхода регистра 1 адреса. После этого с выхода 15 блока 8 регистр 1 адреса приводится в состояние логического О, содержимое счетчика 34 увеличивается на t, выбирается второй выход дешифратора 35, сигнал с которого че1}ез элемент И 42 приводит в исходное состояние устройство, и на выходе 10 выдается сигнал Конец работы.

Если же из блока 5 по какому-то адресу считывается логическая 1,

то через блок 7 сравнения по входу 21 блока 8 на триггер 29 вьщается сигнал ошибки (логическая 1) и после поступления очередного стробирую- щего сигнала триггер 29 устанавлива- вается в единичное состояние. Блокируется дальнейшее поступление строби- рующих импульсов через элемент И 28, Одновременно по сигналу с выхода триггера 29 на регистр 2 адреса принимается код регистра 1, по которому из блока 5 считана логическая 1 и разрешается работа триггера 30 по С-входу, Продолжается дальнейшая проверка блока 5, результат которой принимается на триггер 30, Сигнал, формируемьй на выходе блока 6 сравнения, разрешает передачу стробирую- щих сигналов на вход триггера 30 только тогда, когда код адреса строки проверяемой ячейки памяти блока 5 не совпадает с содержимым регистра 2 адреса неисправной строки (игнорируется ошибка этой строки, так как она должна быть заменена), Если на триггере 30 фиксируется логическая 1 (обнарз/жена ошибка еще в одной строке блока 5), то происходит сброс

О

ся установка в единичное состояние триггера 48 импульса программирования, сигналом с второго выхода - его перевод в нулевое состояние, чем обеспечивается соответствукщая длит тельность импульса программирования. Сигналом с третьего выхода счетчик 46 приводится в состояние логического О и увеличивается на единицу содержимое счетчика 51 циклов программирования. Аналогичным образом формируется второй импульс программирования и т,д. После формирования необходимого для программирования ячеек одного адреса блока 5 количества импульсов, счетчик 51 формирует сигнал переполнения, который через элемент ИЛИ 50 приводит его в нулевое состояние и, через элемент 27 по выходу 15 блока 8 увеличивает :Держимое регистра 1 адреса на единицу, и весь цикл программирования повторяется для следукщего адреса бло- : 5 ка 5, Импульсы программирования с выхода триггера 48 по выходу 18 блока 8 поступают на блок 4 токовых ключей и после усиления в нем - блок 5, После программирования всех яче5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для поиска неисправных блоков и элементов | 1985 |

|

SU1309042A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2020 |

|

RU2723288C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1267415A1 |

Изобретение относится к вычислительной технике, а .именно к запоминающим устройствам, и может быть использовано для программирования блоков постоянной памяти. Цель изобретения - увеличение количества выхода годных блоков постоянной памяти достигается введением регистра адреса неисправных ячеек памяти, коммутатора, адреса и второго блока сравнения и , их связей с известными блоками. Если в проверяемом блоке 5 постоянной памяти отсутствует ошибка, то после перебора всех адресов.в регистре адреса на вход элемента И-ИЛИ 38 поступает единичный сигнал с его выхода. После этого с выхода 15 блока управления регистр приводится в состояние логического нуля, содержание счетчи ка 34 увеличивается на 1 и сигналом с выхода дешифратора. 35 через злемент И 42 устройство возвращает- . ся в исходное состо.яние, а на выходе устройства появляется сигнал Конец работы. При считывании из блока посо (В

устройства в исходное состояние через Q ек с выхода регистра 1 по кходу 25

элементы ИЛИ 43, ИЛИ-НЕ 44, триггер 36, и на выходе 10 выдается сигнал Конец работы,

i Если на триггере 30 до конца проверки блока 5 не фиксируется ошибка, то сигналом с выхода регистра 1 по входу 25 блока 8 через элемент И-ИЛИ 38 содержимое счетчика 34 увеличивается на единицу и устройство переходит на второй режим работы Прог ;раммирование неисправной строки для исключения ее из накопителя блока 5,

В этом режиме чере;з коммутатор 3 на блок 5 по разрядам, определяю- вцад код адреса его строки, передает-; - ся содержимое регистра 2, а по раз- . рядам, определяющим код адреса столбца - соответствующие разряды регист- ра 1, Производится перебор кодов ад- :ресов всех ячеек (столбцов) данной строки и их программирование происходит следующим образом.

Через элемент ИЛИ-НЕ 31 открьюа- ется второй канал элемента И-ИЛИ-НЕ 27 и разрешается поступление синхроимпульсов через элемент И 45 на С-: вход счетчика 46 формирования импульсов программирования. Сигналом с первого выхода счетчика 46 производит-

35

блока 5 через элемент И-ШШ 38 увеличивается содержимое счетчика 34 н единицу и устройство переходит в ре жим замены резервной строки, что со ответствует третьему вькоду дешифратора 35,

В этом режиме производится отключение .(например, пережиганием .соответствующих перемычек) связи ре 4Q зервной строки со всеми строками, кроме бракованной. Производится пе- ребор кодов адресов всех строк и их программирование аналогично режиму Программирование бракованной стро45

60

55

ки.

Когда в регистре 1 устанавливает ся код адреса неисправной бракованной строки, блок 6 сравнения вьщает сигнал равенства и блокируется формирование импульса программирования на триггере 48, После перебора кодо адресов всех строк на регистр 1 с его выхода через элемент И-ИЛИ 38 содержимое счетчика 34 увеличивается на единицу и через Ьлемент ИЛИ 3 регистр 1 приводится в нулевое состояние, и устройство переходит в ре жим Второй функциональньй контроль для проверки содержимого блока 5 с

5

блока 5 через элемент И-ШШ 38 увеличивается содержимое счетчика 34 на единицу и устройство переходит в режим замены резервной строки, что со ответствует третьему вькоду дешифратора 35,

В этом режиме производится отключение .(например, пережиганием .соответствующих перемычек) связи ре- Q зервной строки со всеми строками, кроме бракованной. Производится пе- ребор кодов адресов всех строк и их I программирование аналогично режиму Программирование бракованной строг

45

60

55

ки.

Когда в регистре 1 устанавливается код адреса неисправной бракованной строки, блок 6 сравнения вьщает сигнал равенства и блокируется формирование импульса программирования на триггере 48, После перебора кодов адресов всех строк на регистр 1 с его выхода через элемент И-ИЛИ 38 содержимое счетчика 34 увеличивается на единицу и через Ьлемент ИЛИ 39 регистр 1 приводится в нулевое состояние, и устройство переходит в режим Второй функциональньй контроль для проверки содержимого блока 5 с

включенной реэервной строкой. Режим аналогичен режиму Первьй функциональный контроль. При обнаружении (Ошибки, которая фиксируется на триг- j-epe 41, через элемент ИЛИ 43 и ИПЙ- ЙЕ 44 устройство приводится в исход- йое состояние, и на выходе 10 выда фтся сигнал Конец работы. : При отсутствии ошибки после пере- (iopa всех адресов блока 5 сигналом ; выхода регистра 1 через элементы М-ИЛИ 38, ИПИ 43, ИЛИ-НЕ 44 устройство приводится в исходное состоя™ иие, и по шине 10 выдается сигнал Конец работы.

Таким образом, устройстйо позволяет использовать резервные строки,, закладываемые при изготовлении блоко постоянной памяти для повьшюния про- выхода годных блоков путем замены неисправных строк основного на- 1 опителя.

ормул а изобретения

Устройство для программирования блоков постоянной памяти, содержащее регистр адреса, информационный вход KJOToporo соединен с первым выходом 4лока управления, первый блок сравне- ияу первый вход которого является л|ервым выходом устройства и соединен с вькодом блока токовых ключей, выход первого блока сравнения соединен с| входом признака ошибки блока управ- Jieния., входы сброса и запуска которо0

го являются соответственно входами сброса и запуска устройства, второй выход блока управления является вторым вькодом устройства, отличающееся тем, что, с целью увеличения количества выхода годных блоков постоянной памяти, в него введены регистр адреса неисправных ячеек памяти, второй блок сравнения и коммутатор адреса, вькод которого является третьим выходом устройства, второй вход первого блока сравнения соединен с третьим выходом блока уп5 равления, четвертый выход которого соединен с входом блока токовых клюг чей, информационные входы коммутатора соединены с выходами регистра адреса и регистра адреса неисправных

0 ячеек памяти, управляющий вход комму - татора соединен с пятым выходом блока управления, вход сигнала разрешения замены бракованной строки ячеек памяти которого соединен с вькодом

5 второго блока сравнения, входь второго блока сравнения соединены с выходами регистра адреса и регистра адреса неисправных ячеек памяти, шестой выход блока уп0 равления соединен с управляющим входом регистра адреса неисправных ячеек памяти, вход сигнала разрешения программирования бракованной строки ячеек памяти блока управления соединен с выходом регистра адреса и с информационным входом регистра.адреса неисправньк ячеек памяти.

Е

2t 25t Щ

b 1/ w

Фие.1

I

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для электрического программирования блоков постоянной памяти | 1981 |

|

SU955205A1 |

Авторы

Даты

1989-01-23—Публикация

1987-06-10—Подача