рации; область хранения кодов входных 45 6 устанавливаются в нулевое состоявоздействий и эталонных выходных реакций, представляющих в совокупности тестовый набор элементарного шага проводимого контроля,

ние. На приведенных схемах цепи уста новки устройства в .исходное состояни не показаны.

При нажатии кнопки Пуск 40

Контролируемый блок ДА 5 представ- 5о (Фиг° 4) в блоке 1 триггер 41 уста6 устанавливаются в нулевое состояние. На приведенных схемах цепи установки устройства в .исходное состояние не показаны.

При нажатии кнопки Пуск 40

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

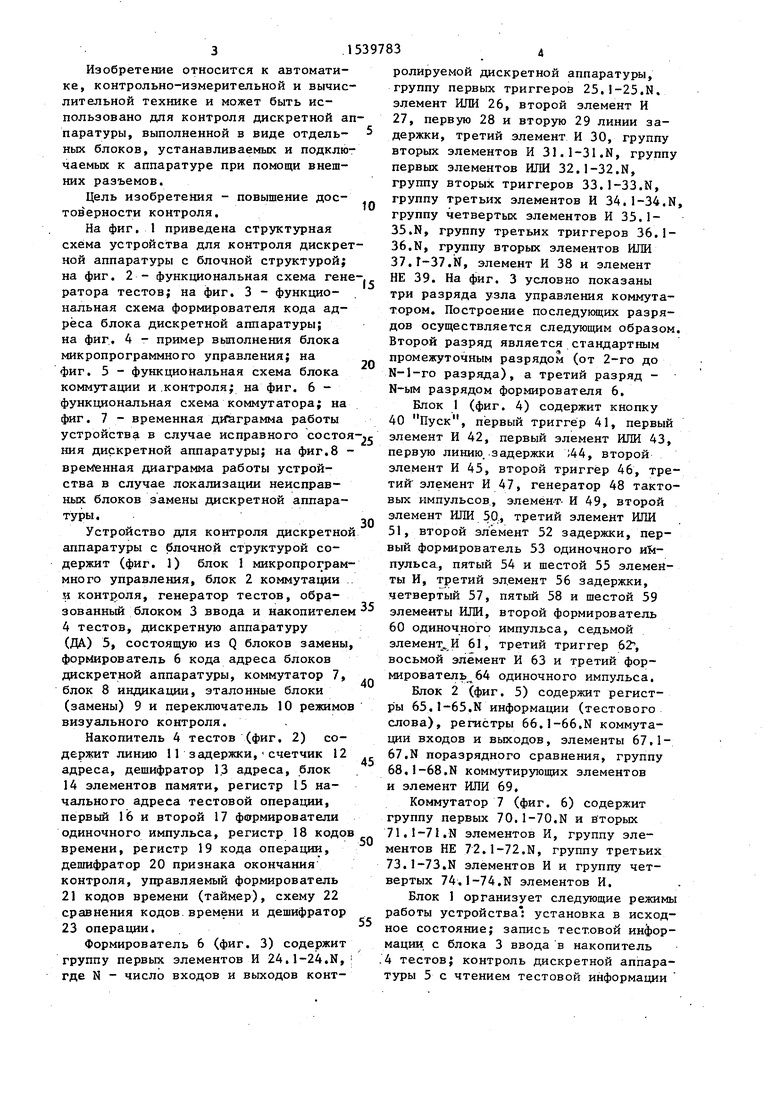

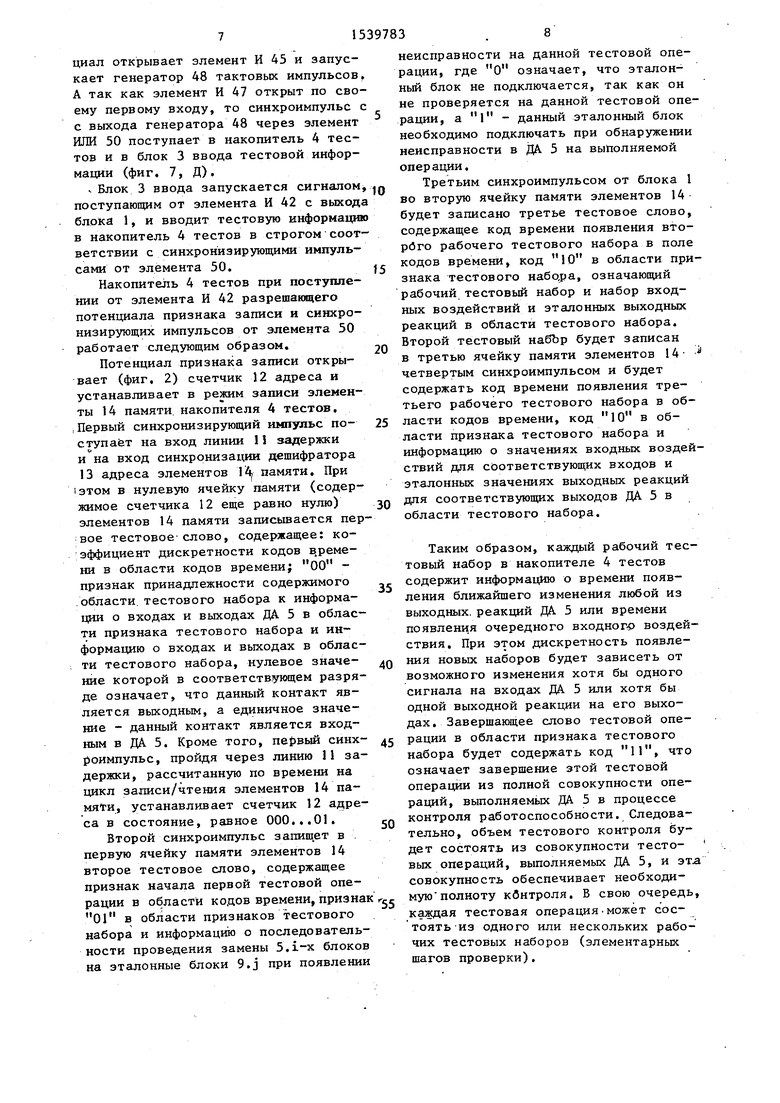

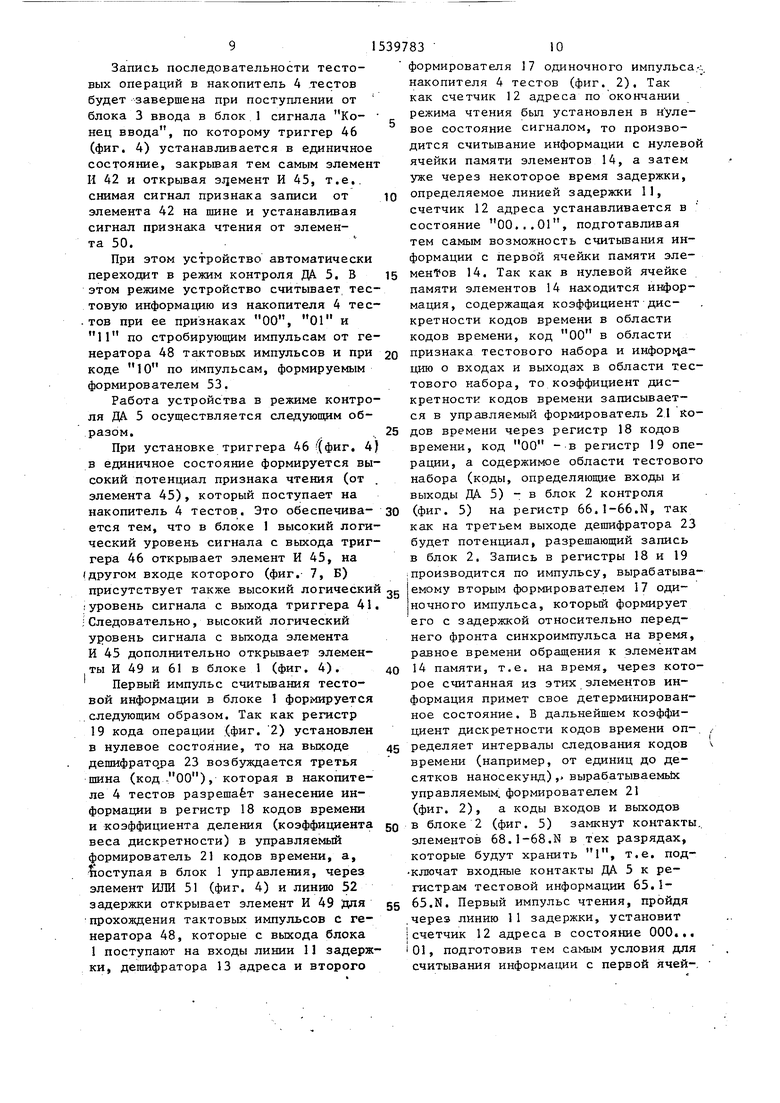

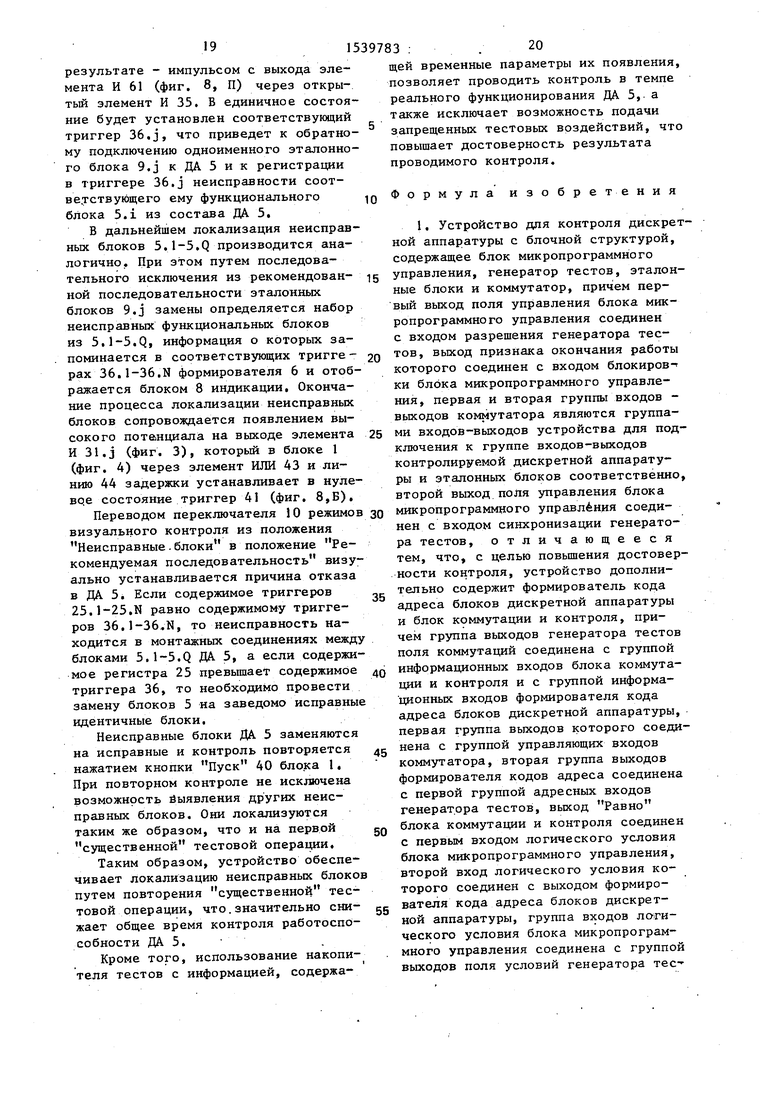

Изобретение относится к автоматике, контрольно-измерительной и вычислительной технике и может быть использовано для контроля дискретной аппаратуры, выполненной в виде отдельных блоков, устанавливаемых и подключаемых к аппаратуре при помощи внешних разъемов. Цель изобретения - повышение достоверности контроля. Устройство содержит блок 1 микропрограммного управления, блок 2 коммутации и контроля, генератор тестов, образованный блоком 3 ввода и накопителем 4 тестов, дискретную аппаратуру (ДА) 5, состоящую из Q блоков замены, формирователь 6 кода адреса блоков ДА, коммутатор 7, блок 8 индикации, эталонные блоки (замены) 9, переключатель 10 режимов визуального контроля. Устройство обеспечивает локализацию неисправных блоков путем повторения существенной тестовой операции, что значительно снижает общее время контроля работоспособности ДА 5. 1 з.п. ф-лы, 8 ил.

ляет собой дискретную аппаратуру с блочной структурой, под которой понимается устройство, состоящее из блоков 5.1-5.Q, соединяющихся между собой посредством внешних разъемов и имеющих возможность отключения с целью замены на эталонный блок замены. Формирователь 6 осуществляет регистрацию последовательности замены

5

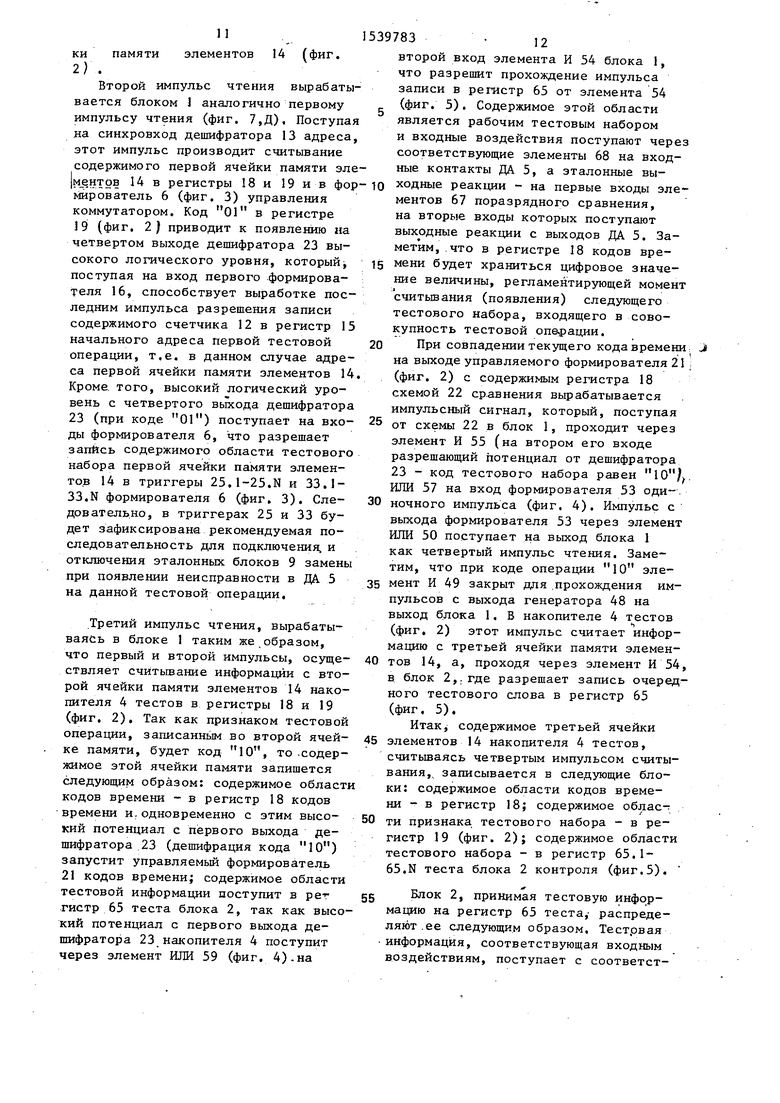

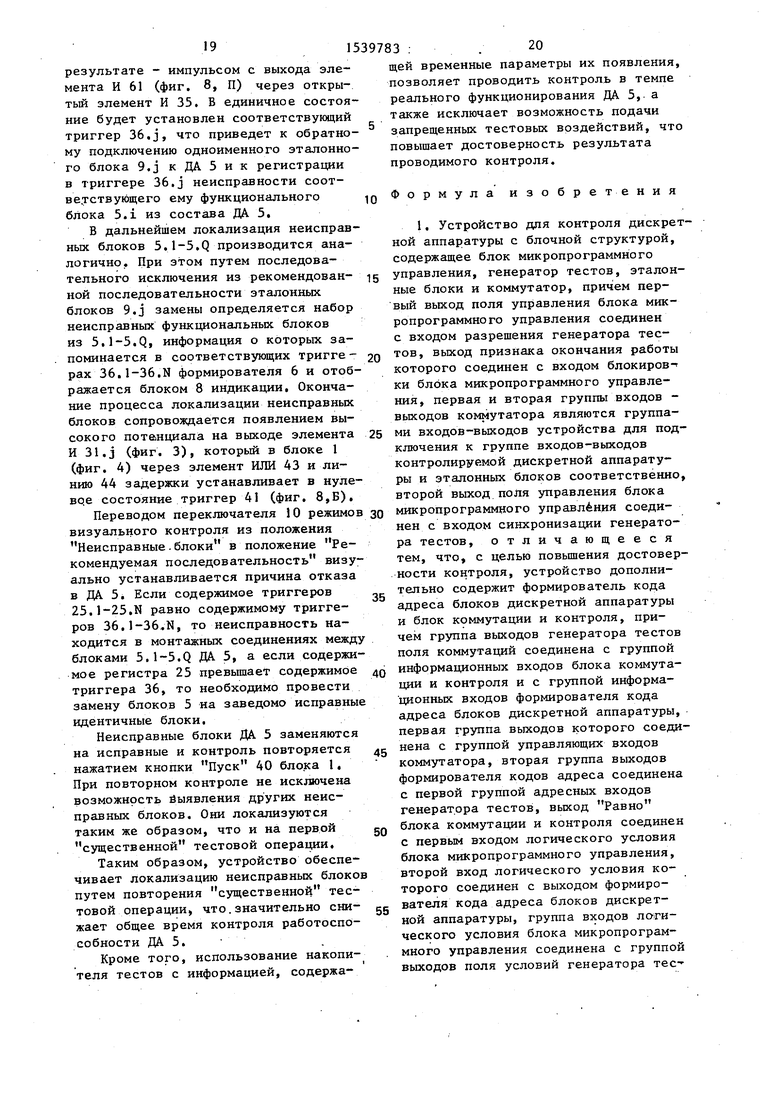

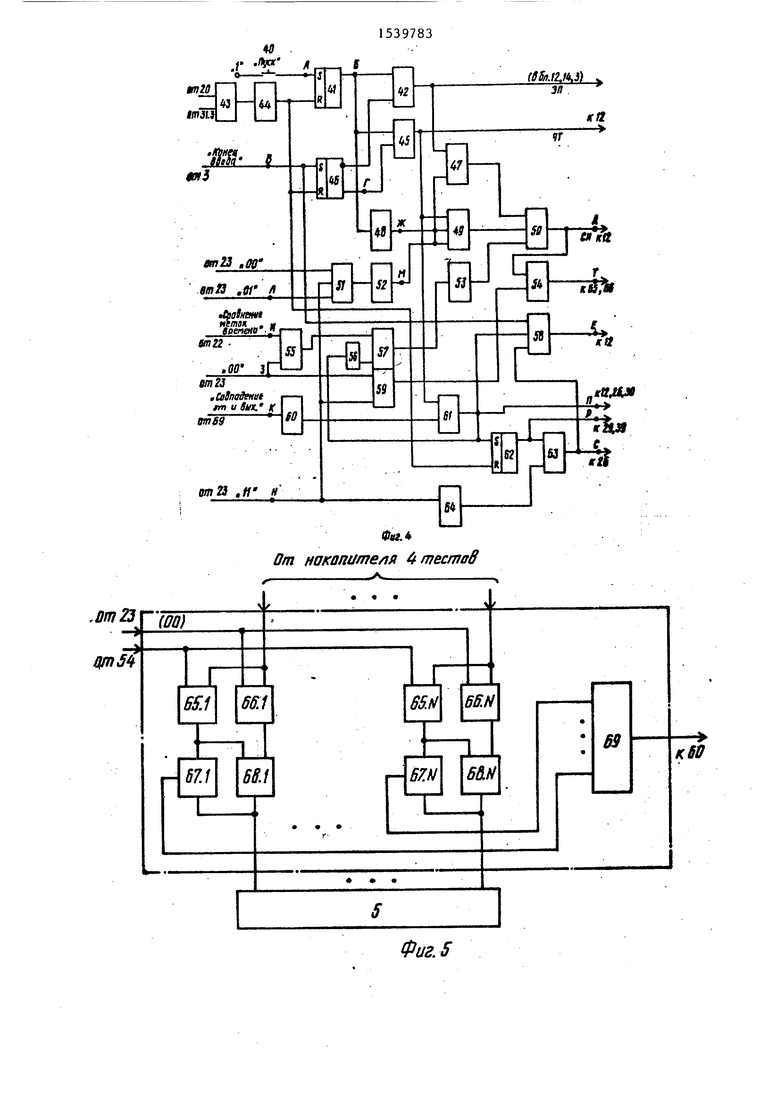

навливается в единичное состояние (фиг. 7, Б) и на выходе открытого ,элемента И 42 (признака записи) появляется высокий управляющий потенциал, который поступает в блок 3 ввода как сигнал запуска и в накопитель 4 тестов как управляющий сигнал режима на- копления поступающей тестовой информации. В блоке 1 этот высокий потен- ,

циал открывает элемент И 45 и запускает генератор 48 тактовых импульсов. А так как элемент И 47 открыт по своему первому входу, то синхроимпульс с с выхода генератора 48 через элемент ИЛИ 50 поступает в накопитель 4 тестов и в блок 3 ввода тестовой информации (фиг, 7, Д).

ч Блок 3 ввода запускается сигналом, поступающим от элемента И 42 с выхода блока 1, и вводит тестовую информацию в накопитель 4 тестов в строгом соответствии с синхронизирующими импульсами от элемента 50.

Накопитель 4 тестов при поступлении от элемента И 42 разрешающего потенциала признака записи и синхронизирующих импульсов от элемента 50 работает следующим образом.

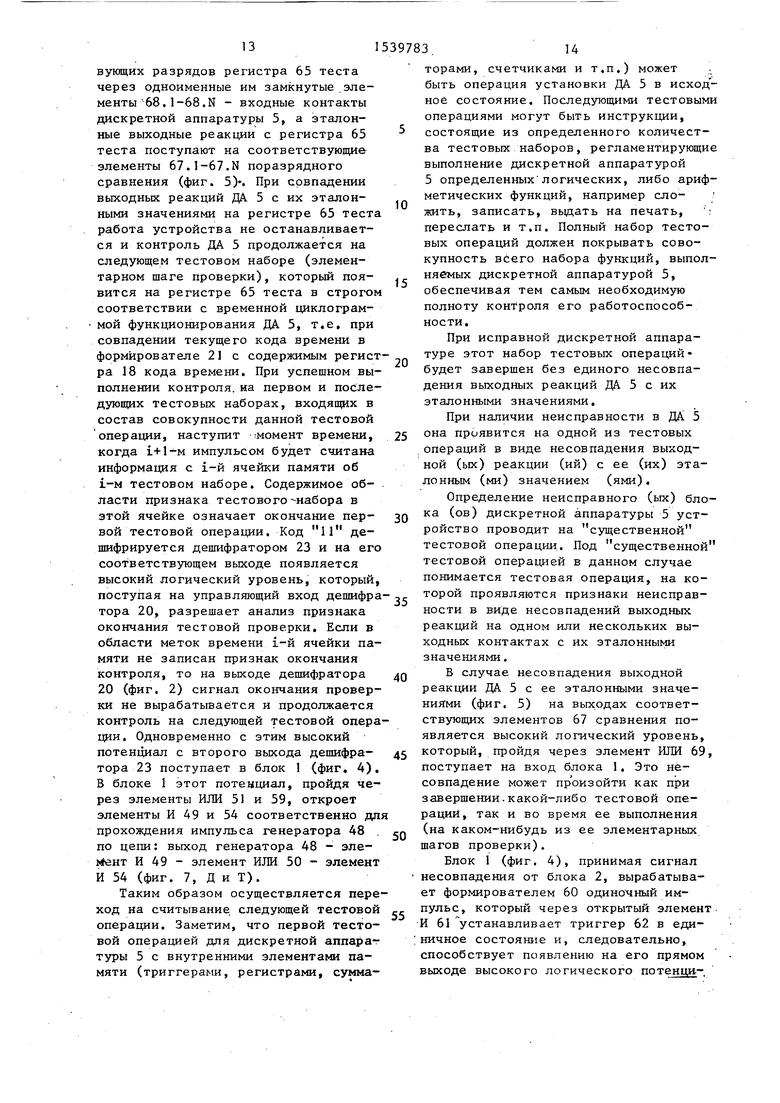

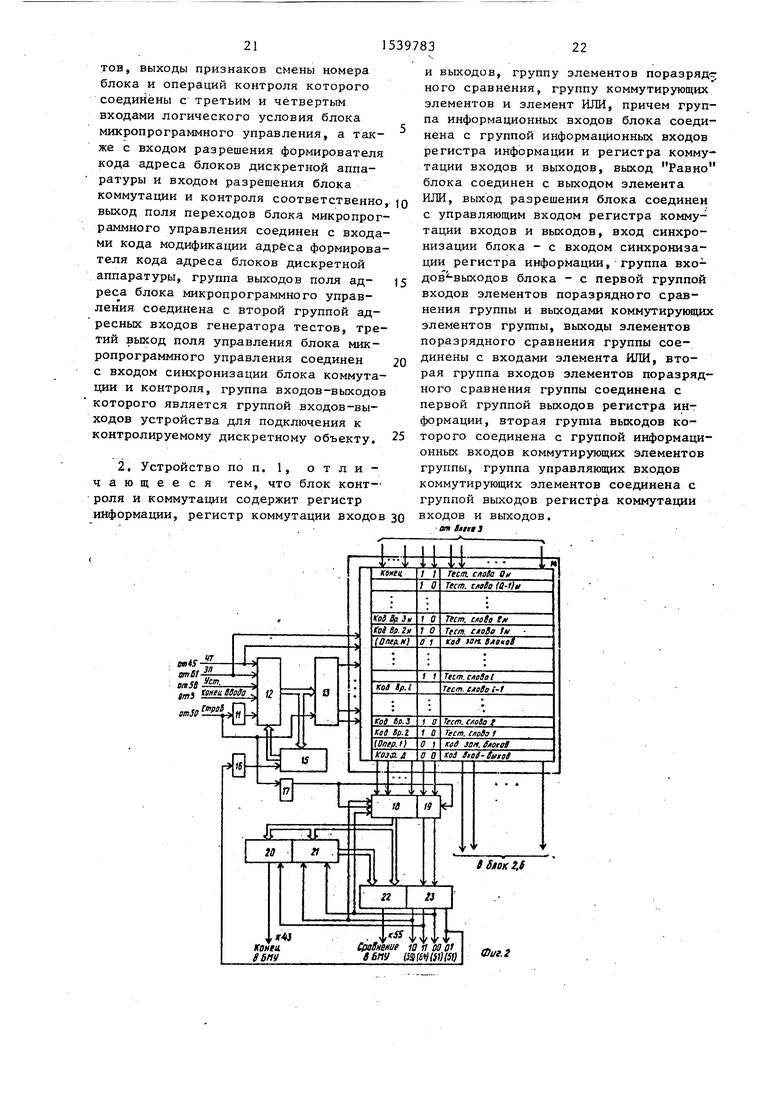

Потенциал признака записи открывает (фиг. 2) счетчик 12 адреса и устанавливает в режим записи элементы 14 памяти накопителя 4 тестов. Первый синхронизирующий импульс по- ступает на вход линии 1I задержки и на вход синхронизации дешифратора 13 адреса элементов 14 памяти. При i этом в нулевую ячейку памяти (содержимое счетчика 12 еще равно нулю) элементов 14 памяти записывается первое тестовое слово, содержащее: коэффициент дискретности кодов в.реме- ни в области кодов времени; 00 - признак принадлежности содержимого области тестового набора к информации о входах и выходах ДА 5 в области признака тестового набора и информацию о входах и выходах в области тестового набора, нулевое значе- ние которой в соответствующем разряде означает, что данный контакт является выходным, а единичное значение - данный контакт является входным в ДА 5. Кроме того, первый синх- роимпульс, пройдя через линию 11 задержки, рассчитанную по времени на цикл записи/чтения элементов 14 памяти, устанавливает счетчик 12 адреса в состояние, равное 000...01.

Второй синхроимпульс запишет в первую ячейку памяти элементов 14 второе тестовое слово, содержащее признак начала первой тестовой операции в области кодов времени, признак 01 в области признаков тестового набора и информацию о последовательности проведения замены 5.1-х блоков на эталонные блоки 9.J при появлении

Q

5

П

5 0 Q 5

г

неисправности на данной тестовой операции, где О означает, что эталонный блок не подключается, так как он не проверяется на данной тестовой операции, а 1 - данный эталонный блок необходимо подключать при обнаружении неисправности в ДА 5 на выполняемой опер ации,

Третьим синхроимпульсом от блока 1 во вторую ячейку памяти элементов 14 будет записано третье тестовое слово, содержащее код времени появления вто- рбго рабочего тестового набора в поле кодов времени, код 10 в области признака тестового набора, означающий рабочий тестовый набор и набор входных воздействий и эталонных выходных реакций в области тестового набора. Второй тестовый набор будет записан в третью ячейку памяти элементов 14 четвертым синхроимпульсом и будет содержать код времени появления третьего рабочего тестового набора в области кодов времени, код 10 в области признака тестового набора и информацию о значениях входных воздействий для соответствующих входов и эталонных значениях выходных реакций для соответствующих выходов ДА 5 в области тестового набора.

Таким образом, каждый рабочий тестовый набор в накопителе 4 тестов содержит информацию о времени появления ближайшего изменения любой из выходных реакций ДА 5 или времени появления очередного входног-р воздействия. При этом дискретность появления новых наборов будет зависеть от возможного изменения хотя бы одного сигнала на входах ДА 5 или хотя бы одной выходной реакции на его выходах. Завершающее слово тестовой операции в области признака тестового набора будет содержать код 11, что означает завершение этой тестовой операции из полной совокупности операций, выполняемых ДА 5 в процессе контроля работоспособности. Следовательно, объем тестового контроля будет состоять из совокупности тесто- вых операций, выполняемых ДА 5, и этл совокупность обеспечивает необходимую полноту квнтроля. В свою очередь, каждая тестовая операция.может состоять из одного или нескольких рабочих тестовых наборов (элементарных шагов проверки).

Запись последовательности тестовых операций в накопитель 4 тестов будет завершена при поступлении от блока 3 ввода в блок сигнала Ко- нец ввода, по которому триггер 46 (фиг. 4) устанавливается в единичное состояние, закрьюая тем самым элемент И 42 и открывая элемент И 45, т.е. снимая сигнал признака записи от элемента 42 на шине и устанавливая сигнал признака чтения от элемента 50.

При этом устройство автоматически переходит в режим контроля ДА 5. В этом режиме устройство считывает тестовую информацию из накопителя 4 тестов при ее признаках 00, 01 и 11 по стробирующим импульсам от генератора 48 тактовых импульсов и при коде 10 по импульсам, формируемым формирователем 53.

Работа устройства в режиме контроля ДА 5 осуществляется следующим образом.

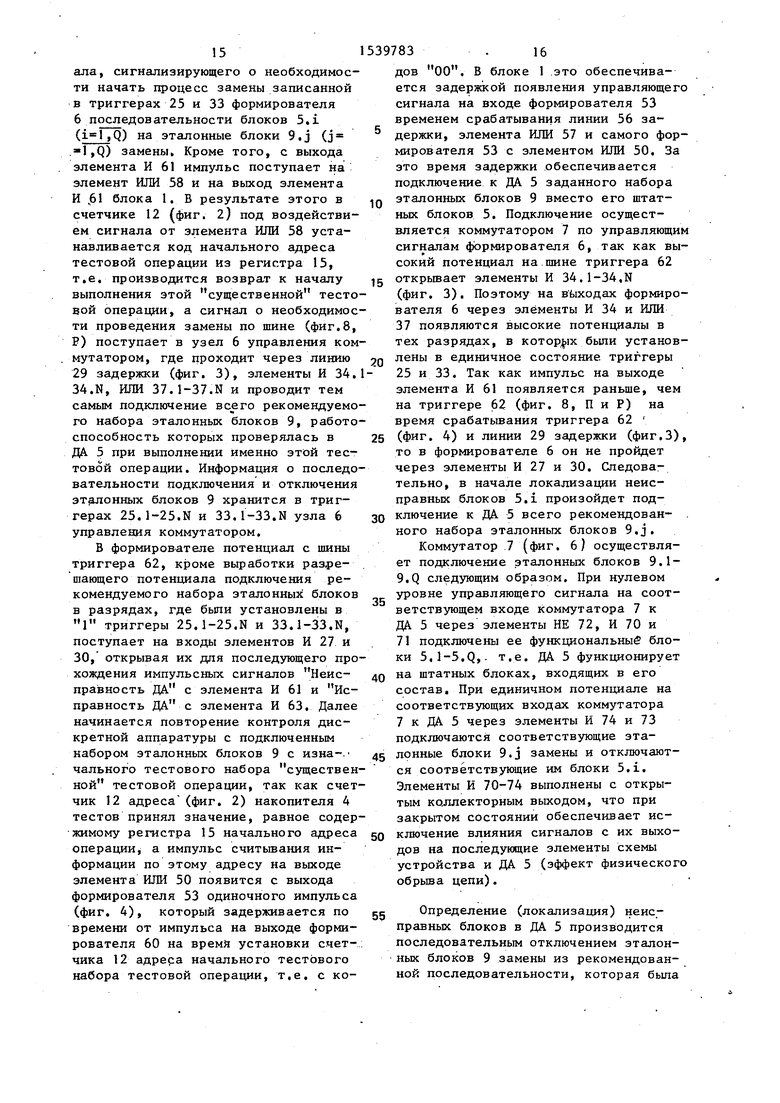

При установке триггера 46 (фиг. 4) в единичное состояние формируется высокий потенциал признака чтения (от элемента 45), который поступает на накопитель 4 тестов. Это обеспечива- ется тем, что в блоке 1 высокий логический уровень сигнала с выхода триггера 46 открывает элемент И 45, на другом входе которого (фиг. 7, Б) присутствует также высокий логический уровень сигнала с выхода триггера 41. Следовательно, высокий логический уровень сигнала с выхода элемента И 45 дополнительно открывает элементы И 49 и 61 в блоке 1 (фиг. 4).

Первый импульс считывания тестовой информации в блоке 1 формируется следующим образом. Так как регистр 19 кода операции (фиг. 2) установлен в нулевое состояние, то на выходе дешифратора 23 возбуждается третья шина (код 00), которая в накопителе 4 тестов разрешает занесение информации в регистр 18 кодов времени и коэффициента деления (коэффициента веса дискретности) в управляемый формирователь 21 кодов времени, а, поступая в блок 1 управления, через элемент ИЛИ 51 (фиг. 4) и линию 52 задержки открывает элемент И 49 для прохождения тактовых импульсов С генератора 48, которые с выхода блока 1 поступают на входы линии 11 задержки, дешифратора 13 адреса и второго

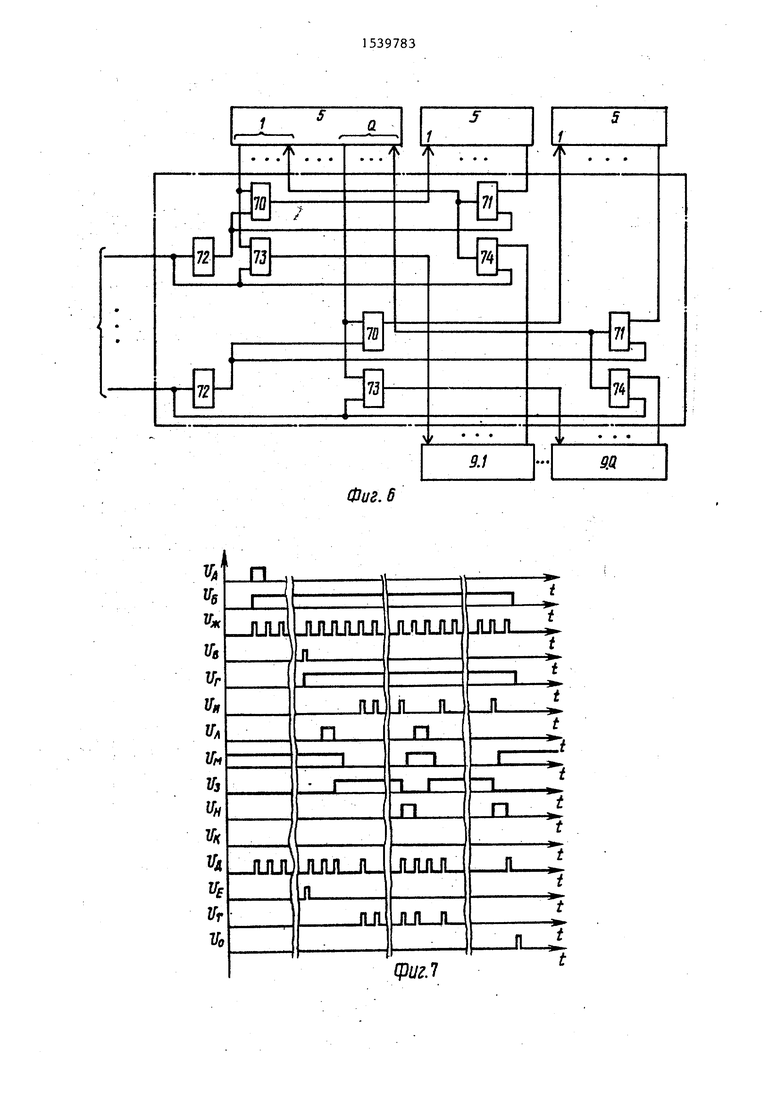

формирователя 17 одиночного импульса накопителя 4 тестов (фиг. 2). Так как счетчик 12 адреса по окончании режима чтения был установлен в нулевое состояние сигналом, то производится считывание информации с нулево ячейки памяти элементов 14, а затем уже через некоторое время задержки, определяемое линией задержки 11, счетчик 12 адреса устанавливается в состояние 00...01, подготавливая тем самым возможность считывания информации с первой ячейки памяти элементов 14. Так как в нулевой ячейке памяти элементов 14 находится информация, содержащая коэффициент дискретности кодов времени в области кодов времени, код 00 в области признака тестового набора и информ.а- цию о входах и выходах в области тестового набора, то коэффициент дискретности кодов времени записывается в управляемый формирователь 21 кодов времени через регистр 18 кодов времени, код 00 - в регистр 19 операции, а содержимое области тестовог набора (коды, определяющие входы и выходы ДА 5) - в блок 2 контроля (фиг. 5) на регистр 66.1-66.N, так как на третьем выходе дешифратора 23 будет потенциал, разрешающий запись в блок 2. Запись в регистры 18 и 19 производится по импульсу, вырабатываемому вторым формирователем 17 одиночного импульса, который формирует его с задержкой относительно переднего фронта синхроимпульса на время, равное времени обращения к элементам 14 памяти, т.е. на время, через которое считанная из этих элементов информация примет свое детерминированное состояние. В дальнейшем коэффициент дискретности кодов времени определяет интервалы следования кодов времени (например, от единиц до десятков наносекунд),. вырабатываемых управляемым, формирователем 21 (фиг. 2), а коды входов и выходов в блоке 2 (фиг. 5) замкнут контакты элементов 68.1-68.N в тех разрядах, которые будут хранить 1, т.е. подключат входные контакты ДА 5 к регистрам тестовой информации 65.1- 65.N. Первый импульс чтения, пройдя через линию 11 задержки, установит

счетчик 12 адреса в состояние 000...

101, подготовив тем самым условия для считывания информации с первой ячей

элементов

ки памяти элементов 14 (фиг. 2) .

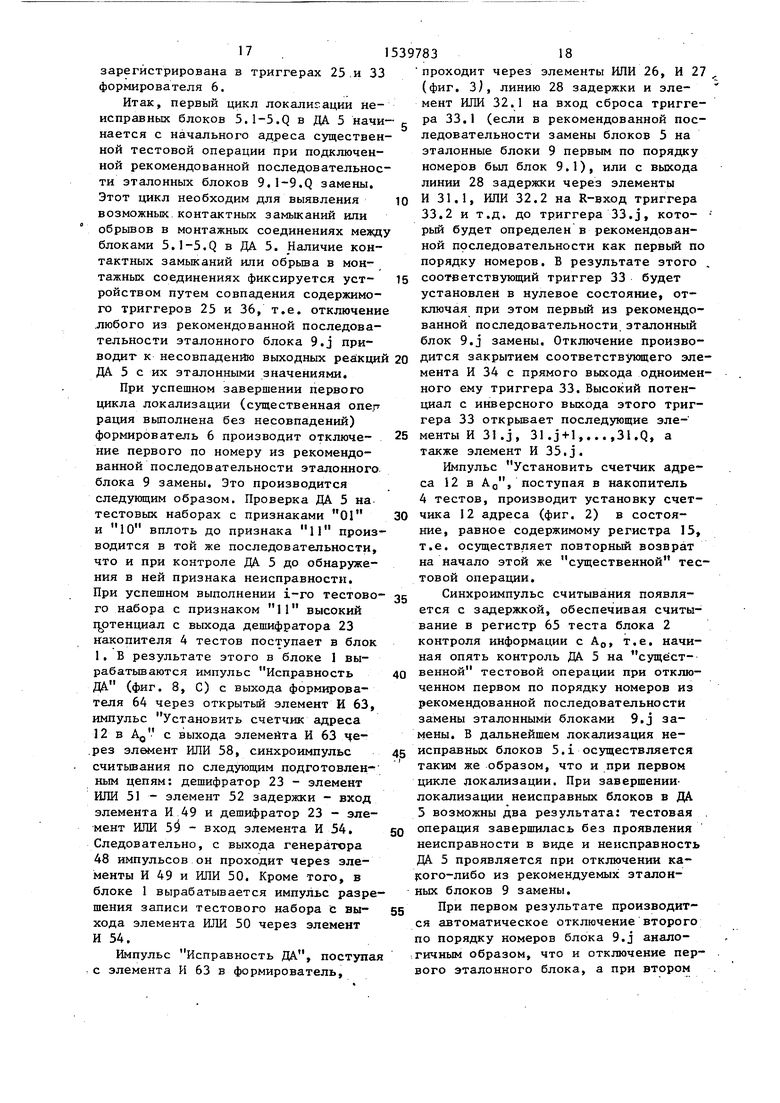

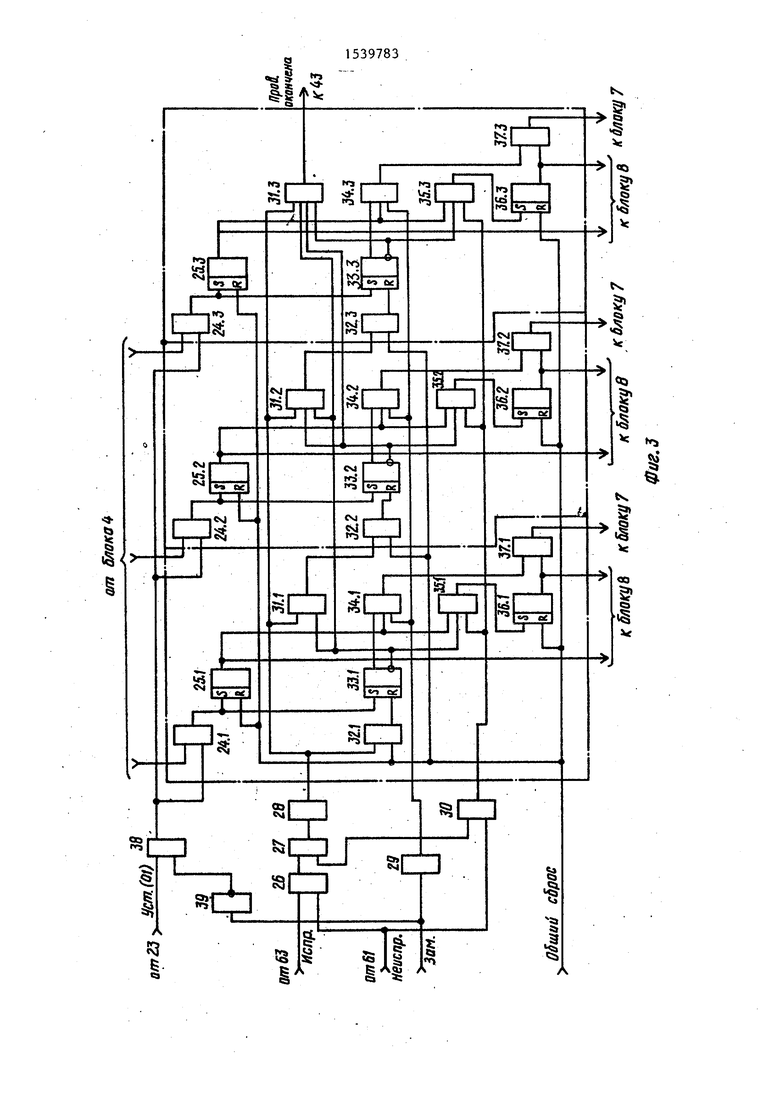

Второй импульс чтения вырабатывается блоком 1 аналогично первому импульсу чтения (фиг. 7,Д). Поступая на синхровход дешифратора 13 адреса, этот импульс производит считывание содержимого первой ячейки памяти эле 14 в регистры 18 и 19 и в формирователь 6 (фиг. 3) управления коммутатором. Код 01 в регистре 19 (фиг. 2) приводит к появлению на четвертом выходе дешифратора 23 высокого логического уровня, который, поступая на вход первого формирователя 16, способствует выработке последним импульса разрешения записи содержимого счетчика 12 в регистр 15 начального адреса первой тестовой операции, т.е. в данном случае адреса первой ячейки памяти элементов 14 Кроме того, высокий логический уровень с четвертого выхода дешифратора 23 (при коде 01) поступает на входы формирователя 6, что разрешает запись содержимого области тестового набора первой ячейки памяти элементов 14 в триггеры 25.1-25.N и 33.1- 33.N формирователя 6 (фиг. 3). Следовательно, в триггерах 25 и 33 будет зафиксирована рекомендуемая последовательность для подключения, и отключения эталонных блоков 9 замены при появлении неисправности в ДА 5 на данной тестовой операции.

Третий импульс чтения, вырабатываясь в блоке 1 таким же,образом, что первый и второй импульсы, осуществляет считывание информации с второй ячейки памяти элементов 14 накопителя 4 тестов в регистры 18 и 19 (фиг. 2). Так как признаком тестовой операции, записанным во второй ячейке памяти, будет код 10, то .содержимое этой ячейки памяти запишется следующим образом: содержимое области кодов времени - в регистр 18 кодов времени и.одновременно с этим высокий потенциал с первого выхода дешифратора 23 (дешифрация кода 10) запустит управляемый формирователь 21 кодов времени; содержимое области тестовой информации поступит в ре- гистр 65 теста блока 2, так как высокий потенциал с первого выхода дешифратора 23 накопителя 4 поступит через элемент ИЛИ 59 (фиг. 4).на

539783 12

второй вход элемента И 54 блока 1, что разрешит прохождение импульса записи в регистр 65 от элемента 54 (фиг. 5). Содержимое этой области является рабочим тестовым набором и входные воздействия поступают через соответствующие элементы 68 на входные контакты ДА 5, а эталонные выfO ходные реакции - на первые входы элементов 67 поразрядного сравнения, на вторые входы которых поступают выходные реакции с выходов ДА 5. Заметим, что в регистре 18 кодов вре15 мени будет храниться цифровое значение величины, регламентирующей момент считывания (появления) следующего тестового набора, входящего в совокупность тестовой операции.

20 При совпадении текущего кода времени л на выходе управляемого формирователя 21 i (фиг. 2) с содержимым регистра 18 схемой 22 сравнения вырабатывается импульсный сигнал, который, поступая

25 от схемы 22 в блок 1, проходит через элемент И 55 (на втором его входе разрешающий потенциал от дешифратора 23 - код тестового набора равен ИЛИ 57 на вход формирователя 53 оди-

30 ночного импульса (фиг. 4). Импульс с выхода формирователя 53 через элемент ИЛИ 50 поступает на выход блока 1 как четвертый импульс чтения. Заметим, что при коде операции 10 эле35 мент И 49 закрыт для прохождения импульсов с выхода генератора 48 на выход блока 1. В накопителе 4 тестов (фиг. 2) этот импульс считает информацию с третьей ячейки памяти элемен40 тов 14, а, проходя через элемент И 54, в блок 2,.где разрешает запись очередного тестового слова в регистр 65 (фиг. 5).

Итак, содержимое третьей ячейки

45 элементов 14 накопителя 4 тестов,

считываясь четвертым импульсом считывания,, записывается в следующие блоки: содержимое области кодов времени - в регистр 18; содержимое облас50 ти признака тестового набора - в регистр 19 (фиг. 2); содержимое области тестового набора - в регистр 65.1- 65.N теста блока 2 контроля (фиг.5).

55 Блок 2, принимая тестовую информацию на регистр 65 теста,- распределяют ее следующим образом. Тестрвая информация, соответствующая входным воздействиям, поступает с соответст13

вующих разрядов регистра 65 теста через одноименные им замкнутые элементы 68. 1-68. N - входные контакты дискретной аппаратуры 5, а эталонные выходные реакции с регистра 65 теста поступают на соответствующие элементы 67.1-67.N поразрядного сравнения (фиг. 5). При совпадении выходных реакций ДА 5 с их эталонными значениями на регистре 65 теста работа устройства не останавливается и контроль ДА 5 продолжается на следующем тестовом наборе (элементарном шаге проверки), который появится на регистре 65 теста в строгом соответствии с временной циклограм- мой функционирования ДА 5, т.е. при совпадении текущего кода времени в формирователе 21 с содержимым регистра 18 кода времени. При успешном выполнении контроля, на первом и последующих тестовых наборах, входящих в состав совокупности данной тестовой операции, наступит момент времени, когда i+1-м импульсом будет считана информация с i-й ячейки памяти об i-м тестовом наборе. Содержимое области признака тестового-набора в этой ячейке означает окончание первой тестовой операции. Код 11 дешифрируется дешифратором 23 и на его соответствующем выходе появляется высокий логический уровень, который,

10

15

торами, счетчиками и т.п.) может быть операция установки ДА 5 в исход ное состояние. Последующими тестовым операциями могут быть инструкции, состоящие из определенного количества тестовых наборов, регламентирующи выполнение дискретной аппаратурой 5 определенных логических, либо ариф метических функций, например сложить, записать, выдать на печать, переслать и т.п. Полный набор тестовых операций должен покрывать совокупность всего набора функций, выпол няемых дискретной аппаратурой 5, обеспечивая тем самым необходимую полноту контроля его работоспособности.

При исправной дискретной аппаратуре этот набор тестовых операций- будет завершен без единого несовпадения выходных реакций ДА 5 с их эталонными значениями.

При наличии неисправности в ДА 5 она проявится на одной из тестовых операций в виде несовпадения выходной (ых) реакции (ий) с ее (их) эталонным (ми) значением (ями).

Определение неисправного (ых) бло ка (ов) дискретной аппаратуры 5 устройство проводит на существенной тестовой операции. Под существенной тестовой операцией в данном случае понимается тестовая операция, на ко20

25

30

поступая на управляющий вход дешифра- ,5 торой проявляются признаки неисправ40

тора 20, разрешает анализ признака окончания тестовой проверки. Если в области меток времени i-й ячейки памяти не записан признак окончания контроля, то на выходе дешифратора 20 (фиг, 2) сигнал окончания проверки не вырабатывается и продолжается контроль на следующей тестовой операции. Одновременно с этим высокий потенциал с второго выхода дешифра- д5 тора 23 поступает в блок 1 (фиг. 4). В блоке 1 этот потенциал, пройдя через элементы ИЛИ 51 и 59, откроет элементы И 49 и 54 соответственно для прохождения импульса генератора 48 CQ по цепи: выход генератора 48 - элемент И 49 - элемент ИЛИ 50 - элемент И 54 (фиг. 7, Д и Т).

Таким образом осуществляется переход на считывание следующей тестовой операции. Заметим, что первой тестовой операцией для дискретной аппаратуры 5 с внутренними элементами памяти (триггерами, регистрами, сумма55

ности в виде несовпадений выходных реакций на одном или нескольких выходных контактах с их эталонными значениями.

В случае несовпадения выходной реакции ДА 5 с ее эталонными значениями (фиг. 5) на выходах соответствующих элементов 67 сравнения появляется высокий логический уровень, который, пройдя через элемент ИЛИ 69 поступает на вход блока 1. Это несовпадение может произойти как при завершении.какой-либо тестовой операций, так и во время ее выполнения (на каком-нибудь из ее элементарных шагов проверки).

Блок 1 (фиг. 4), принимая сигнал несовпадения от блока 2, вырабатывает формирователем 60 одиночный импульс, который через открытый элемент И 61 устанавливает триггер 62 в единичное состояние и, следовательно, способствует появлению на его прямом выходе высокого логического потенци

10

15

53978314

торами, счетчиками и т.п.) может быть операция установки ДА 5 в исход - ное состояние. Последующими тестовыми операциями могут быть инструкции, состоящие из определенного количества тестовых наборов, регламентирующие выполнение дискретной аппаратурой 5 определенных логических, либо арифметических функций, например сложить, записать, выдать на печать, переслать и т.п. Полный набор тестовых операций должен покрывать совокупность всего набора функций, выполняемых дискретной аппаратурой 5, обеспечивая тем самым необходимую полноту контроля его работоспособности.

При исправной дискретной аппаратуре этот набор тестовых операций- будет завершен без единого несовпадения выходных реакций ДА 5 с их эталонными значениями.

При наличии неисправности в ДА 5 она проявится на одной из тестовых операций в виде несовпадения выходной (ых) реакции (ий) с ее (их) эталонным (ми) значением (ями).

Определение неисправного (ых) блока (ов) дискретной аппаратуры 5 устройство проводит на существенной тестовой операции. Под существенной тестовой операцией в данном случае понимается тестовая операция, на ко20

25

30

0

5 Q

5

ности в виде несовпадений выходных реакций на одном или нескольких выходных контактах с их эталонными значениями.

В случае несовпадения выходной реакции ДА 5 с ее эталонными значениями (фиг. 5) на выходах соответствующих элементов 67 сравнения появляется высокий логический уровень, который, пройдя через элемент ИЛИ 69, поступает на вход блока 1. Это несовпадение может произойти как при завершении.какой-либо тестовой операций, так и во время ее выполнения (на каком-нибудь из ее элементарных шагов проверки).

Блок 1 (фиг. 4), принимая сигнал несовпадения от блока 2, вырабатывает формирователем 60 одиночный импульс, который через открытый элемент И 61 устанавливает триггер 62 в единичное состояние и, следовательно, способствует появлению на его прямом выходе высокого логического потенциала

151

, сигнализирующего о необходимости начать процесс замены записанной в триггерах 25 и 33 формирователя 6 последовательности блоков 5.1 (,Q) на эталонные блоки 9.j (j 1,Q) замены. Кроме того, с выхода элемента И 61 импульс поступает на элемент ИЛИ 58 и на выход элемента И ,61 блока 1. В результате этого в счетчике 12 (фиг. 2) под воздействием сигнала от элемента ИЛИ 58 устанавливается код начального адреса тестовой операции из регистра 15, т.е. производится возврат к началу выполнения этой существенной тестовой операции, а сигнал о необходимости проведения замены по шине (фиг.8, Р) поступает в узел 6 управления коммутатором, где проходит через линию 29 задержки (фиг. 3), элементы И 34.1- 34.N, ИЛИ 37.1-37.N и проводит тем самым подключение всего рекомендуемого набора эталонных блоков 9, работоспособность которых проверялась в ДА 5 при выполнении именно этой тестовой операции. Информация о последовательности подключения и отключения эталонных блоков 9 хранится в триггерах 25.1-25.N и 33.1-33.N узла 6 управления коммутатором.

В формирователе потенциал с шины триггера 62, кроме выработки разрешающего потенциала подключения рекомендуемого набора эталонных блоков в разрядах, где были установлены в 1м триггеры 25.1-25.N и 33.1-33.N, поступает на входы элементов И 27 и 30, открывая их для последующего прохождения импульсных сигналов Неисправность ДА с элемента И 61 и Исправность ДА с элемента И 63. Далее начинается повторение контроля дискретной аппаратуры с подключенным набором эталонных блоков 9 с изна- чального тестового набора существенной тестовой операции, так как счетчик 12 адреса (фиг. 2) накопителя 4 тестов принял значение, равное содержимому регистра 15 начального адреса операции, а импульс считывания информации по этому адресу на выходе элемента ИЛИ 50 появится с выхода формирователя 53 одиночного импульса (фиг. 4), который задерживается по времени от импульса на выходе формирователя 60 на время установки счетчика 12 адреса начального тестового набора тестовой операции, т.е. с ко

дов 00. В блоке 1 это обеспечивается задержкой появления управляющего сигнала на входе формирователя 53 временем срабатывания линии 56 за- держки, элемента ИЛИ 57 и самого формирователя 53 с элементом ИЛИ 50. За это время задержки обеспечивается подключение к ДА 5 заданного набора

эталонных блоков 9 вместо его штатных блоков 5. Подключение осуществляется коммутатором 7 по управляющим сигналам формирователя 6, так как высокий потенциал на шине триггера 62

открывает элементы И 34.1-34.N

(фиг. 3). Поэтому на выходах формирователя 6 через элементы И 34 и ИЛИ 37 появляются высокие потенциалы в тех разрядах, в которых были установлены в единичное состояние триггеры 25 и 33. Так как импульс на выходе элемента И 61 появляется раньше, чем на триггере 62 (фиг. 8, П и Р) на время срабатывания триггера 62

(фиг. 4) и линии 29 задержки (фиг.З), то в формирователе 6 он не пройдет через элементы И 27 и 30. Следовательно, в начале локализации неисправных блоков 5.1 произойдет подключение к ДА 5 всего рекомендованного набора эталонных блоков 9.J.

Коммутатор 7 (фиг. 6) осуществляет подключение эталонных блоков 9.1- 9.Q следующим образом. При нулевом уровне управляющего сигнала на соответствующем входе коммутатора 7 к ДА 5 через элементы НЕ 72, И 70 и 71 подключены ее функциональные блоки 5.1-5.Q,- т.е. ДА 5 функционирует

на штатных блоках, входящих в его состав. При единичном потенциале на соответствующих входах коммутатора 7 к ДА 5 через элементы И 74 и 73 подключаются соответствующие эталонные блоки 9.J замены и отключаются соответствующие им блоки 5.1. Элементы И 70-74 выполнены с открытым коллекторным выходом, что при закрытом состоянии обеспечивает исключение влияния сигналов с их выходов на последующие элементы схемы устройства и ДА 5 (эффект физического обрыва цепи).

Определение (локализация) неисправных блоков в ДА 5 производится последовательным отключением эталонных блоков 9 замены из рекомендованной последовательности, которая была

зарегистрирована в триггерах 25 и 33 формирователя 6.

Итак, первый цикл локалиеации неисправных блоков 5.1-5.Q в ДА 5 начинается с начального адреса существенной тестовой операции при подключенной рекомендованной последовательности эталонных блоков 9.1-9.Q замены. Этот цикл необходим для выявления возможных контактных замыканий или обрывов в монтажных соединениях между блоками 5.1-5.Q в ДА 5. Наличие контактных замыканий или обрыва в монтажных соединениях фиксируется уст- ройством путем совпадения содержимого триггеров 25 и 36, т.е. отключение любого из рекомендованной последовательности эталонного блока 9.J приводит к несовпадению выходных реакций ДА 5 с их эталонными значениями.

При успешном завершении первого цикла локализации (существенная опегт рация выполнена без несовпадений) формирователь 6 производит отключе- ние первого по номеру из рекомендованной последовательности эталонного блока 9 замены. Это производится следующим образом. Проверка ДА 5 на

тестовых наборах с признаками 01

и 10 вплоть до признака 11 производится в той же последовательности, что и при контроле ДА 5 до обнаружения в ней признака неисправности. При успешном выполнении 1-го тестово го набора с признаком 11 высокий п ртенциал с выхода дешифратора 23 накопителя 4 тестов поступает в блок 1. В результате этого в блоке 1 вырабатываются импульс Исправность ДА (фиг. 8, С) с выхода формирователя 64 через открытый элемент И 63, импульс Установить счетчик адреса 12 в А0 с выхода элемейта И 63 через элемент ИЛИ 58, синхроимпульс считьюания по следующим подготовленным цепям: дешифратор 23 - элемент ИЛИ 51 - элемент 52 задержки - вход элемента И 49 и дешифратор 23 - элемент ИЛИ 5 - вход элемента И 54. Следовательно, с выхода генератора 48 импульсов он проходит через элементы И 49 и ИЛИ 50. Кроме того, в блоке 1 вырабатывается импульс разрешения записи тестового набора с вы- хода элемента ИЛИ 50 через элемент И 54.

Импульс Исправность ДА, поступа с элемента К 63 в формирователь,

5 0

5

0

5 0 5 0 5

проходит через элементы ИЛИ 26, И 27 (фиг. 3), линию 28 задержки и элемент ИЛИ 32.1 на вход сброса триггера 33.1 (если в рекомендованной последовательности замены блоков 5 на эталонные блоки 9 первым по порядку номеров был блок 9.1), или с выхода линии 28 задержки через элементы И 31.1, ИЛИ 32.2 на R-вход триггера 33.2 и т.д. до триггера 33.j, который будет определен в рекомендованной последовательности как первый по порядку номеров. В результате этого . соответствующий триггер 33 будет установлен в нулевое состояние, отключая при этом первый из рекомендованной последовательности эталонный блок 9.J замены. Отключение производится закрытием соответствующего элемента И 34 с прямого выхода одноименного ему триггера 33. Высокий потенциал с инверсного выхода этого триггера 33 открывает последующие элементы И 31.j, 31.j+l,...,31.Q, a также элемент И 35.j.

Импульс Установить счетчик адреса 12 в А0, поступая в накопитель

4тестов, производит установку счетчика 12 адреса (фиг. 2) в состояние, равное содержимому регистра 15, т.е. осуществляет повторный возврат на начало этой же существенной11 тестовой операции.

Синхроимпульс считывания появляется с задержкой, обеспечивая считывание в регистр 65 теста блока 2 контроля информации с А0, т.е. начиная опять контроль ДА 5 на существенной тестовой операции при отключенном первом по порядку номеров из рекомендованной последовательности замены эталонными блоками 9.J замены. В дальнейшем локализация неисправных блоков 5.1 осуществляется таким же образом, что и при первом цикле локализации. При завершении локализации неисправных блоков в ДА

5возможны два результата: тестовая операция завершилась без проявления неисправности в виде и неисправность ДА 5 проявляется при отключении какого-либо из рекомендуемых эталонных блоков 9 замены.

При первом результате производится автоматическое отключение второго по порядку номеров блока 9.J аналогичным образом, что и отключение первого эталонного блока, а при втором

19

результате - импульсом с выхода элемента И 61 (фиг. 8, П) через открытый элемент И 35, В единичное состояние будет установлен соответствующий триггер 36.j, что приведет к обратному подключению одноименного эталонного блока 9,j к ДА 5 и к регистрации в триггере 36.j неисправности соответствующего ему функционального JQ блока 5.1 из состава ДА 5.

В дальнейшем локализация неисправных блоков 5.1-5.Q производится аналогично. При этом путем последовательного исключения из рекомендованной последовательности эталонных блоков 9.J замены определяется набор неисправных функциональных блоков из 5.1-5.Q, информация о которых запоминается в соответствующих триггерах 36,1-36.N формирователя 6 и отображается блоком 8 индикации. Окончание процесса локализации неисправных блоков сопровождается появлением высокого потеяциала на выходе элемента 25 И 31.j (фиг. 3), который в блоке 1 (фиг. 4) через элемент ИЛИ 43 и линию 44 задержки устанавливает в нуле- во.е состояние триггер 41 (фиг. 8,Б).

щей временные параметры их появления позволяет проводить контроль в темпе реального функционирования ДА 5, а также исключает возможность подачи запрещенных тестовых воздействий, чт повышает достоверность результата проводимого контроля.

15

20

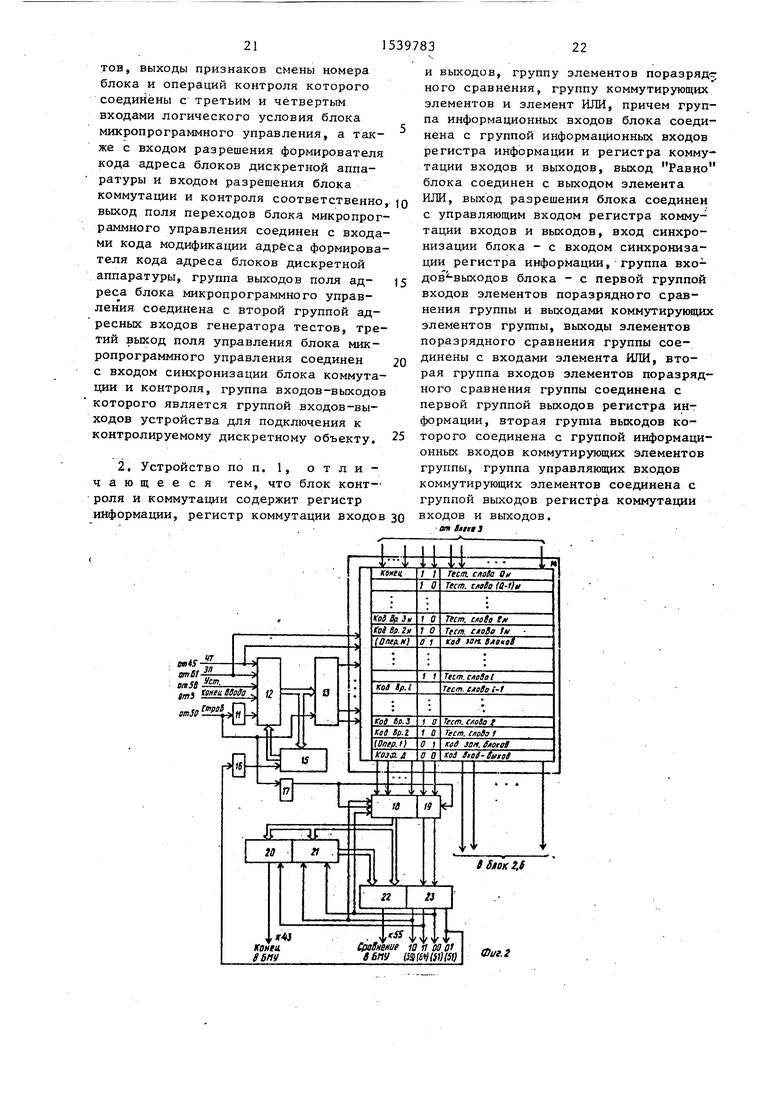

Формула изобретения

Переводом переключателя 10 режимов 30 микропрограммного управления соедивизуального контроля из положения Неисправные.блоки в положение Рекомендуемая последовательность визуально устанавливается причина отказа в ДА 5. Если содержимое триггеров 25.1-25.N равно содержимому триггеров 36.1-36.N, то неисправность находится в монтажных соединениях между блоками 5.1-5.Q ДА 5, а если содержимое регистра 25 превышает содержимое триггера 36, то необходимо провести замену блоков 5 на заведомо исправные идентичные блоки.

Неисправные блоки ДА 5 заменяются на исправные и контроль повторяется нажатием кнопки Пуск 40 блока 1. При повторном контроле не исключена возможность выявления других неисправных блоков. Они локализуются таким же образом, что и на первой существенной тестовой операции.

Таким образом, устройство обеспечивает локализацию неисправных блоков путем повторения существенной тестовой операции что.значительно снижает общее время контроля работоспособности ДА 5.

Кроме того, использование накопителя тестов с информацией, содержа

щей временные параметры их появления, позволяет проводить контроль в темпе реального функционирования ДА 5, а также исключает возможность подачи запрещенных тестовых воздействий, что повышает достоверность результата проводимого контроля.

Формула изобретения

5

0

5

0

5

нен с входом синхронизации генератора тестов, отличающееся тем, что, с целью повышения достоверности контроля, устройство дополнительно содержит формирователь кода адреса блоков дискретной аппаратуры и блок коммутации и контроля, причем группа выходов генератора тестов поля коммутаций соединена с группой информационных входов блока коммутации и контроля и с группой информационных входов формирователя кода адреса блоков дискретной аппаратуры, первая группа выходов которого соединена с группой управляющих входов коммутатора, вторая группа выходов формирователя кодов адреса соединена с первой группой адресных входов генератора тестов, выход Равно блока коммутации и контроля соединен с первым входом логического условия блока микропрограммного управления, второй вход логического условия которого соединен с выходом формирователя кода адреса блоков дискретной аппаратуры, группа входов логического условия блока микропрограммного управления соединена с группой выходов поля условий генератора тес-

тов, выходы признаков смены номера блока и операций контроля которого соединены с третьим и четвертым входами логического условия блока микропрограммного управления, а также с входом разрешения формирователя кода адреса блоков дискретной аппаратуры и входом разрешения блока коммутации и контроля соответственно, выход поля переходов блока микропрограммного управления соединен с входами кода модификации адреса формирователя кода адреса блоков дискретной аппаратуры, группа выходов поля ад- реса блока микропрограммного управления соединена с второй группой адресных входов генератора тестов, третий выход поля управления блока микропрограммного управления соединен с входом синхронизации блока коммутации и контроля, группа входов-выходов которого является группой входов-выходов устройства для подключения к контролируемому дискретному объекту.

и выходов, группу элементов поразряд-г ного сравнения, группу коммутирующих элементов и элемент ИЛИ, причем группа информационных входов блока соединена с группой информационных входов регистра информации и регистра коммутации входов и выходов, выход Равно блока соединен с выходом элемента ИЛИ, выход разрешения блока соединен с управляющим входом регистра коммутации входов и выходов, вход синхронизации блока - с входом синхронизации регистра информации, группа вхо- дов -выходов блока - с первой группой входов элементов поразрядного сравнения группы и выходами коммутирующих элементов группы, выходы элементов поразрядного сравнения группы соединены с входами элемента ИЛИ, вторая группа входов элементов поразрядного сравнения группы соединена с первой группой выходов регистра информации, вторая группа выходов которого соединена с группой информационных входов коммутирующих элементов группы, группа управляющих входов коммутирующих элементов соединена с группой выходов регистра коммутации входов и выходов.

от 1ччЗ

«3 5

i

к

Ǥ

Ve

J

СЧ

V;

t

I

Ǥ -,

I

I

e

00

Л

mlu

ФвгЛ От накопителя 4 тестов

1539783

(fffa.lW) ъ 311

МАЯ

Фиг. 5

Фиг. 6

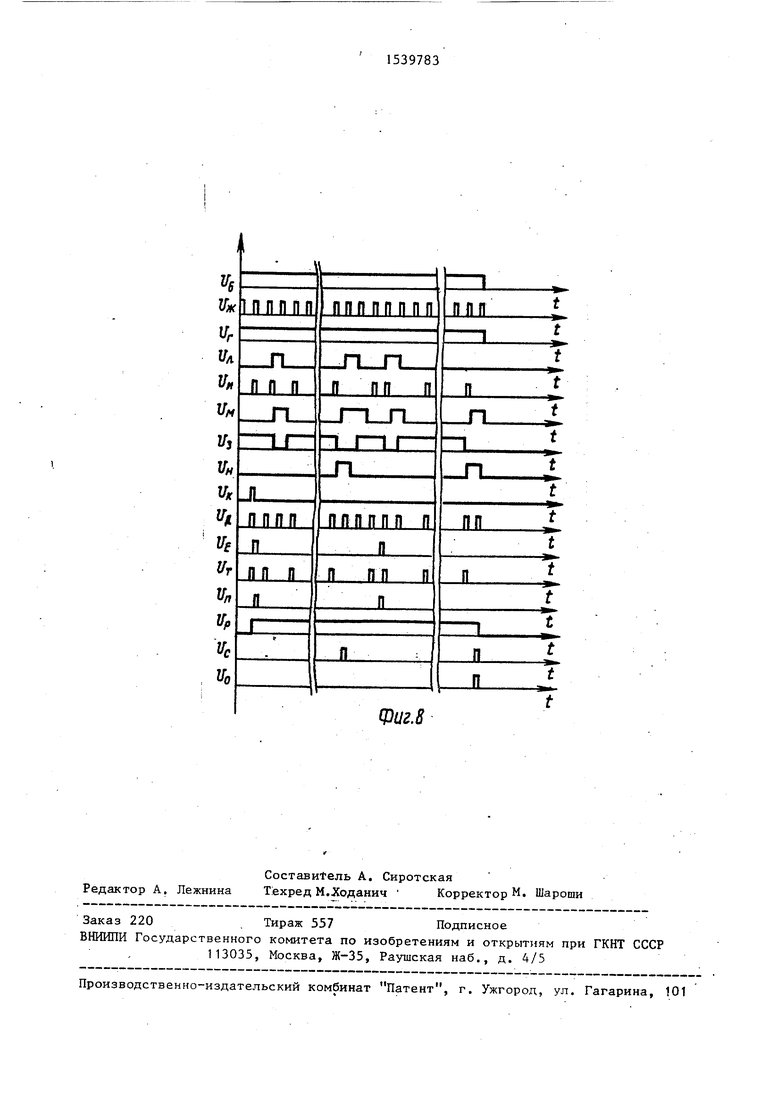

Фиг.8

| Патент США № 3614608, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1987-11-06—Подача