1

Изобретение относится к вычислительной технике.

Известно запоминающее устройство, состоящее из адресного накопителя, адресных цепей, разрядных цепей, регистра слова, блока местного управления, кодирующего и декодирующих устройств и регистра мощности корректирующего кода.

При отказе одной или нескольких ячеек в, таком запоминающем устройстве не требуется ремонт адресного накопителя, останов мащины либо коррекция стандартных подпрограмм. Ошибки исправляются за счет использования регистра мощности корректирующего кода, который управляет работой устройств кодирования и декодирования в зависимости от наихудшего, максимального количества отказов в одной ячейке накопителя. Однако применение известного устройства не эффективно в случае, например, наличия некоторого количества отказов в одной ячейке накопителя и отсутствия отказов во всех остальных, т. е. при неравномерном распределении количества отказов. Вследствие этого снижается эффективность цифровой вычислительной машины (ЦВМ) из-за нерационально использованного технического ресурса оборудования устройства памяти.

Цель изобретения - создание запоминающего устройства с переменной мощностью

корректирующего кода для различных областей (секторов, страниц) памяти, позволяющего наиболее гибкой полно использовать технический ресурс оборудования, повысить эффективность устройства памяти, а значит и всей ЦВМ.

Это достигается тем, что в устройство памяти введены регистры мощности корректирующего кода, схемы «И и дещифратор регистров мощности корректирующего кода, вход которого соединен с выходом регистра адреса старших разрядов, а выход - с входами схем «И и с входами регистров мощности корректирующего кода. Другие входы схем «И связаны с блоком местного управления, а выход каждой схемы «И - с соответствующим регистром мощности корректирующего кода, причем выходы регистров мощности корректирующего кода соединены с управляющими

входами кодирующего и декодирующего блоков.

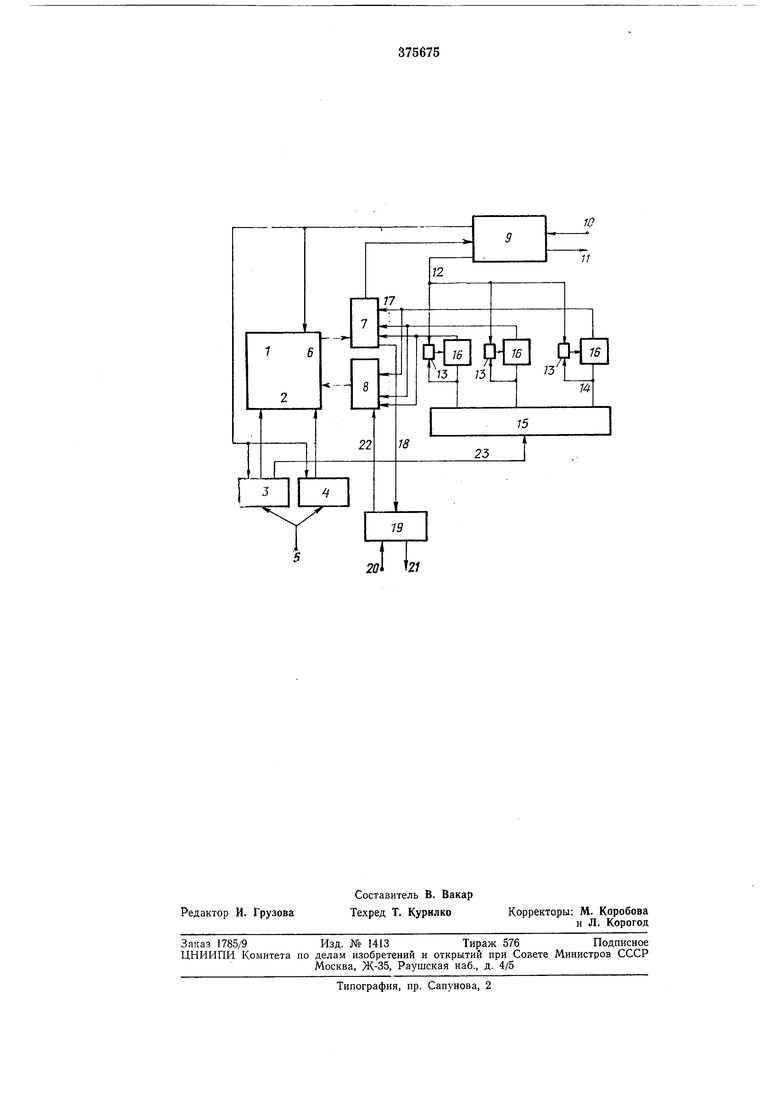

На чертеже показана блок-схема предлагаемого запоминающего устройства. Запоминающее устройство содержит накопитель /, дешифратор 2 адреса, входы которого связаны с регистром адреса, условно разбитого на регистры старших разрядов 3 и младших разрядов 4, имеющие адресный вход 5. Разрядные цепи 5 накопителя / соединены

с информационным входом блока 7 декодирования и с информационным выходом блока S кодирования, управляющий выход блока декодирования -- с блоком 9 местного управления, имеющим вход 10 и выход 11. Управляющий выход блока местного управления подключен к регистрам 5 и 4 адреса накопителя / и его разрядными цепями 6, а через цепь 12 выходы блока местного управления подсоединены к входам схем 13 совпадения. Второй вход этих схем через цепь 14 соединен с дещифратором 15 регистров мощности корректирующего кода (МКК), а выходы схем - с входами регистров 16 МКК, выполненными в виде счетчика. Соответствующий i-й выход дещифратора 15 регистров МКК через цепь 14 связан с щиной считывания г-го регистра 16 МКК, выходы регистров 16 через цепь 17 - с управляющими входами блока 7 декодирования. Информационный выход блока декодирования через цепь 18 подключен к регистру 19 слова, имеющему информационный вход 20 и выход 21. Регистр слова соединен через цепь 22 с информационным входом блока 8 кодирования, вход дещифратора 15 регистров ДЧМК через цепь 23 - с выходом регистра 3 старших разрядов адреса. Устройство памяти работает следующим образом. Пусть необходимо обратиться к i-й ячейке накопителя, имеющей т отказов. В этом случае на дещифратор 2 адреса поступает код числа L Одновременно с этим на дешифратор регистра МКК подается код числа k, где tl - адрес, образованный старшими разрядами полного адреса i в регистре 3. Слово, находящееся в tl-M регистре МКК, определяет величину мощности корректирующего кода, в данном случае, равную (m+I). Таким образом, при наличии в ячейке АН 1 т отказов используется корректирующий код который может исправлять (/п+1) ошибку. Величина корректирующей способности кода с tl-ro регистра МКК через цепь 17 управляет работой блоков декодирования и кодирования так, чтобы они могли кодировать и декодировать слово, которое считывается ими, записывается в ячейку АН I с (т+1) отказом. Если в ячейке АН I не т отказов, а (т+1), то информация не теряется, но при этом блок декодирования выдает в блок местного управления сигнал с предельно использованной мощности корректирующего кода, т. е. имеется (т+1) отказ и блок декодирования исправляет (т+1) ошибку. По этому сигналу из блока местного управления через цепь/2 выдается на схему 13 сигнал «+1, который поступает на выбранный ti-й регистр МКК и суммируется с его содержимым. Вследствие этого величина МКК для данной й-й области (страницы, сектора) ячеек АН I возрастает и становится равной (т+2). После этого содержимое Il области АН I перезаписывается в АН I для МКК (/п+2) через блок декодирования, цепь 18, регистр слова, цепь 22 и блок декодирования. Если число отказов в i блока ячеек АН I между двумя последовательными обращениями изменилось не на единицу, а, например, на К (что менее вероятно), то при чтении блок декодирования выдает в блок местного управления сигнал о повыщении данной МКК. Блок местного управления с выхода 11 подает в управляющее устройство ЦВМ сигнал о том, что информация по адресу, находящемуся в регистрах 3 и 4, потеряна, Одновременно блок местного управления через цепи 12 и схему 13 выдает сигнал «+1 в данный регистр МКК, который суммируется с содержимым регистра МКК. Вновь записанное слово поступает на вход 20 регистра слова через цепь 22 и блок кодирования. Если при чтении снова блок кодирования выдает сигнал о превыщении МКК, описанный выще, цикл повторяется. Таким образом, предлагаемое устройство памяти позволяет рационально использовать технический ресурс оборудования, т. е. адаптироваться к имеющей место ситуации. Предмет изобретения Запоминающее устройство, содержащее блок местного управления, выходы которого соединены с разрядными цепями накопителя и с регистром адреса младщих и старших разрядов, выходы которого через дешифратор адреса соединены с накопителем, выход которого подключен к входу декодирующего блока, выход которого соединен с блоком местного управления и с входом регистра слова, выход которого соединен с входом блока кодирования, подключенного своим выходом к разрядным цепям накопителя, отличающееся тем, что, с целью рационального использования технического ресурса оборудования в случае неравномерного распределения отказов в устройстве, в него введены регистры мощности корректирующего кода, схемы «И и дешифратор регистров мощности корректирующего кода, вход которого соединен с выходом регистра адреса, старших разрядов, а выход - с входами регистров мощности корректирующего кода и с входами схем «И, другие входы схем «И соединены с блоком местного управления, а выход каждой схемы «И связан с соответствующим регистром мощности корректирующего кода, причем выходы регистров мощности корректирующего кода соединены с управляющими входами кодирующего и декодирующего блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 1971 |

|

SU429424A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство | 1975 |

|

SU560255A2 |

| Запоминающее устройство | 1975 |

|

SU529481A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО:1 Т 5•..:' 'Уу | 1973 |

|

SU436388A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU377873A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Запоминающее устройство | 1972 |

|

SU448480A1 |

Авторы

Даты

1973-01-01—Публикация