СП СП

СП

со

о

ГчЭ

Изобретение относится к радиотехнике, в частности к радиосистемам передачи информации, может использоваться для совершенствования широкого класса цифровых систем передачи дискретных сообщений, представленных в виде сверточных кодов, и является усовершенствованием изобретения по авт.св.К 1262744.

Цель изобретения - повышение достоверности приема сигналов путем повышения надежности сигнальной синхронизации в фазовом подканале.

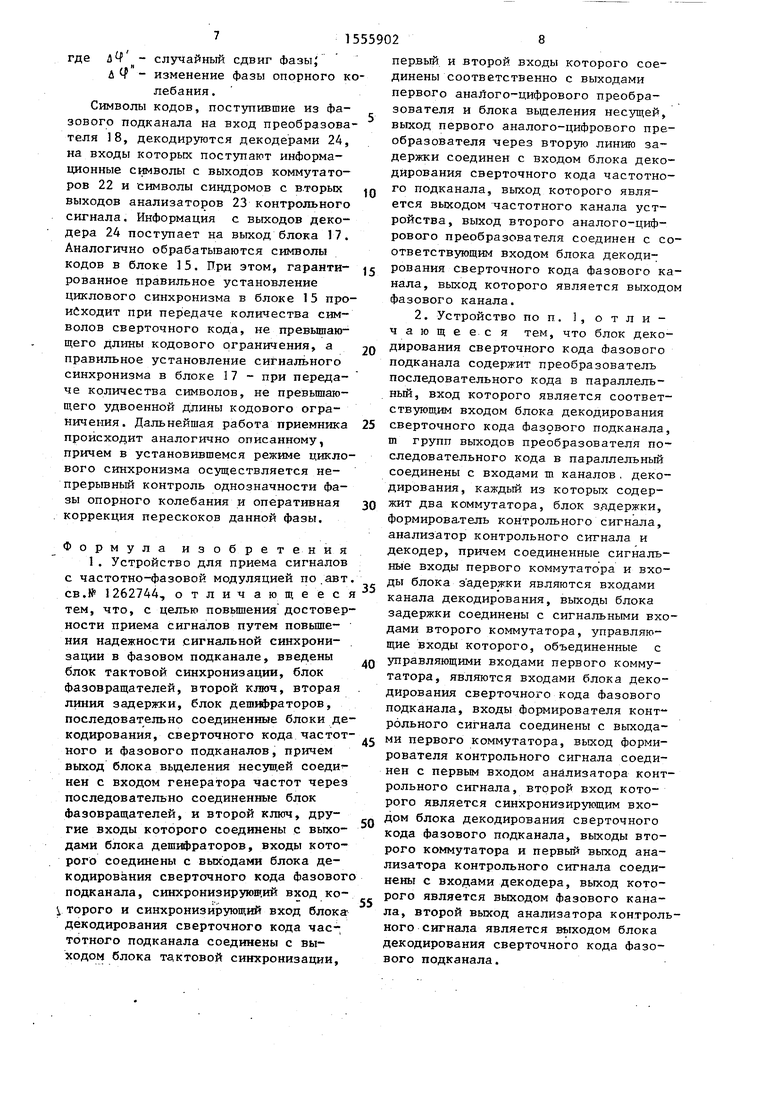

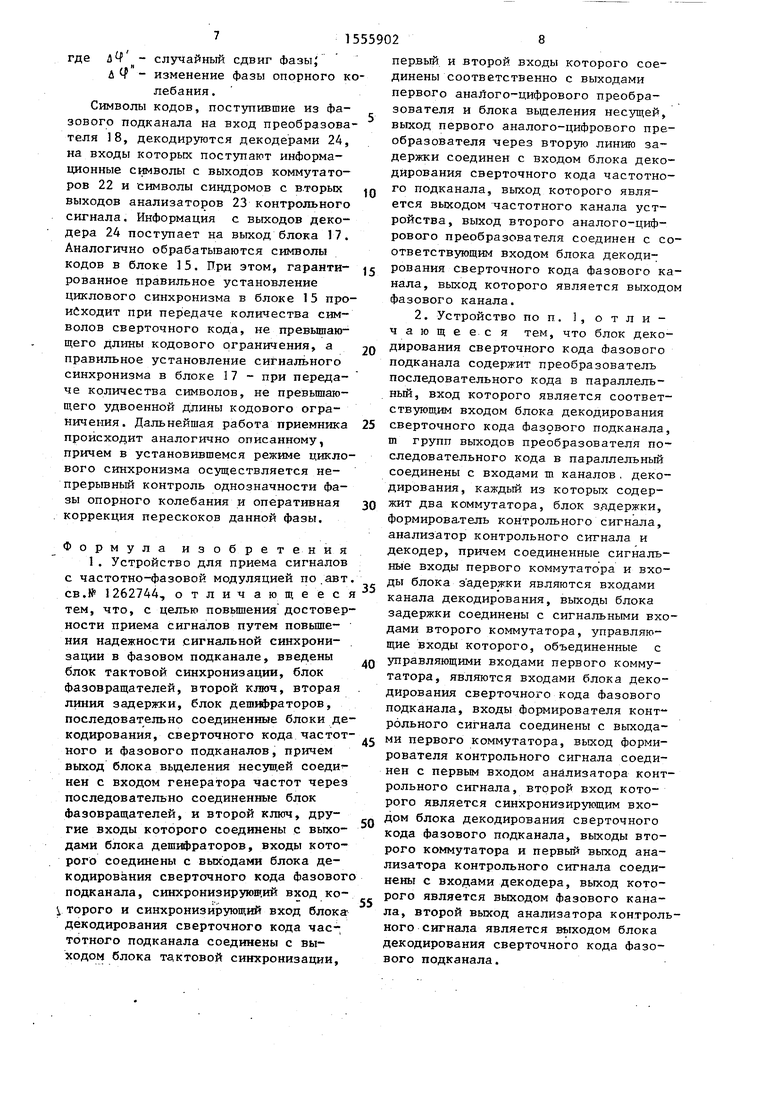

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг.2 - схема блока декодирования сверточного кода фазового подканала.

Устройство содержит частотный це- тектор 1 , первую линию задержки, первый интегратор 3, блок 4 выделения несущей, фазовый детектор 5, первый аналого-цифровой преобразователь (АЦП) 6, блок 7 тактовой синхрониза- ции,блок 8 фэзоврапгателей,второй интегратор 9, в торой ключ 1 0, второй AUIJ 1 1, генератор 12 частот, первый ключ 13, вторую линию 14 задержки, блок 15 декодирования сверточного кода частотного подканала, блок 16 дешифратора, блок 17 декодирования сверточного кода фазового подканала, состоящий из преобразователя J 8 последовательного кода в параллельный, го каналов, каждый из которых состоит из первого коммутатора 19, блока 20 задержки, формирователя 21 контрольного сш- нала, второго коммутатора 22, анализатора 23 контрольного сигнала и декодера 24.

Устройство работает следующим образом.

На его вход поступает частотно-фа- зоманипулированный сигнал, который можно представить в виде

Asin(wut +JAW(t)dt +

S(t)

+ ДЧЧО +(O

амплитуда огибающей сигнала ;

50

55

круговая частота и начальная фаза несущего колебания;

закон изменения частоты несущего колебания

закон изменения фазы сигнала.

С входа приемника сигнал поступает на входы частотного дотектора 1 и первой линии 2 задержки. На выходе частотного детектора 1 формируется напряжение, которое является монотонной функцией величины отклонения значения частоты принимаемого элемента сигнала (т.е. сигнала, принимаемого за тактовый интервал времени) fc от частоты настройки частотного детектора 1 f :

ИА

i

5

0 5

0

5

0

5

0

5

.

Данное напряжение интегрируется за время такта первым интегратором 3, передаточная функция которого определяется выражением

Un yKA(t)dt,

о

где с/ - постоянная времени интегрирования .

Напряжение с выхода интегратора 3 поступает на вход АДП 6, который преобразует данное напряжение в последовательность двоичных символов (.код), соответствующую частоте принимаемого элемента сигнала. Данный код поступает на управляющие входы ключа 13 и через линию 14 задержки на вход блока 15.

Сигнал, задержанный линией 2 задержки на время, равное длительности обработки элемента сигнала в частотном подканале (.1 такт), поступает на вход блока 4, в котором производится выделение опорного колебания. Данное опорное колебание поступает на вход блока 8,который производит фазовый сдвиг данного колебания ft

п Л О /О 1 X

на 0 ii, 2т- t Um-1 ) -i Это опорное колебание поступает на первый вход блока 7, который по поступающему на его второй вход сигналу формирует из опорного колебания синхронизирующие импульсы с частотой, равной тактовой частоте формируемых АЦП 6 символов. Опорные колебания с указанными выше фазовыми сдвигами поступают на сигнальные входы ключа 13, который производит подключение

ОДНОГО ИЗ СВОИХ ВХОДОВ К ВЫХОДУ В

соответствии с управляющим сигналом. При этом в начальное время приема, пока не установлен сигнальный синхронизм, ключ 13 подключает к выходу свой первый вход, на который подается опорное колебание с нулевым сдвигом

515559026

Данное опорное колебание поступает анализаторов 23 контрольных сигналов на вход генератора 12 частот, который в блоке 15 и анализаторов 23 конт

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Устройство фазирования регенераторов цифрового сигнала | 1978 |

|

SU786036A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Демодулятор многочастотных сигналов с амплитудно-фазовой модуляцией | 1983 |

|

SU1117856A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение достоверности приема сигналов. Устройство для приема сигналов с частотно-фазовой модуляцией содержит частотный детектор 1, линии 2 и 14 задержки, интеграторы 3 и 9, блок 4 выделения несущей, фазовый детектор 5, АЦП 6 и 11, блок 7 тактовой синхронизации, блок 8 фазовращателей, ключи 10 и 13, г-р 12 частот, блок 15 декодирования сверточного кода частотного подканала, блок 16 дешифраторов и блок 17 декодирования сверточного кода фазового подканала. Цель достигается путем повышения надежности сигнальной синхронизации в фазовом подканале. Устройство по п. 2 ф-лы отличается выполнением блока 17 декодирования. 1 з.п. ф-лы, 2 ил.

формирует сетку опорных частот, поступающих на сигнальные входы ключа 13.. По управляющему сигналу с выхода АЦП 6, соответствующему частоте принятого элемента сигнала, ключ 13 пропускает на свой выход опорное колебание с частотой принятого элемента сигнала, поступающего на второй вход фазового детектора 5, на первый вход которого подается сигнал с выхода линии 2 задержки. На выходе фазового детектора 5 формируется напряжение, являющееся 15 монотонной функцией значения разности фаз принятого и опорного сигналов:

20

()Данное напряжение выделяется интегратором 9 и поступает на вход АЦП 6, который преобразует его в код, соответствующий фазе принятого сигнала.

Код из фазового подканала поступает на вход блока 17. Одновременно с 25 ним на вход блока 15 поступает код из частотного подканала, задержанный линией 14 задержки на время принятия решения в фазовом подканале (1 такт). Блок 15 производит установление цик- 30 левого синхронизма по выделению фазирующей последовательности, накладываемой при передаче на проверочные символы сверточного кода путем суммирования по модулю два. При установле- 35 нии циклового синхронизма коммутация входов декодера 24 устанавливается управляющими сигналами с первых выходов анализаторов 23 контрольных сигналов в соответствии с определенными данными анализаторами 23 контрольных сигналов в блок 15 положениями информационных и проверочного символов в кодовой комбинации принятого сверточного кода.

Эти управляющие сигналы с выходов анализаторов 23 контрольных сигналов (выходов блока 15) поступают на входы блока 17, устанавливая первые коммутаторы 19 и вторые коммутаторы 22 в положения, соответствующие установленной цикловой синхронизации в блок 15. При этом сверточные коды, поступающие на входы каналов декоди40

45

50

довательнос и в каждом из каналов декодирования производится аналогично данному выделению в блоке 15. При этом прием неискаженной Лавирующей последовательности соответствует появлению на первых выходах анализаторов 23 контрольного сигнала логической , а прием искаженной из-за случайного сдвига Фазы фазирующей последовательности - сигнала логического О. Дпя выбранного манипуля- ционного кода существз ет однозначное соответствие комбинаций одновременно принятых н непринятых в m каналах фазирующих последовательностей произошедшим случайным перескокам фазы опорного колебания которые кратны

Сигналы с первых выходов анализаторов 23 контрольного сигнала поступают на входы блока 16, который опознает вид комбинации единиц и нулей и выдает единичный сигнал на соответствующий управляющий вход коммутатора 19 для выбора определенного корректирующего фазового сдвига опорного колебания. К примеру, прием вместо переданной кодовой комбинации 101 комбинации 000 означает произошедший

лскачок Фазы опорного колебания на -,

при котором фазирующая последовательность правильно выделена только во втором канале декодирования, и блок 16 по поступившей на его входы комбинации OJ 0 выдает сигнал логической 3 на тот управляющий вход ключа 10, который подключает к его выходу опорное

рования с выходов преобразователя 18, 55 колебание со сдвигом на 3-, т.е.корреканалогичные кодам,поступающим в блок 15 (т.е. одинаковыми являются образующие полиномы данных кодов), и передаются синхронно с ними, а работа

тирующий сдвиг фазы удовлетворяет равенству

+ i 2,

5

0

5 0 5

рольных сигналов в блоке 17 синхронизируется тактовыми импульсами, поступающими с выхода блока 7. i

С установлением циклового синхронизма становится возможным правильное выделение фазирующей последовательности в каналах декодирования блока 17,. каждый из которых обрабатывает сверточный код, передаваемый по соответствующему крату фазовой манипуляции. Выделение фазирующей после /

довательнос и в каждом из каналов декодирования производится аналогично данному выделению в блоке 15. При этом прием неискаженной Лавирующей последовательности соответствует появлению на первых выходах анализаторов 23 контрольного сигнала логической , а прием искаженной из-за случайного сдвига Фазы фазирующей последовательности - сигнала логического О. Дпя выбранного манипуля- ционного кода существз ет однозначное соответствие комбинаций одновременно принятых н непринятых в m каналах фазирующих последовательностей произошедшим случайным перескокам фазы опорного колебания которые кратны

Сигналы с первых выходов анализаторов 23 контрольного сигнала поступают на входы блока 16, который опознает вид комбинации единиц и нулей и выдает единичный сигнал на соответствующий управляющий вход коммутатора 19 для выбора определенного корректирующего фазового сдвига опорного колебания. К примеру, прием вместо переданной кодовой комбинации 101 комбинации 000 означает произошедший

лскачок Фазы опорного колебания на -,

при котором фазирующая последовательность правильно выделена только во втором канале декодирования, и блок 16 по поступившей на его входы комби, нации OJ 0 выдает сигнал логической 3 | на тот управляющий вход ключа 10, который подключает к его выходу опорное

тирующий сдвиг фазы удовлетворяет равенству

+ i 2,

где

- случайный сдвиг фазы Д - изменение фазы опорного колебания.

Символы кодов, поступившие из фазового подканала на вход преобразователя 18, декодируются декодерами 24, на входы которых поступают информационные символы с выходов коммутаторов 22 и символы синдромов с вторых выходов анализаторов 23 контрольного сигнала, Информация с выходов декодера 24 поступает на выход блока 17. Аналогично обрабатываются символы кодов в блоке 15. При этом, гарантированное правильное установление циклового синхронизма в блоке 15 происходит при передаче количества символов сверточного кода, не превышающего длины кодового ограничения, а правильное установление сигнального синхронизма в блоке 17 - при передаче количества символов, не превышающего удвоенной длины кодового ограничения. Дальнейшая работа приемника происходит аналогично описанному, причем в установившемся режиме циклового синхронизма осуществляется непрерывный контроль однозначности фазы опорного колебания и оперативная коррекция перескоков данной фазы.

Формула изобретения 1. Устройство для приема сигналов с частотно-фазовой модуляцией по авт. св,№ 1262744, отличающееся тем, что, с целью повышения достоверности приема сигналов путем повышения надежности сигнальной синхронизации в фазовом подканале, введены блок тактовой синхронизации, блок фазовращателей, второй ключ, вторая линия задержки, блок дешифраторов, последовательно соединенные блоки де50

кодирования, сверточного кода частот- мн первого коммутатора, выход форми- ного и фазового подканалов, причем выход блока выделения несущей соединен с входом генератора частот через последовательно соединенные блок фазовращателей, и второй ключ, другие входы которого соединены с выходами блока дешифраторов, входы которого соединены с выходами блока декодирования сверточного кода фазового подканала, синхронизирующий вход ко- торого и синхронизирующий вход блока- декодирования сверточного кода частотного подканала соединены с выходом блока тактовой синхронизации,

55

рователя контрольного сигнала соединен с первым входом анализатора контрольного сигнала, второй вход которого является синхронизирующим входом блока декодирования сверточного кода фазового подканала, выходы второго коммутатора и первый выход анализатора контрольного сигнала соединены с входами декодера, выход которого является выходом фазового канала, второй выход анализатора контроль ного сигнала является выходом блока декодирования сверточного кода Фазового подканала.

0

5

0

5

0

первый и второй входы которого соединены соответственно с выходами первого аналого-цифрового преобразователя и блока выделения несущей, выход первого аналого-цифрового преобразователя через вторую линию задержки соединен с входом блока декодирования сверточного кода частотного подканала, выход которого является выходом частотного канала устройства, выход второго аналого-цифрового преобразователя соединен с соответствующим входом блока декодирования сверточного кода фазового канала, выход которого является выходом фазового канала.

мн первого коммутатора, выход форми-

рователя контрольного сигнала соединен с первым входом анализатора контрольного сигнала, второй вход которого является синхронизирующим входом блока декодирования сверточного кода фазового подканала, выходы второго коммутатора и первый выход анализатора контрольного сигнала соединены с входами декодера, выход которого является выходом фазового канала, второй выход анализатора контрольного сигнала является выходом блока декодирования сверточного кода Фазового подканала.

Отдл.15

Вш

ъЬКбл.16

Вых. Ъкб&1б

Выл.

ъЪК8л.16

От 5л. 7 Фиг. г

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1985 |

|

SU1262744A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-04-07—Публикация

1988-06-02—Подача