Изобретение относится к электросвязи.

Известны устройства для асинхронного ввода в цифровой тракт двоичной информации с двусторонним стаффингом, содержащие блок памяти, фазовый компаратор и формирователь команд.

Недостатком известных устройств является наличие низкочастотных фазовых флюктуации, входящих в полосу пропускания фильтра нижних частот в системе фазовой автоподстройки (ФАП).

Борьба с низкочастотными фазовыми флюктуациями сводится к уменьшению шага дискретизации за счет увеличения числа команд, что приводит к уменьшению допустимой расстройки частот и при заданном коэффициеите использования тракта значительно ухудшает достоверность приема команд.

Цель изобретения - уменьшение низкочастотных фазовых флюктуации. Достигается она тем, что в предлагаемом устройстве между фазовым компаратором и формирователем команд включен блок управления формирователем, содержащий последовательно соединенные дифференциальный детектор, вход которого соединен с выходом фазового компаратора, фильтр нижних частот и усилитель-ограничитель, выход которого соединен со входом формирователя команд, а также блок запрета активных команд, вход которого соединен со вторым выходом фазового компаратора, а выформирователя

входом

ход - со

вторым команд.

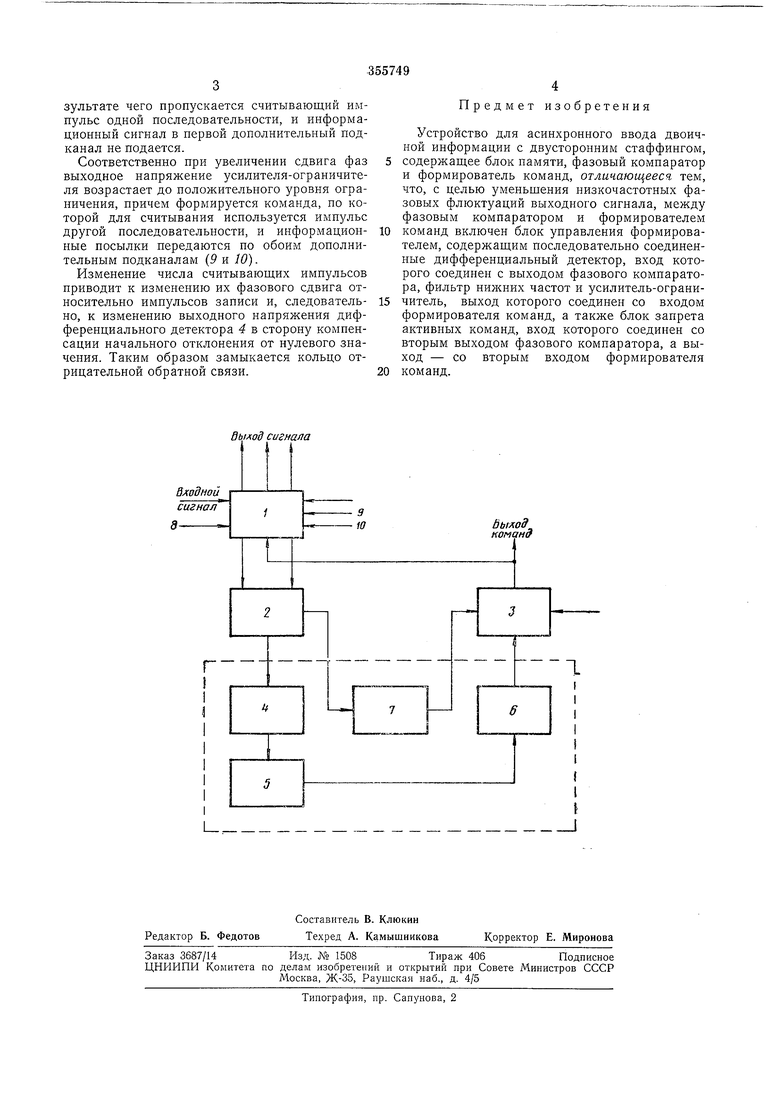

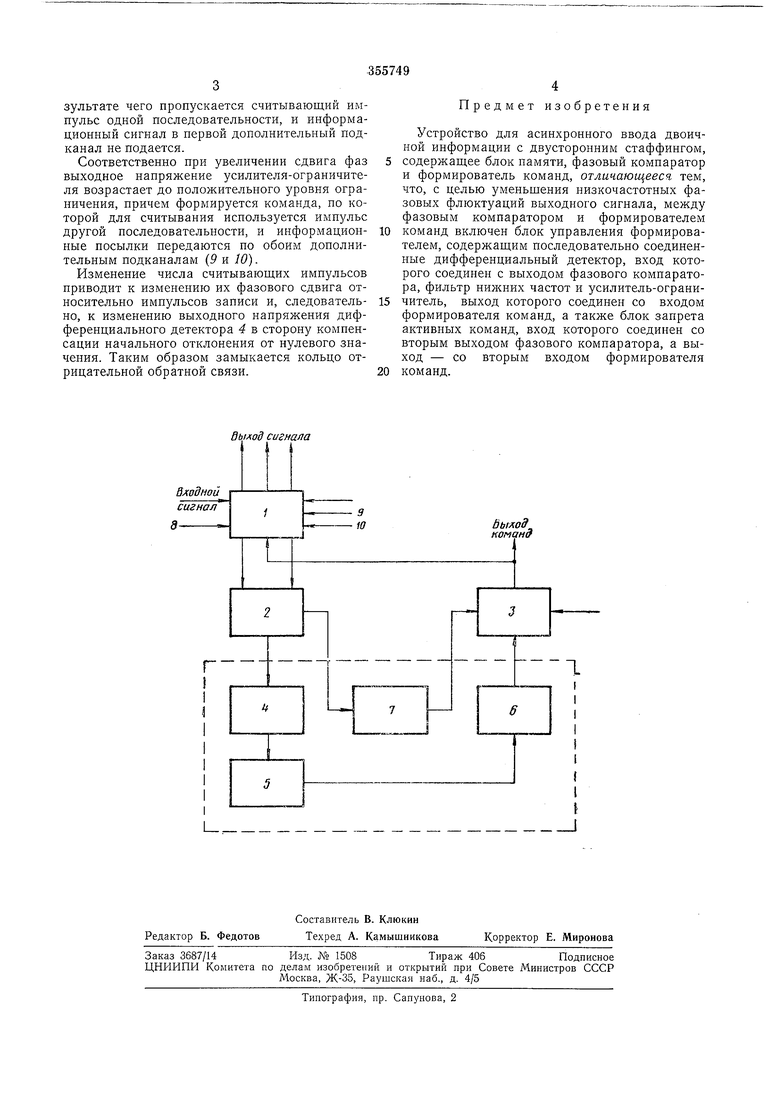

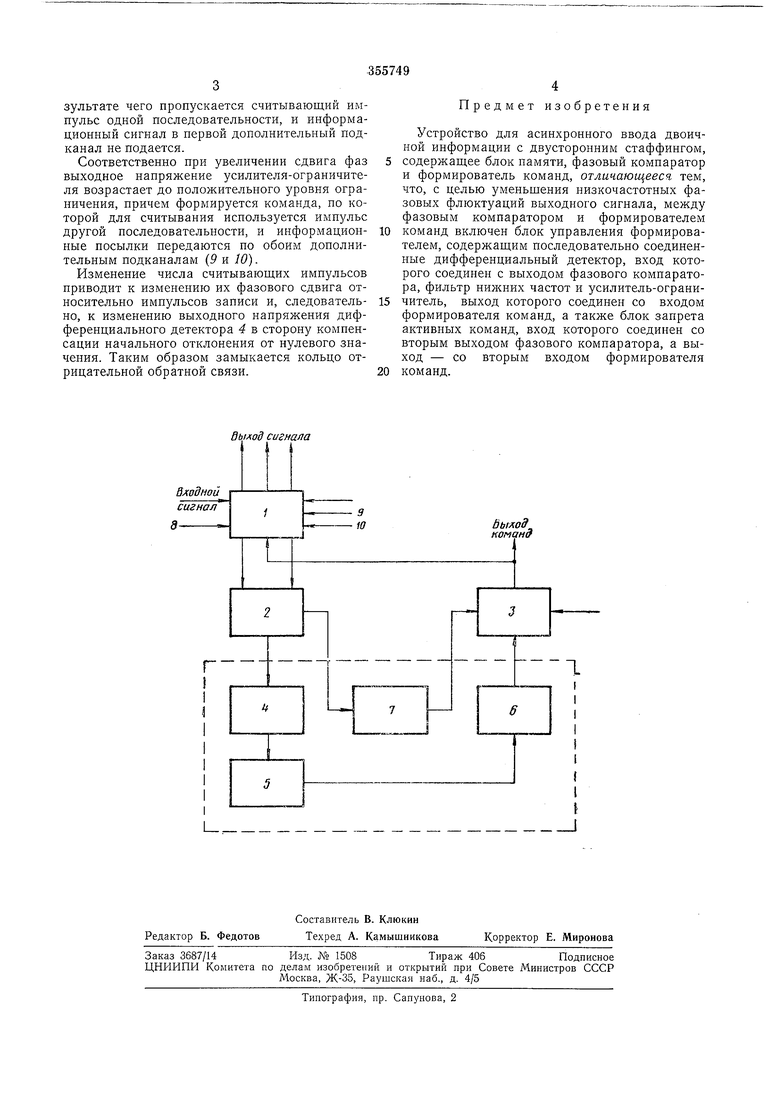

На чертеже показана блок-схема устройства для асинхронного ввода двоичной информации с двусторонним стаффингом.

В состав устройства для асинхронного ввода входят устройство для согласования фаз входного сигнала и импульсной несущей частоты (эластичная память 1), фазовый компаратор 2, следящий за запасом информации, записанной в ячейках намяти, и схема формирования команд 3. В отличие от известных устройств, в которых фазовый компаратор управляет схемой формирования комаид неносредственно, в данном устройстве это управление производится через дифференциальный детектор 4 с фильтром нижних частот 5 и усилитель-ограничитель 6, а также через схему запрета активных команд 7.

Схема работает следующим образом.

Когда сдвиг фазы импульсов записи и считывания имеет номииальное значение, выходное напряжение усилителя-ограничителя 6 близко к нулю. При этом формируется нейтральная команда, при которой сигнал передается как по основному каналу, так и по первому дополнительному нодканалу 9.

зультате чего пропускается считывающий импульс одной последовательности, и информационный сигнал в первой дополнительный подканал не подается.

Соответственно при увеличении сдвига фаз выходное напряжение усилителя-ограничителя возрастает до положительного уровня ограничения, причем формируется команда, по которой для считывания используется импульс другой последовательности, и информационные посылки передаются по обоим дополнительным подканалам (9 и 10).

Изменение числа считывающих импульсов приводит к изменению их фазового сдвига относительно импульсов записи и, следовательно, к изменению выходного напряжения дифференциального детектора 4 в сторону компенсации начального отклонения от нулевого значения. Таким образом замыкается кольцо отрицательной обратной связи.

Предмет изобретения

Устройство для асинхронного ввода двоичной информации с двусторонним стаффингом, содержащее блок памяти, фазовый компаратор и формирователь команд, отличающееся тем, что, с целью уменьщения низкочастотных фазовых флюктуации выходного сигнала, между фазовым компаратором и формирователем команд включен блок управления формирователем, содержащим последовательно соединенные дифференциальный детектор, вход которого соединен с выходом фазового компаратора, фильтр нижних частот и усилитель-ограничитель, выход которого соединен со входом формирователя команд, а также блок запрета активных команд, вход которого соединен со вторым выходом фазового компаратора, а выход - со вторым входом формирователя команд.

сигнала

||

ЬылоЗ команд

Даты

1972-01-01—Публикация