Изобретение относится к области вычислительной техники и может быть использовано, например, в устройствах ввода-вывода управляющих вычислительных машин.

Известны многоканальные устройства для вывода сигналов управления из вычислительной машины, содержаш,ие блок управления, подключенный к элементам памяти. Основным недостатком таких устройств является возможность выработки ложных сигналов управления в результате отказов, возникаюП1их при работе устройства, что может привести к нарушению всего процесса управления.

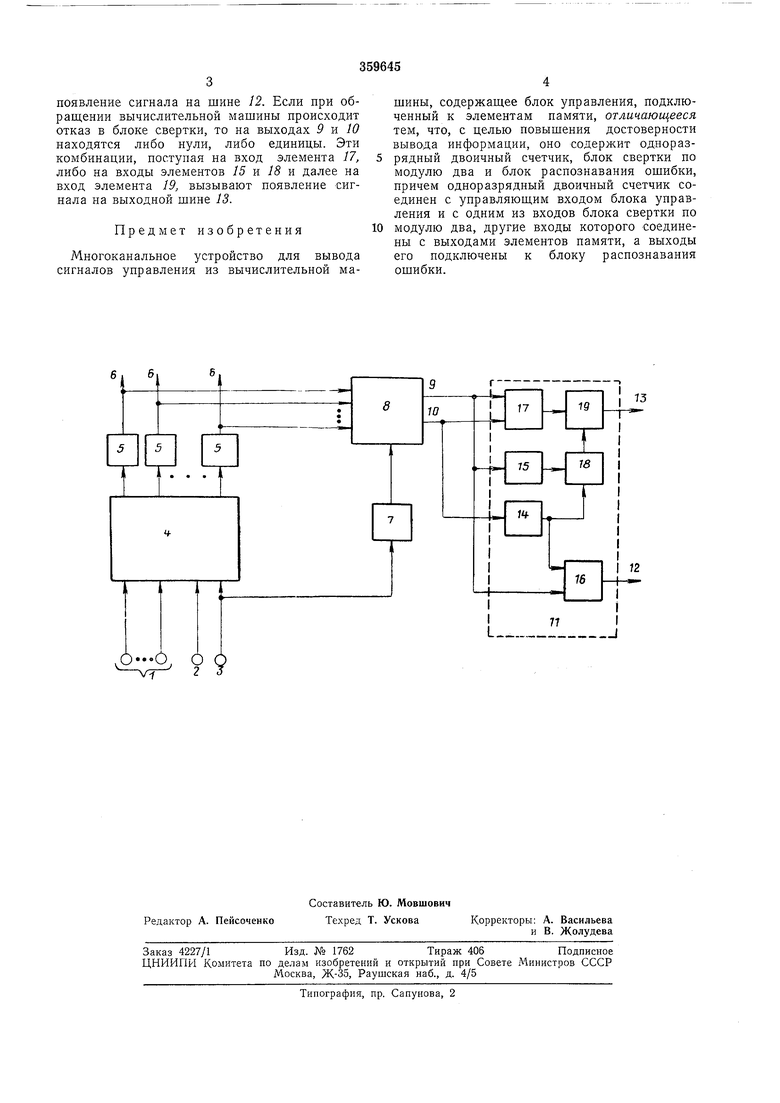

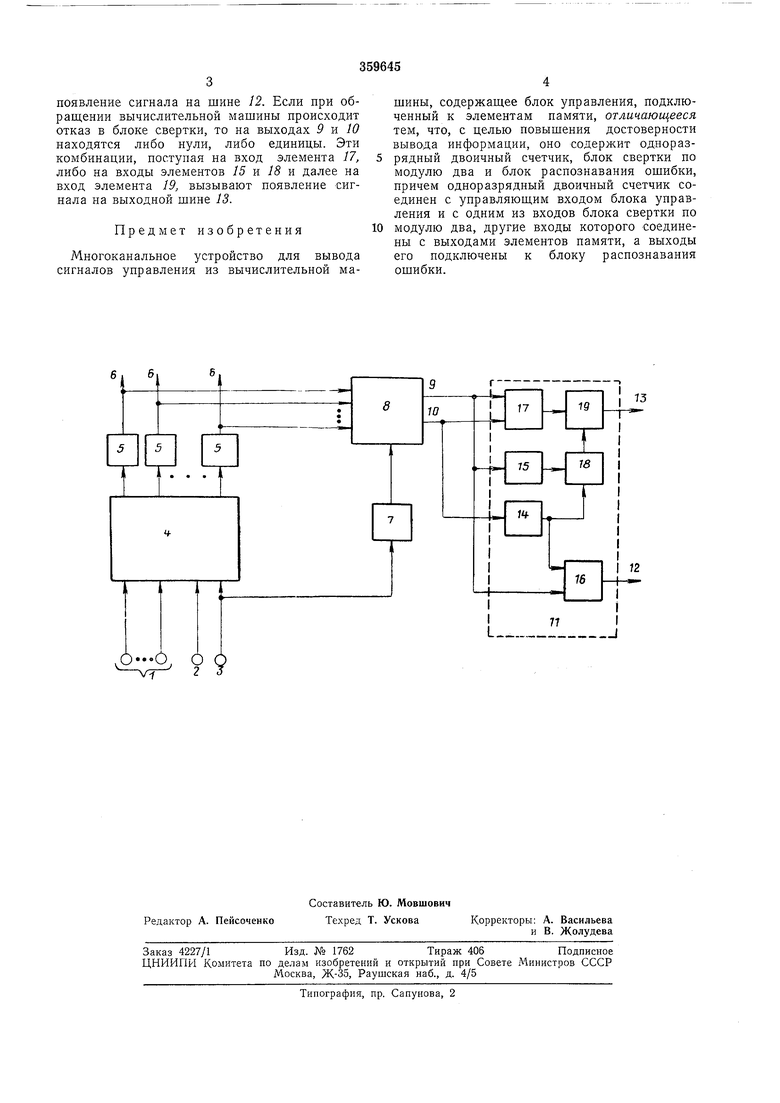

Цель изобретения - повышение достоверности вывода информации. Это достигается тем, что предлагаемое устройство содержит одноразрядный двоичный счетчик, блок свертки по модулю два и блок распознавания ошибки. Одноразрядный двоичный счетчик соединен с управляющим входом блока управления и с одним из входов блока свертки по модулю два, другие входы которого соединены с выходами элементов памяти, а выходы его подключены к блоку распознавания ошибки.

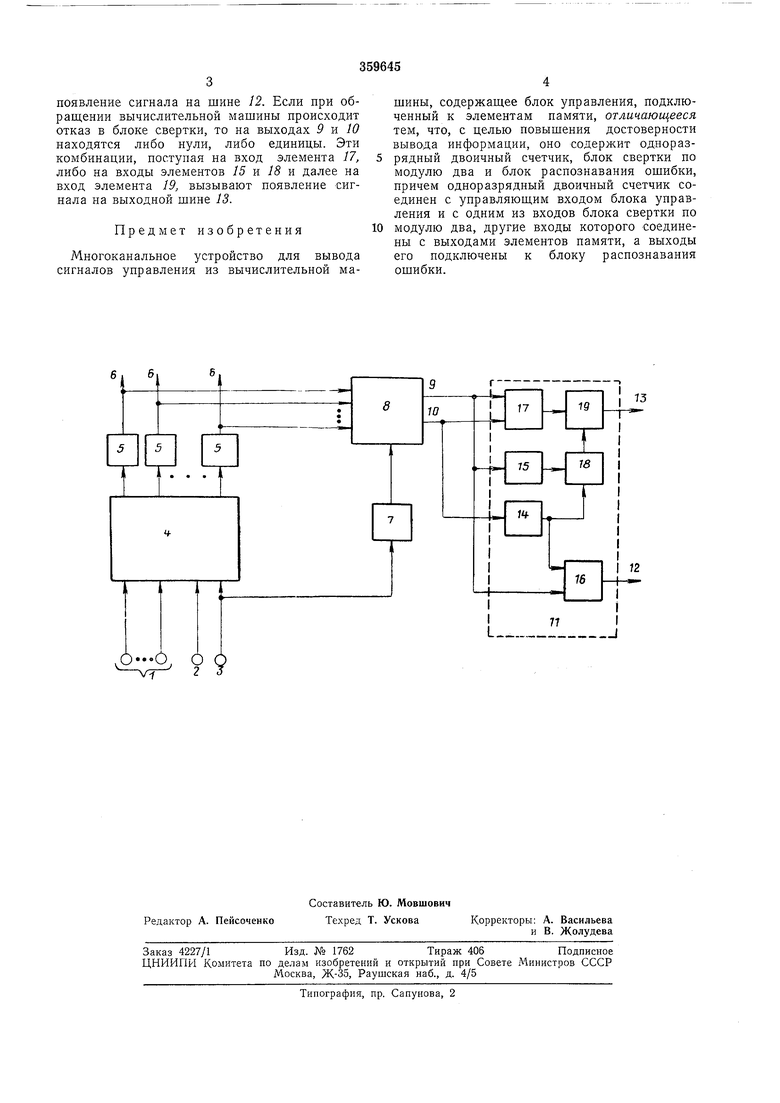

На чертеже дана блок-схема описываемого устройства.

ции, одноразрядный двоичный счетчик 7, блок 8 свертки по модулю два с прямым 9 и инверсным 10 выходами и блок И распознавания ошибки с выходными шинами 12 и 13, схемами «НЕ 14 и 15, схемами «И 16-18 и схемой «ИЛИ 19.

Устройство работает следующим образом. При обращении вычислительной машины к устройству на входные кодовые шины / и 2

и управляющий вход 3 поступают соответствующие сигналы. Блок 4 управления вырабатывает сигнал записи принятой информации в один из элементов 5 памяти в соответствии с кодом адреса на шинах /. При этом

состояние соответствующей выходной кодовой шины 6 изменяется на противоположное. Кроме того, сигнал обращения к устройству поступает на вход счетчика 7, изменяя его состояние. Если отказов в работе устройства

нет, то на прямом выходе 9 блока 8 находится нуль, а на инверсном выходе 10 - единица. Эта комбинация сигналов, поступая на вход блока 11 раснознавания ошибки, не изменяет состояния его выходов, а на выходиых шинах 12 и 13 сигналов нет. Если же при обращении вычислительной машины происходит отказ собственно устройства, то на выходе 9 блока 8 присутствз ет единица, а на выходе 10 - нуль. Эта комбинация, иоступоявление сигнала на шине 12. Если нри обращении вычислительной машины происходит отказ Б блоке свертки, то на выходах Р и /О находятся либо нули, либо единицы. Эти комбинации, поступая на вход элемента 17, либо на входы элементов 15 и 18 Е далее на вход элемента 19, вызывают появление сигнала на выходной шине 13.

Предмет изобретения

Многоканальное устройство для вывода сигналов управления из вычислительной машины, содержащее блок управления, подключенный к элементам памяти, отличающееся тем, что, с целью повышения достоверности вывода информации, оно содержит одноразрядный двоичный счетчик, блок свертки по модулю два и блок распознавания ошибки, причем одноразрядный двоичный счетчик соединен с управляющим входом блока управления и с одним из входов блока свертки по

модулю два, другие входы которого соединены с выходами элементов памяти, а выходы его подключены к блоку распознавания ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с самоконтролем | 1982 |

|

SU1084902A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1037348A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| ЧЕТЫРЕХТАКТНЫЙ РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2010 |

|

RU2475933C2 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

6 6 ,, о д

Даты

1972-01-01—Публикация