4

ОЭ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1559347A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1481775A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1566332A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении надежных микропроцессорных систем (МПС), Устройство обеспечивает контроль МПС с тремя шинами. Цель изобретения - повьпление достоверности контроля МПС в процессе функционирования. Устройство содержит два блока постоянной памяти, регистр, счетчик, схему сравнения, мультиплексор, триггер, элементы И и ИЛИ. Для обеспечения контроля в устройстве каждому машинному циклу команды ставится в соответствие адрес ячейки в блоке постоянной памяти. Содержимое этой ячейки памяти представляет информацию об ожидаемых сигналах на шине управления МПС, типе устройств, с которыми возможен обмен, последнем машинном цикле команды. Эта информация является исходной для m. iOBeASHnK контроля за корректным исполнением команд программы. При наличии любой некорректной ситуации при выполнении команд активируется выход ошибки устройства, который соединен с входом запроса прерывания процессора системы. Это обеспечивает переход к выполнению подпрограммы прерывания по ошибке с целью принятия необходимых действий. 1 ил., 4 табл. i (О

1

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем.

Цель изобретения - повышение достоверности контроля микропроцессорной системы в процессе функционирования .

На чертеже изображена структурная ,схема устройства.

Устройство для контроля микропроцессорной системы содержит первый .блок 1 постоянной памяти, адресный .

вход 2 устройства, мультиплексор 3, триггер 4, выход 5 ошибки устройства, вход 6 установки устройства, регистр 7, второй блок 8 постоянной памяти, вход 9 данных устройства, схему 10 сравнения, управляюший вход 11 устройства, счетчик 12, первый элемент И 13, первый элемент ИЛИ 14, второй элемент ИЛИ 15, третий элемент ИЛИ 16, второй элемент И 17. Предлагаемое устройство обеспечивает контроль наиболее распространенной микропроцессорной системы с

ГС

ю

31460722-

тремя шинами: шиной адреса, шиной устройства у1травления микропроцессо- данных и шиной управления. Для обес- ра или одновременного сбоя на шине печения контроля микропроцессорной адреса и управления, системы вход 11 устройства подключа- Для обнаружения некорректных си- ется к управляющей шине контролиру- туаций первой группы в устройстве емой системы, вход 2 - к старшим раз- производится сопоставление ожидаемо- ,рядам ее адресной шины, вход 9 - к го состояния шины управления МПС, со- шине данных, вход установки 6 - к це- ответствующее текущей команде, фак- пи сброса микропроцессора, а выход,5 ю тическому состоянию сигналов на ши- сигнала ошибки может подключаться к не управления в каждом машинном цик- входу запроса прерывания микропроцес- ле. В состав шины управления типовой сора или использоваться другим обра- мпС входят следующие сигналы: чтение зом. В общем случае контролируемая памяти (ЧТ), запись в память (ЗП), микропроцессорная система (МПС) со- 15 ввод (ВВ), вывод (Выв), чтение пер- держит постоянную память (ПЗУ), one- вого байта команды (Ml), ративную память (ОЗУ), в которой ор- Для обращения к внешним устройст- ганизуется стек, и устройства ввода- вам эти сигналы стробируются соот- вывода (УВВ). Нормальное функциони- ветствующими строб-сигналами микро- рование МПС заключается в корректном 20 процессора Прием (DB1N) или Выда- исполнении. команд микропроцессора, чи (WRITE).

расположенных в программной памяти Устройство работает следующим об- МПС. Известно, что реализация команд разом.

микропроцессора происходит в течение . Для осуществления контроля на со- одного или более машинных циклов. 25 ответствие ожидаемых и текущих сиг- При этом для каждой команды точно из- налов на шине управления МПС ожида- вестны количество составляющих ее емые состояния сигналов на этой шине, циклов и их типы. Тип машинного цикла соответствующие каждой команде мик- несет информацию о типе устройства, ропроцессора, хранятся в блоке 8 по- к которому осуществляется обращение, ЗО стоянной памяти. Адрес ячейки блока и о характере сигналов шины управле- 8 памяти формируется из кода команды, ния МПС, с помощью которых осуществ- поступающего с выхода регистра 7, ляется обмен информацией.и текущего номера машинного цикла

Таким образом, нормальное функцио- исполняемой команды, поступающего с нирование МПС характеризуется коррект- g выхода счетчика 12. Разрядность счет- ным выполнением команд (по машинным чика 12 определяется исходя из коциклам) и соответствием информации на личества машинных циклов, необходимых шине адреса и управления в каждом на- ддя вьтолнения самой длинной команды, шинном цикле реализации команды. -рак, для микропроцессора КР580ВМ80А

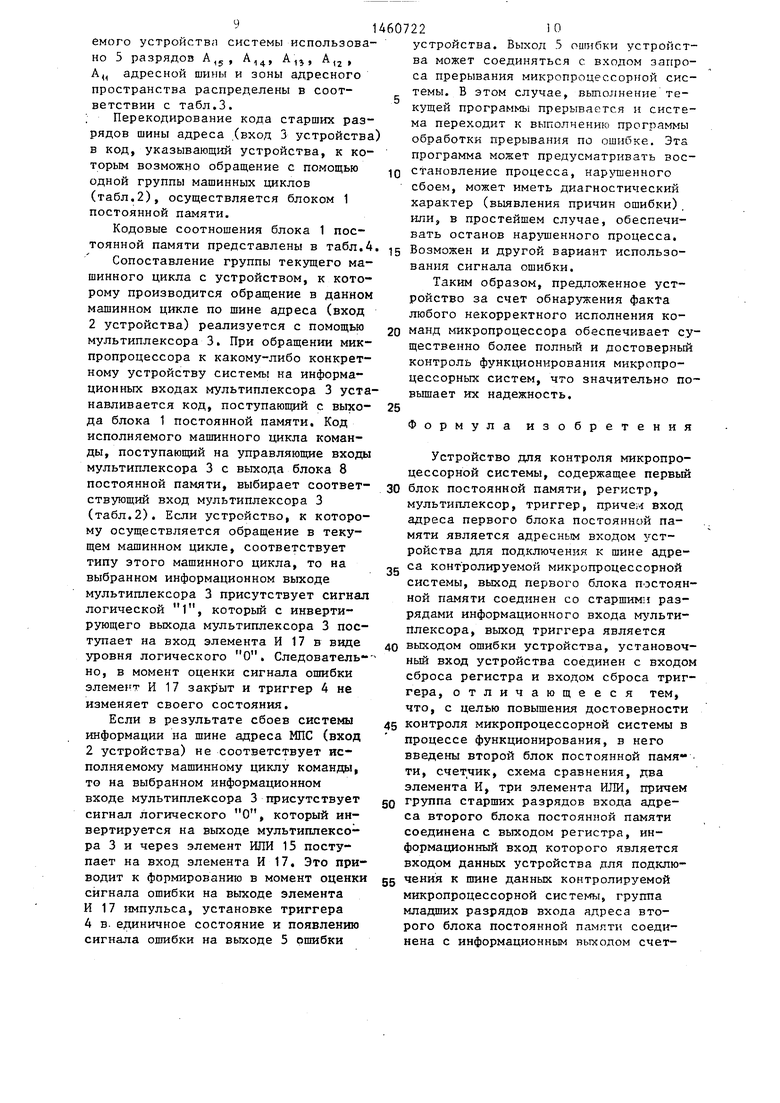

При работе МПС в условиях помех 40 максимальное количество машинных цик- возможны и отказы системы, которые лов для выполнения команды равно 5. приводят к нарушению ее нормального Тогда разрядность счетчика 12 должна функционирования. При этом наиболее быть равна 3, и он имеет 8 состояний, часто причинами нарушения нормального Часть ячеек описывает корректные функционирования являются: 5 машинные циклы, используемые при ренарушение корректного выполнения ализации команды. Другая часть ячеек, команд, обусловленное нарушением количество которых равно разнице межпроцесса чтения и декодирования ко- ду числом состояний счетчика 12 и манды, например, вследс- вие отказа числом корректных машинных циклов, шины данных или регистра и дёшифрато- gg описывает некорректные с точки зре- ра команд микропроцессор а, а также ния исполняемой команды машинные цик- пропуском или основанием лишних ма- лы. Эти ячейки могут выбираться лишь шинных циклов микропроцессора, напри- при нарушении нормального функционн- мер, вследствие сбоя в схеме форми- рования МПС, связанного с превьш1ени- рования машинных циклов микропроцес- gg ем количества машинных циклов при ис- сора;полнении текущей команды. В табл.1

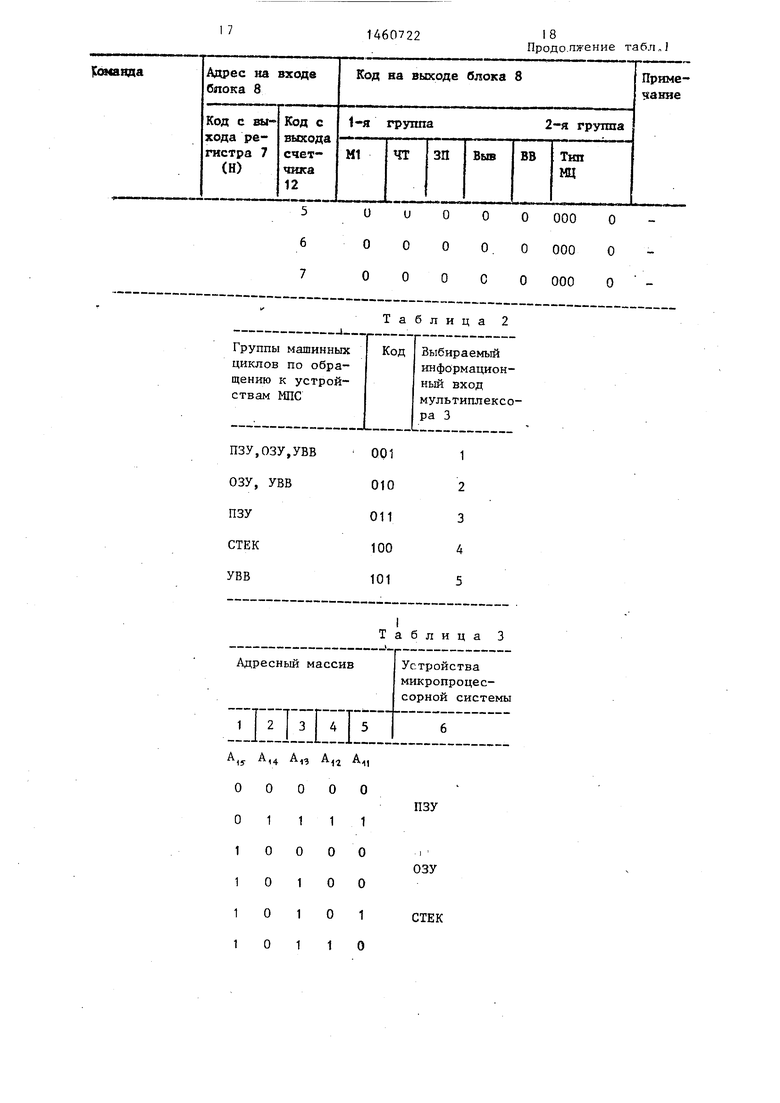

нарушение соответствия сигналов приведены фрагменты содержимого блока на шине адреса и управления текущей постоянной памяти 8 для контроля МПС .командой, например, вследствие сбоя на базе микропроцессора КР580ВМ80А.

В частности, выход поля типа операций (1-я группа) блока 8 постоянной памяти содержит информацию о состоянии основных сигналов шины управления МПС по машинным циклам для каждой конкретной команды микропроцес- сора.

В качестве контролируемых сигнало шины управления выбраны сигналы Ml, ЧТ, ЗП, Выв, ВВ.

В примечании табл.1 знаком Ч обозначены ячейки блока 8 постоянной памяти, обращение к которым разрешено при нормальной работе МПС. Знаком - отмечены ячейки, адресация к которым производится при реализации избыточных машинных циклов при вьтолнении текущей команды микропроцессора. В этих ячейках записаны нули, что соответствует непрограммируемым ячейкам памяти.

Контроль за соответствием ожидаемых и текущих сигналов на шине управления МПС осуществляется схемой 10 сравнения. При этом оценка сигнала ошибки, поступающего с выхода схемы 10 сравнения через элемент ИЛИ 15 на вход элемента И 17, осуществляется стробирующими сигналами Выдача или Прием микропроцессора, поступающими через элемент ИЛИ 16 на второй вход элемента И 17.

При нормальном функционировании МПС осуществляется чтение команд из программной памяти. При этом код команды появляется на шине данных системы (вход 9 устройства) и сопровождается сигналом М1. Под действием

При переключении счетчика 12 соответствие сигнало в на входе схемы 10 сравнения нарушается и на ее выходе формируется уровень логической единицы,свидетельствующий об ошибке. Однако в этот момент времени оценка

15 сигнала ощибки не производится и поэтому на выходе элемента И 17 сигнал ложной ошибки отсутствует. При нормальном функционировании JfflC в момент оценки сигнала ошибки соответ20 ствие кодов на входах схемы 10 сравнения всегда установлено, и нулевой сигнал с ее выхода запирает элемент И 17, что блокирует формирование сиг нала на его выходе. В результате

25 триггер 4 всегда находится в исходно состоянии, в которое он был переведе при начальном сбросе системы. При этом на выходе 5 ошибки устройства установлен нулевой уровень, свиде30 тельствующий об отсутствии од ибки.

При нарушении приема или декодирования команд вследствие отказов или сбоев системы ожидаемая комбинация сигналов с выхода блока 8 памяти

og не совпадает с текущей комбинацией сигналов на шине управления МПС (вход 11 устройства). В результате схема 10 сравнения формирует сигнал

ошибки, который поступает на устано- этого сигнала код команды записывает- 40 вочный вход триггера А, переводя его ся с щины данных системы в регистр в единичное состояние. При этом на 7 и одновременно сбрасывается в нулевое состояние счетчик 12, подготавливая устройство к контролю за выполвыходе 5 ошибки устройства появляется активный уровень, свидетельствующий об ошибке. Для контроля за стронением первого машинного цикла. В ре- 45 гим соответствием фактического и

зультате этого на выходе поля типа операций блока 8 памяти появляется информация, описьгоающая ошвдаемые ,. i

состояния сигналов на шине управления системы (вход 11 устройства) в пер- 50 вом машинном цикле текущей команды.

При соответствии ожидаемого и текущего состояний сигналов на йшне управления системы на выходе схемы 10 сравнения формируется уровень логи- 55 ческого нуля, свидетельствующий об отсутствии ошибки в текущем машинном цикле. При переходе к следующему машинному циклу текущей команды появ

ляется сигнал Синхронизация, указывающий начало очередного машинного цикла. При этом состсяи1-;е счетчика 12 увеличивается на 1, подготавливая устройство к контролю очередного машинного цикла, которьш осуществляется аналогично.

При переключении счетчика 12 соответствие сигнало в на входе схемы 10 сравнения нарушается и на ее выходе формируется уровень логической единицы,свидетельствующий об ошибке. Однако в этот момент времени оценка

сигнала ощибки не производится и поэтому на выходе элемента И 17 сигнал ложной ошибки отсутствует. При нормальном функционировании JfflC в момент оценки сигнала ошибки соответствие кодов на входах схемы 10 сравнения всегда установлено, и нулевой сигнал с ее выхода запирает элемент И 17, что блокирует формирование сигнала на его выходе. В результате

триггер 4 всегда находится в исходном состоянии, в которое он был переведен при начальном сбросе системы. При этом на выходе 5 ошибки устройства установлен нулевой уровень, свидетельствующий об отсутствии од ибки.

При нарушении приема или декодирования команд вследствие отказов или сбоев системы ожидаемая комбинация сигналов с выхода блока 8 памяти

не совпадает с текущей комбинацией сигналов на шине управления МПС (вход 11 устройства). В результате схема 10 сравнения формирует сигнал

ошибки, который поступает на устано- вочный вход триггера А, переводя его в единичное состояние. При этом на

выходе 5 ошибки устройства появляется активный уровень, свидетельствующий об ошибке. Для контроля за строожидаемого количества машинных цикл при реализации текущей команды микропроцессора используется одноразрядный выход разрешения записи данных (выход 3) блока 8 памяти. Значение этого разряда равно 1 лишь в ячейках блока 8 памяти, соответствующих последнему машинному циклу для каждой команды.

Как видно из табл.1, например, для команды NOP сигнал на выходе разрешения записи данных (выход 3) блока 8 памяти равен логической 1 в первой ячейке группы ячеек, объединеиных кодом команды NOP, а для команды CALL ADDR сигнал на этом выходе равен логической 1 в пятой ячейке группы ячеек, объединенных кодом команды CALL ADDR, так как эти команды выполняются, соответственно, за 1 и 5 машинных циклов. Таким образом, при исполнении последнего машинного цикла команды на выходе разрешения записи данных (выход 3) блока 8 памяти всегда формируется единичный сигнал, который поступает на вход элемента И 13, подготавливая его к передаче в следующем машинном цикле ожидаемого сигнала Ml на вход синхронизации регистра 7 и вход сброса счетчика 12, т.е. подготавливая цикл контроля очередной команды.

Если же в результате отказа или сбоя МПС ожидаемый сигнал М1 после выполнения последнего машинного цикл текущей команды не формируется, то счетчик 12 не сбрасывается, а увет личивает свое состояние на 1 по приходу очередного импульса Синхронизация. Это приводит к обращению к ячейкам блока 8 памяти, описывающим некорректные машинные циклы. В этом случае с выхода блока 8 памяти на вход схемы 10 сравнения поступает нулевая комбинация ожидаемых сигнало шины 11 управления (см. табл.1). При этом соответствие сигналов на входах схемы 10 сравнения в момент оценки сигнала ошибки не будет установлено, и триггер 4 будет установлен -в единичное состояние, фиксируя ошибку.

Если же в результате отказа или сбоя МПС при выполнении текущей команды пропущен один или несколько машинных циклов, то эта ситуация также обнаруживается устройством. Действительно, факт пропуска машинного цикла команды однозначно связано с внеочередным появлением сигнала М1 на шине 11 управления. Ко поскольку сигнал окончания команды на выходе разрешения записи данных бл ока 8 в этот момент времени не сфорь}ирован, то сигнал Ml не проходит через элемент И 13 на вход синхронизации регистра 7 и записи кода новой команды не происходит. Это означает, что на выходе блока 8 устанавливается комбинация сигналов на шине управления МПС (вход 1 1 устройства), соответствуто607228

щая пропущенному машинному циклу команды. Появление неожидаемого сигнала Ml на шине управления МПС обнаруживается схемой 10 сравнения, что приводит к появлению единичного сигнала на выходе 5 ошибки устройства.

Для обнаружения некорректных ситуаций второй группы в предлагаемом

0 устройстве производится сопоставление информации, устанавливаемой на шине адреса системы (вход 2 устройства), на соответствие текущему машинному циклу исполняемой команды, Действи15 тельно, в каждом машинном цикле допустимо обращение лишь к корректному типу устройств микропроцессорной системы. Некоторые машинные циклы допускают обращения к различньи устройст20 вам МПС. Например, в цикле чтения информации допустимо обращение к ОЗУ и к ПЗУ. В зависимости от возможности обращения к устройствам МПС все типы машинных циклов можно разбить на

25 группы.

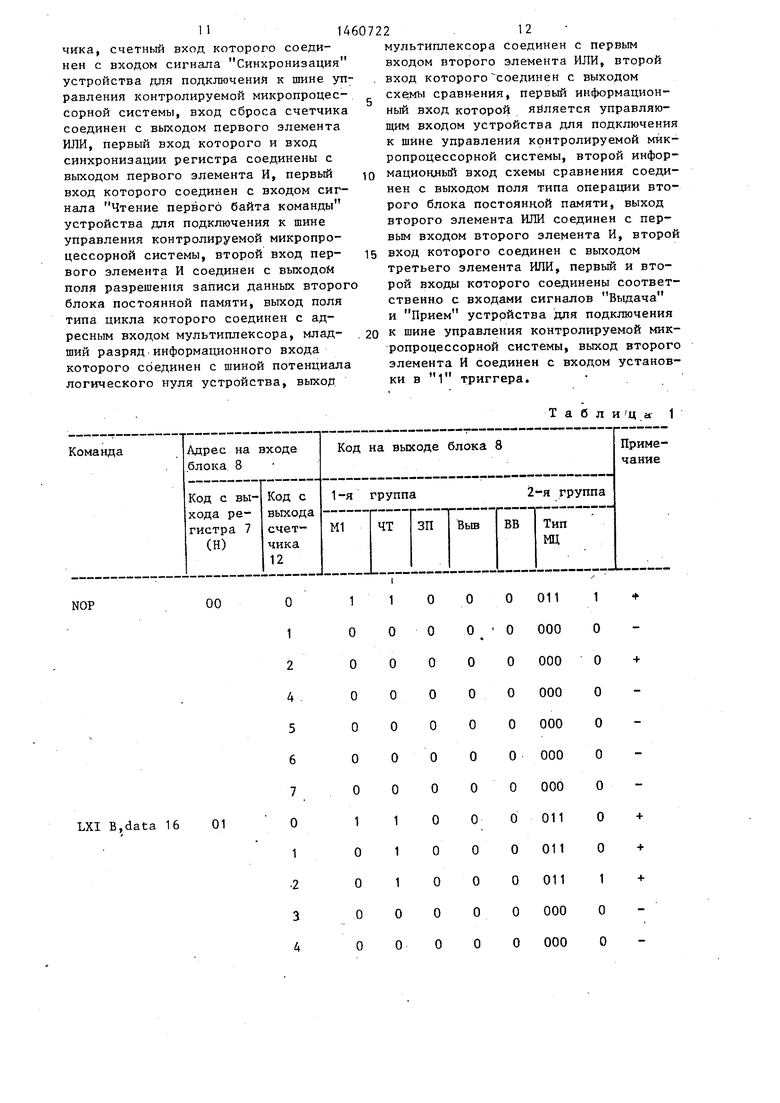

Кодирование машинных циклов по обращению у устройствам МПС представлено в табл.2.

Так, например, код 001 соответст30 вует таким машинным циклам микропроцессора, в которых допустимо обращение к одному из трех устройств МПС: ПЗУ, ОЗУ и УВВ. Код 011 соответствует машинным циклам чтения команды, в

35 которых разрешено обращение только к прог раммному ПЗУ. Код 100 соответствует машинным циклам обращения к стеку при выполнении стековых команд.

Для идентификации устройств МПС на стадии программирования программист должен распределить зону адресного пространства микропроцессора и закрепить за каждым из устройств системы определенную адресную зону. При этом, как правило, часть адресного пространства остается неиспользованной. Для упрощения селекции выбираемого устройства распределения адресов осуществляется таким образом, чтобы по старшим разрядам можно было определить устройство, к которому осуществляется обращение. Количество используемых для этого старших разрядов определяется минимальным объемом адресного пространства, закрепленного за каким-либо устройством микропроцессорной системы, nycTfe, например, для идентификации выбираемого устройства

но 5 разрядов А,, А,4, А,, А,,

системы использова15

А, адресной шины и зоны адресного пространства распределены в соответствии с табл.3.

; Перекодирование кода старших разрядов шины адреса .(вход 3 устройств в код, указывающий устройства, к которым возможно обращение с помощью одной группы машинных циклов (табл.2), осуществляется блоком 1 постоянной памяти.

Кодовые соотношения блока 1 постоянной памяти представлены в табл.4

Сопоставление группы текущего машинного цикла с устройством, к которому производится обращение в данном машинном цикле по шине адреса (вход 2 устройства) реализуется с помощью мультиплексора 3. При обращении мик- пропроцессора к какому-либо конкретному устройству системы на информационных входах мультиплексора 3 устанавливается код, поступающий с выхода блока 1 постоянной памяти. Код исполняемого машинного цикла команды, поступающий на управляющие входы мультиплексора 3 с выхода блока 8 постоянной памяти, выбирает соответствующий вход мультиплексора 3 (табл.2). Если устройство, к которому осуществляется обращение в текущем машинном цикле, соответствует типу этого машинного цикла, то на выбранном информационном выходе мультиплексора 3 присутствует сигнал логической 1, которьй с инвертирующего выхода мультиплексора 3 поступает на вход элемента И 17 в виде уровня логического О. Следовательно, в момент оценки сигнала ошибки элемент И 17 закрыт и триггер 4 не изменяет своего состояния.

Если в результате сбоев системы информации на шине адреса МПС (вход 2 устройства) не соответствует исполняемому машинному циклу команды, то на выбранном информационном входе мультиплексора 3 присутствует сигнал логического О, который инвертируется на выходе мультиплексора 3 и через элемент ИЛИ 15 поступает на вход элемента И 17. Это приводит к формированию в момент оценки сигнала ошибки на выходе элемента И 17 импульса, установке триггера 4 в. единичное состояние и появлению сигнала ошибки на выходе 5 ошибки

46072210

устройства. Выход 5 ошибки устройства может соединяться с входом са прерывания микропроцессорной сис- темы. В этом случае, вьтолнение текущей программы прерывается и система переходит к выполнению программы обработки прерывания по ошибке. Эта программа может предусматривать вос1Q становление процесса, нар%тпенного сбоем, может иметь диагностический характер (выявления причин ошибки) или, в простейшем случае, обеспечивать останов нарушенного процесса.

15 Возможен и другой вариант использования сигнала ошибки.

Таким образом, предложенное устройство за счет обнаружения факта любого некорректного исполнения ко20 манд микропроцессора обеспечивает существенно более полный и достоверный контроль функционирования микропроцессорных систем, что значительно повышает их надежность.

Формула изобретения

Устройство для контроля микропроцессорной системы, содержащее первый

блок постоянной памяти, регистр, мультиплексор, триггер, приче вход адреса первого блока постоянной памяти является адресным входом устройства для подключения к шине адреса контролируемой микропроцессорной системы, выход первого блока постоянной памяти соединен со старшими разрядами информационного входа м шьти- йлексора, выход триггера является

выходом ошибки устройства, установочный вход устройства соединен с Входом сброса регистра и входом сброса триггера, отличающееся тем, что, с целью повьш1ения достоверности

контроля микропроцессорной системы в процессе функционирования, в него введены второй блок постоянной памя ти, счетчик, схема сравнения, два элемента И, три элемента ИЛИ, причем

группа старших разрядов входа адреса второго блока постоянной памяти соединена с выходом регистра, информационный вход которого является входом данных устройства для подключения к шине данных контролируемой микропроцессорной системы, группа младших разрядов входа адреса втоого блока постоянной памяти соединена с информационным выходом счетчика, счетный вход которого соединен с входом сигнала Синхронизация устройства для подключений к шине управления контролируемой микропроцессорной системы, вход сброса счетчика соединен с выходом первого элемента ИЛИ, первый вход которого и вход синхронизации регистра соединены с выходом первого элемента И, первый вход которого соединен с входом сигнала Чтение первого байта команды устройства для подключения к шине управления контролируемой микропроцессорной системы, второй вход первого элемента И соединен с выходом поля разрешения записи данных второг блока постоянной памяти выход поля типа цикла которого соединен с адресным входом мультиплексора, млад- ший разряд информационного входа которого соединен с шиной потенциала логического нуля устройства, выход

00

В,data 16

01

О

1

2

5

6

7

О 1

.2 3 4

мультиплексора соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом сравн-ения, первый информационный вход КОТОРОЙ1 является управляющим входом устройства для подключения к шине управления контролируемой микропроцессорной системы, второй информационный вход схемы сравнения соединен с выходом поля типа операции второго блока постоянной памяти, выход второго элемента ИЛИ соединен с первым входом второго элемента И, второй

вход которого соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с входами сигналов Выдача и Прием устройства для подключения

к шине управления контролируемой микропроцессорной системы, выход второго элемента И соединен с входом установки в 1 триггера.

Т а б л и ц сг 1

+ + +

13

STAX D

12

MVI М, data

36

ADD М

86

1460722

14

Г родолжение табл. 1

Команда

Адрес на входе блока 8

Код на выходе блока 8

Код с . выхода счетчика12

1-я группа

Ml

ЧТ

ALL ADDR

UT PORT

5

6

7

CD О 1 2 3 А

5 , 6 7

D3 О 1 2 3 4 5. 6 7

Неисполь- О

зуемые

коды 1

2 3

4

Примечание

2-я группа

ЧТ

1

о

о

о

о

о

о

о

зп

о

о

о

1

1

1

о

о

о

о

о

1

1

о

о

о

о

о

о

о

оо

оо

оо

оо

о

о

о

о

о

о

1

1

о

о

о

о

о

о

о

о

о

/

о о о

о о

о

Вьш

о о о о о о о о

D

о

о

о

о

1

о

о

о

о

о

о

о о о

вв

Тип

мц

О000

О000

О000

о011

о011

о011

о100

о100

о000

о000

о000

о011

о011

о101

о000

о000

о000

о000

о000

о000.

оооо

о 000

о000

о000

о

о

о

о

о

о

о

1

о

о

о

о

о

т

о

о

о

о

о

о

о о о

о

+ + +

+ +

+ +

ПЗУ,ОЗУ,УВВ

ОЗУ, УВВ

ПЗУ

СТЕК

УВВ

15,4 А,, AI,

0000

1 1 11

о о 00 0100 0101

1

0110

Таблица 2

2 3

4 5

Таблица 3

ПЗУ

ОЗУ

СТЕК

| Устройство для синтаксическогоКОНТРОля пРОгРАММ | 1978 |

|

SU807299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-23—Публикация

1987-06-30—Подача