равляющим входом первого блока памяти и вторым з равлякщим входом второго регистра сдвига, выход второго регистра сдвига соединен с входом второго дешифратора и входом мажоритарного элемента, выход мажоритарног элемента соединен с вторым входом элемента сложения по модулю два, выход второго блока памяти соединен с первым входом четвертого элемента И, выход второго дешифратора - с вторьм входом четвертого элемента И,

выход элемента сложения по модулю два - с третьим входом четвертого элемента И, выход которого соединен с информационньм входом второго триггера, выход третьего элемента И соединен с тактовым входом второго триггера, вход сброса второго тригге ра - с входом сброса устройства, нулевой вход второго триггера соединен с сигнальным входом устройства,выход второго триггера - с входом элемента НЕ и является выходом пркрывания устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛА ПРЕРЫВАНИЯ, содержащее элемент НЕ, первый элемент И, двоичный счетчик, первый дешифратор, группу элементов И, элемент ИЛИ, причем первый вход первого элемента И соединен с тактовым входом устройства, второй вход первого элемента И - с выходом элемента НЕ, выход первого элемента И - с счетным входом двоичного счетчика, первый выход двоич-. ного счетчика - с входом дешифратора и адресным выходом устройства, каждый выход дешифратора - с первым входом одноименного элемента И группы, вторые входы элементов И группы - с одноименными запросными входами устройства, выходы элементов И группы с входами элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности формирования общего сигнала прерывания по появлению запроса прерывания и по его снятию, а также улучшения помехозащищенности устройства, в него дополнительно введены генератор импульсов, второй, третий и четвертый элементы И, первый триггер, первый блок памяти, два регистра сдвига, элемент И-НЕ, мультиплексор, второй блок памяти, второй дешифратор, мажоритарный элемент, элемент сложения по модулю два, второй триггер, причем второй выход двоичного счетчика соединен с первым входом второго элемента И, с первым входом адреса первого блока памяти, с первым входом мультиплексора, с первым входом третьего элемента И, третий выход двоичного счетчика соединен с входом запуска генератора импульсов, первый выход двоичного счетчика - с вторым входом адреса первого блока памяти, с первым входом адреса второго блока памяти, с тактовым входом первого i регистра сдвига, первый выход генератора импульсов соединен с вторым k/) входом второго элемента И, второй выход генератора импульсов - с тактовым входом первого блока памяти, третий выход - с тактовым входом второго регистра сдвига, четвертый выход генератора импульсов соединен с вторым входом третьего элемента И, выход элемента ИЛИ - с информационN5 ным входом первого триггера, выход второго элемента И - с тактовым вхоСАЭ Дом первого триггера, выход первого а триггера - с информационным входом У1 первого блока памяти, вторым входом .адреса второго блока памяти, с первым входом элемента сложения по модулю два, выход первого блока памяти соединен с первым управляющим входом второго регистра сдвига, выходы первого регистра сдвига - с входами элемента И-НЕ и вторым входом мультиплек сора, выход элемента И-НЕ - с управляющим входом первого регистра сдвига и третьим входом мультиплексора, выход мультиплексора соединен с уп-.

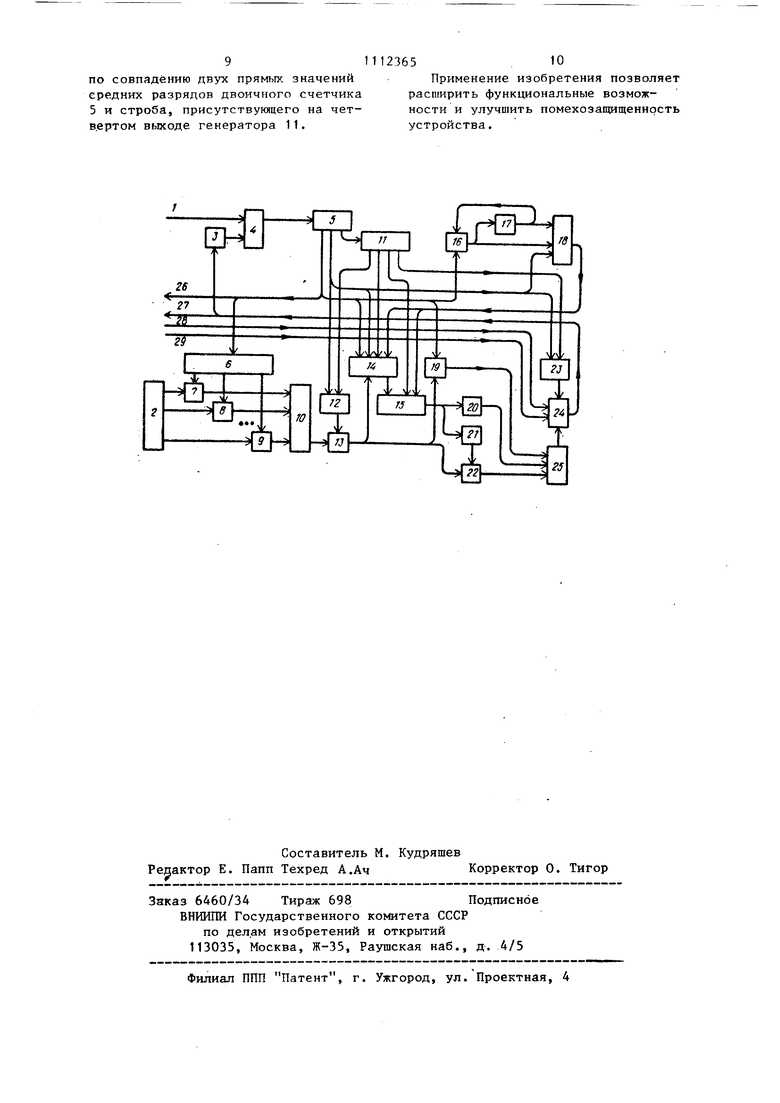

Изобретение относится к цифровой вьмислительной технике и может быть использовано в системах прерывания вычислительных систем, в том числе в управляющих вычислительных машинах и комплексах. Известна многоуровневая система прерывания, содержащая регистр, груп пу элементов ИЛИ, схему распознавания уровня прерывания и элемент ИЛИ выход которого является выходом пре рывания устройства 1J Недостатком этой системы является слабая помолоэащищенность Наиболее близким по технической сущности к предлагаемому является ус ройство формирования сигнала прерывания и системы, содержащее инвертор первый элемент И, двоичный счетчик, дешифратор, группу элементов И, элемент ИЛИ, причем первый вход первого элемента И соединен с тактовым входом устройства, второй вход первого элемента И.соединен с входом двоичного счетчика, выход двоичного счетчика соединен с входом деши ратора и с выходом устройства, выход дешифратора соединены с первыми входами элементов И, группы, вторые входы элементов И группы соединены с запросными входами устройства, вы ходы э тементов И группы соединены с входами элемента ИЛИ, выход которого является выходом прерьгаания устройства 2| . Устройство позволяет сформироват сигнал прерывания только по появлению (переднему фронту) запроса.. Недостатком устройства является то, что оно не позволяет формировать по появлению (переднему фронту) запроса и по его снятию (заднему фронту), что вытекает из необходимости удаления запроса, по появлению которого уже сформирован сигнал прерьгаания. Задача формирования двух сигналов прерывания по одному запросу, т.е. по появлению и по снятию запроса, возникает, например, в случаях формирования сигналов прерывания в узлах сопряжения пультов с вычислительными машинами. Пульты содержат кнопки и переключатели, переключение и нажатие которых и является запросом. Причем запрос на любом из уровней прерывания может находиться неограниченно долго и его снятие диктуется внешними условиями. Запрос, поступающий с кнопки и переключателя, характеризуется наличием помех (дребезга) при появлении (переднему фронту) и при снятии (заднему фронту). Известное устройство весьма чувствительно к , сопровождающим его работу, они приводят к разрьшам сигнала прерывания, неустойчивой временной диаграмме его формирования. Таким образом, недостатком известного устройства является также то, что оно не имеет защиты от помех, и, как следствие этого, невозможность в ряде задач непосредственного подключения УФСП к ИЗП. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности форми рования общего сигнала прерывания по появлению запроса прерывания и по его снятию, а также улучшение помехозащищенности устройства. Поставленная цегъ достигается тем-, что в устройство формирования сигнала прерывания, содержащее элемент НЕ, первый элемент И, двоичный счетчик, первьй дешифратор, группу элементов И, элемент ИЛИ, причем первый вход первого элемента И соединен с тактовым входом устройства, второй вход первого элемента И - с выходом элемента НЕ, выход первого элемента - с счетным входом двоичного счетчика, первый выход двоичного счетчика - с входом дешифратора и с адресным выходом устройства, каждый выход дешифратора - с первым входом одноименного элемента И груп пы, вторые входы элементов И группы с одноименными запросными входами устройства, выходы элементов и груп пы - с входами элемента ИЛИ, введены генератор импульсов, второй, т тий и четвертый элементы И, первый триггер, первый блок памяти, пе вый и второй регистры сдвига, элемент И-НЕ, мультиплексор, второй блок памяти, второй дешифратор, маж ритарный элемент, элемент сложения по модулю два, второй триггер, причем второй выход двоичного счетчика соединен с первым входом второго элемента И, с первым входом адреса первого блока памяти, с первым входом мультиплексора, с первым входом третьего элемента И, третий выход двоичного счетчика соединен с входо запуска генератора импульсов, первы выход двоичного счетчика - с вторьм входом адреса первого блока памяти, с первым входом адреса второго блок памяти, с тактовым входом первого регистра сдвига, первый выход генер тора импульсов соединен с вторым входом второго элемента И, второй выход генератора импульсов - с тактовым входом первого блока памяти, третий выход генератора импульсов с тактовым входом второго регистра сдвига, четвертый выход генератора импульсов соединен с вторым входом третьего элемента И, выход злемента ИЛИ - с информационным входом пе вого триггера, выход второго элемен та И - с тактовым входом первого триггера, выход первого триггера с информационным входом первого блока памяти, с вторым адресным входом второго блока памяти, с первым входом элемента сложения по модулю два, выход первого блока памяти соединен -с первым управляющим входом второго регистра сдвига, вьтходы первого регистра сдвига - с входами элемента И-НЕ, и вторым входом мультиплексора, выход элемента И-НЕ - с управляющим входом первого регистра сдвига и третьим входом мультиплексора, выход мультиплексора соединен с управляющим входом первого блока памяти и вторым управляющим входом второго регистра сдвига, выход второго регистра сдвига соединен с входом второго дешифратора ивходом мажоритарного элемента, выход мажоритарного элемента соединен с вторым входом элемента сложения по модулю два, выход второго блока памяти соединен с первым входом четвертого элемента И, выход второго дешифратора - с вторым входом четвертого элемента И, выход элемента сложения по модулю два - с третьим входом четвертого элемента И, выход которого соединен с информационным входом второго триггера, выход третьего элемента И соединен с тактовым входом второго триггера, вход сброса второго триггера с входом сброса устройства, нулевой вход второго триггера соединен с сигнальным входом устройства, выход второго триггера - с входом элемента НЕ и является выходом прерывания устройства. 1 На чертеже приведена структурная схема устройства. Устройство содержит тактовый вход 1 устройства, группу 2 запросных входов устройства, элемент НЕ 3, элемент И 4, двоичный счетчик 5, дешифратор 6, группу элементов .И 7-9, элемент ИЛИ 10, генератор 11 импульсов, элемент И 12, триггер 13, блок 1А памяти, регистры 15 и 16 сдвига, элемент И-НЕ 17, мультиплексор 18; блок 19 памяти, дешифратор 20, мажоритарный элемент 21, элемент 22 сложения по модулю два, элемент И 23, триггер 24, элемент И 25, адресный выход 26 устройства, выход 27 прерывания устройства, сигнальный вход 28 устройства, вход 29 сброса устройства. Устройство работает следующим образом. Счетчик 5, на который с некоторой частотой поступают импульсы с входа 1 при помощи дешифратора б и элементов И 7-9, в каждом такте проверки и наличия запроса на входах 2 проверяется уровень прерывания, номер кото рого совпадает с содержимым старших разрядов счетчика 5, поступающим в депшфратор 6 с первого выхода двоичного счетчика 5. Эта проверка уровня прерывания заключается в сравнении значения запросов за три прёдьщущих периода проверки, хранящимися в блоке 14 с текущим значением запроса (проверка- пояснена ниже) и определении факта изменения значения запроса. Если в данном уровне прерывания запрос не изменил значения, то через некоторое время произойдет изменение на единицу старших разрядовсчетчика 5 и проверяется следуюощй по порядку уровень прерывания. Если имеется изменение значения запроса, просмотр прекращается, устанавливается триггер 24, с выхода которого на выход 27 подается сигнал прерывания, а содержимое двоичного счетчика 5 исполь зуется для (формирования начального адреса прерывающей программы. Сигнал с выхода 27 поступает также на элемент НЕ 3 и запрещает прохождение импульсов с входа 1 через элемент И 4 на счетный вход двоичного счетчика 5, фиксируя его состояние. После передачи управления прерывающей программе объекта управления из него по входу 28 поступает сигнал, сбрасы вающий триггер 24, и процедура поиск запросов возобновляется. Через некот рое время произойдет изменение на единицу старпшх разрядов счетчика 5 и проверяется следующий по порядку уровень прерывания. Проверка уровней прерывания для формирования сигнала прерывания заключается в сравнении значения сигнал запроса за -три предыдущих периода проверки, хранящимися в блоке 14, с текущим значением запроса и определении фасета «изменения значения запроса Работа блока 14 в составе устройства происходит следующим образом В блоке 14 каждому уровню прерывания отведена зона из четьфех одноразрядных слов, идущих подряд одно за другим. Зона блока 14 определяется 11

ням прерывания элемент И-НЕ 17 переключается, после чего в течение периода поиска на управляющем входе 56 старшими разрядами счетчика 5, ее номер совпадает с номером уровня прерывания . В течение периода поиска по всем уровням проверка значения запроса будет выполняться в стандартном такте проверки, В этот такт проверки выполняется одна операция, записи информации в блок 14 и три операции считывания информации из блока 14. Обращение к четьфем словам зоны блока 14 вьтолняется с помощью двух средних размеров двоичного счетчика 5, находящихся на его втором выходе. Это обращение к-словам блока 14 выполняется по очереди, т.е. к первому слову зоны, далее к второму, третьему i затем четвертому. Для какого слова будет выполняться операция записи информации, определяет управляющая информация, поступающая из мультиплексора. 18 на управляющий вход блока 14. Для данного периода поиска по всем уровням прерывания номер слова в зоне блока 14, в которое выполняется запись информации, один и тот же. В конце периода поиска этот номер изменяется циклически, т.е. если в данный период поиска запись вьшолняется в слово зон блока 14 номер четыре, то в следующий период запись информации выполняется в слово зон номер один, а по прошествии еще двух периодов поиска - снова в слово номер четыре и т.д. I Номер слова зон блока 14, в которое выполняется запись информации, формируется совместной работой регистра сдвига 16, элемента И-НЕ 17 мультиплексора 18. На тактовый вход регистра 16 сдвига поступает самый старший разряд двоичного счетчика 5, по заднему фронту этого разряда выполняется операция записи информации в регистр 16 сдвига. Все выходы второго регистра сдвига 16 соединяются между собой через элемент И-НЕ 17, выход которого подключен к управляющему входу регистра 16 сдвига. Поэтому до тех пор, пока на одном из выходов второго регистра 16 сдвига имеется логический нуль, в него будут записьшаться сигналы логической единицы. После трех периодов поиска по всем уроврегистра 16 сдвигя будет логически) нуль. Благодаря этому логический нуль будет только на одном выходе регистра 16 сдвига или на выходе элемента И-НЕ 17. Выходу элемента И-НЕ 17 поставлены в соответствие все первые слова зон блока 14. Трем выходам регистра 16 сдвига поставлены в соответствие все вторые, третьи и четвертые слова зон блока 14 соответственно. Опрос значений выходов регистра 16 сдвига и выхода элемента И-НЕ 17 выполняет мультиплексор 18, на управляющий вход которого поступают два средних разряда двоичного счетчика 5. На выходе мультиплексора 18 появляется признак,обозначающий выполнять блоку 14 операцию записи или операцию считывания данного слова.

Адрес обращения к слову в блоке 14 образуется объединением старших и средних разрядов двоичного счетчика 5, присутствующих на его первом и втором выходах.

Такт проверки изменения значения запроса в данном уровне прерывания одинаков для всех зон блока .14, Он состоит из подячи кода уров ня прерывания на дешифратор 6 и второй адресный вход блока 14, операции записи текущего значения запроса с выхода элемента ИЛИ 10 в триггер 13, четырех операций обращения к блоку 14, трех операций записи значения за проса за три предьщущих периода проверки и операции записи сигнала прерывания с выхода элемента И 25 в тригер 24. Строб записи информации в триггер 13 формируется элементом И 12 по совпадению двух инверсных значений средних разрядов двоичного счетчика 5 и строба, присутствующего на первом выходе генератора 11. При этом триггер 13 зафиксирует значение запроса на весь такт поиска, это обеспечивает возможность асинхронной работы источника запросов по отношению к устройству,. Значение запроса с выхода триггера 13 поступит на информационный вход блока 14. Эта информация будет записана в блок 14 тогда, когда с выхода мультиплексора 18 поступит признак записи. После записи значения запроса в триггер 13 вьшолняются четыре операции обращения к блоку 14, каждая из которых сопровождается признаком записи

или счит.1ва1И я, ггос.тупающим из мульплексора 18. Этот же признак поступает и на управляющий вход регистра 15 сднига, который во время операци записи в блок 14 пропустит такт записи информации. Операции записи значения запроса с выхода блока 14 в регистр 15 сдвига выполняются во время трех операций считывания информации из блока 14. Синхронизацию работы блока 14 и триггера 13 выполняет генератор 11. В блоке 14 значение запроса запишется с выхода триггера 13, что обеспечит использование значения запроса в следуюиш периоды проверки. После четырех операций обращение к блоку 14 в регистре 15 сдвига имеем трехразрядно слово, содержащее значение за три предьиущих периода проверки. Информация с выхода регистра 15 сдвига параллельным трехразрядным кодом поступает на дешифратор 20 и мажоритарньй элемент 21.

С выхода мажоритарного элемента 21 сигнал поступает на второй вход элемента 22.

Элемент 22 сравнивает состояние триггера 13, равное текущему значению запроса, с сигналом с выхода элемента 21 и формирует на выходе сигнал разрешения (логическая, единица) в случае несовпадения сигнало на его входах и сигнал запрета (логический ноль) в случае совпадения.

Блок 19 содержит признаки разрешения формирования прерывания по по явлению и по снятию запроса.

Адрес обращения к слову блока 19 образуется слиянием старших разрядов счетчика 5 и информации на выходе триггера 13. В блоке 19 в слове, соответствующем данной зоне блока 14 и значению запроса,поступающему из триггера 13, хранится информация разрешено (логическая единица)если разрешено формирование сигнала прерьшания по снятию запрос и запрет (логический ноль) в противном случае.

Элемент И 25 формирует значение сигнала прерывания логическая единица при появлении трех сигналов разрешено на выходах блока 19 дешифратора 20 и элемента 22 и значени логический ноль в противном случае.

Строб записи информации в триггер 24 формируется элементом И 23

91112365 0

по совпадению двух прямых значений Применение изобретения позволяет ередни разрядов двоичного счетчика расширить функциональные возмож5 и прису ствую,цего на чет- ности и улучшить помехозащищенность в.ертом выходе генератора 11.устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| М., Энергия, 1979, с.296, рис.8-15 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с.298, рис.8-16 (прототип) . | |||

Авторы

Даты

1984-09-07—Публикация

1983-06-03—Подача