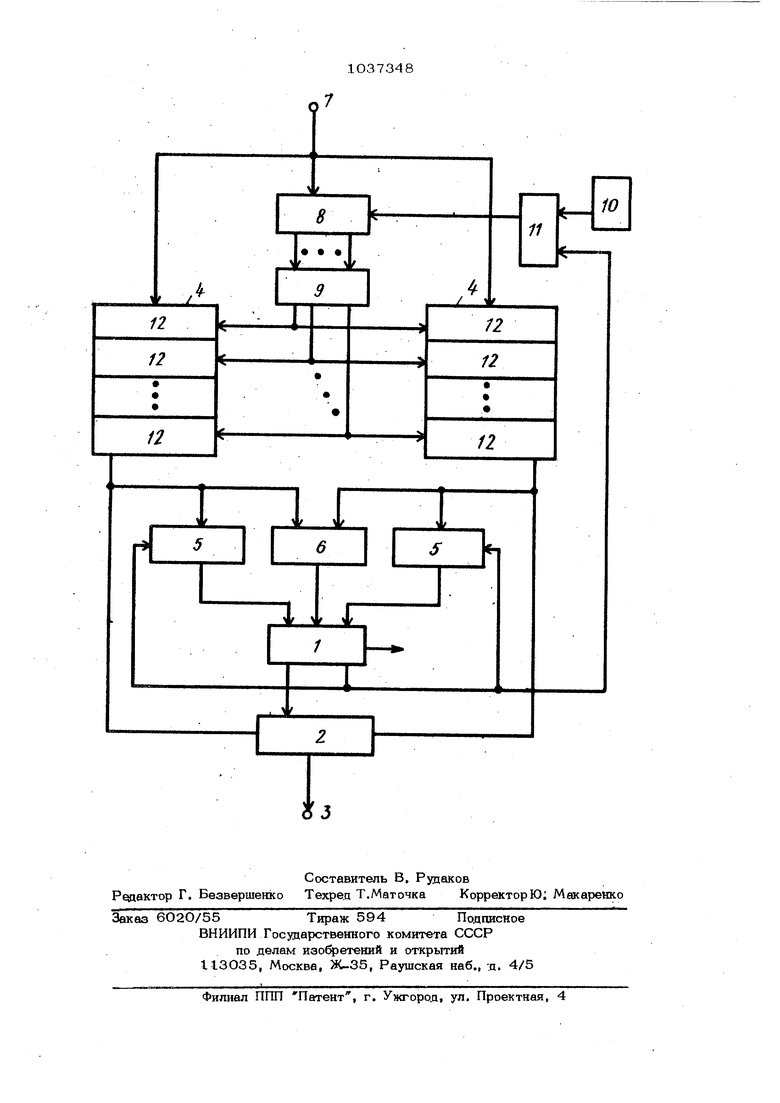

I1 Изобретение относится к вычислитель ной технике и предназначено для использования в устройствах повышенной на-- дежности, в частности в специализирован ных вычислительных машинах. Извесгнорезервированное запоминающе устройство.которое содержит три блока памя ти, один из которых находится в ненагруженном резерве и соединен с источником питания через ключ, компараторы, служащие для сравнения выходной информашш, блок кон ,роля, блок регенерации, мажоритарный элемент и шины: адресную, обращения, ос танова и данных. В процессе выборки производится сравнение информации, пост паюдей из двух блоков памяти, и при несовпадении производится подалючение резервного блока. При этом информация восстанавливается с помощью мажори тарного органа, а определение номерй неисправного блока памяти производится с помгацью блока контроля, входы которо го соединены с выходами компараторов LI. , Недостатком этого зйпоминаквдего уст ройства является высокая сложность, устройства, обусловленная наличием трех блоковпамяти, хранящих вдентичную информашпо. Наиболее близким техническим решением к изобретению является резервированное запоминшсяцее устройство, содержащее накопители, блок управлшия, входные коммутаторы, выходные коммута торы, блоки свертки по модулю два, бло поразрядного сравнения, коммутатор, причем вкодыустройства соединены с соответствующими входами входных коммутаторов, выходы которых соединены с входами накопителей, выходы которых соедине ны с входами выходных коммутаторов, выходы которых соединены с входами соответствующих блоков свертки по моду лю два, входами блока поразрядного сра нения и входами коммутатора, выход которого соединен с выходом устройства, выходы блоков свертки по модулю два и блока поразрядного сравнения соединшы -с входами блока управления, выходы которого соединены с управляклдими входами входных и выходных коммутаторов, управпякший выход блока управления соедини с управляющим входом коммутатора 2. Недостатком известного устройства является низкая надежность, о15условленная тем, что в случае пост{зоен1Ш устройства с двумя накопителями может 48 исправляться лишь двухкратная ошибка, возникающая при отказе одного из накопителей. Ошибки кратности больше .двух не исправляются, поскольку становится невозможньп 1 определить номер отказывающего накопителя. Для увеличения кратности исправляемой ошибки необходимо увеличивать число накопителей. КромеТОГО входные и выходные коммутаторы необходимы лишь для Построения оперативных запоминающих устройств, в Которых возможна коммутация входов и вьпсодов отказавшего разряда на резервный. В случае построения постоянного запоминающего устройства необходимость во входных и выходных коммутаторах отпа,аает, но кратность исправляемой ошибки при этом снижается до е.аинииы. Цель изобретения - повышение на,аежности устройства за счет исправления многократных ошибок. Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее блоки свертки по модулю два, блок поразря,аного сравнения, блок управления, коммутатор и накопите ли информации, одни из в-.одов которых соответственно объединены и являются адресными входами устройства, а выходы подключены к информационным входам блоков свертки по модулю два, блока поразрящного сравнения и коммутатора, вь1ход которого является выходом устройства| выходы блока поразрядного сравнения и блоков свертки по модулю два по.аключены к входам блока управления, выход которого соединен с управляющим входом коммутатора, введены счетчик импульсов, дешифратор, элемент И и генератор импульсов, выход которого подключен к одному из входов элемента И, выход которого соединен с одним из входов счетчика импульсов, другие входы которого подключены к адресным входам устройства, а выходы ,-. к дёши зратора, выходыкоторого соединеныс дру гими входами накопителей информации, второй выход блока управления подключен к другому входу опеме«г& И и управЛ5по1цим входам блоков свертки по модулю два. На чертеже изображена структурная схила предлагаемого устройства. Устройство содержит блок I управления, ксялмутатор 2, выход 3 которого является выходом устройства, накопители 4 информашш, блоки 5 свертки по модутпо два и блок 6 поразрядного сравнеьшя. Адресный вход 7 устройства связан с входами счетчика 8 импульсов и накопителей 4. Устройство также содержит дешифратор 9, генератор 10 импульсов и элемент ИИ. Кажцый накопитель 4 разделен на сегменты 12, управляющий вход канодого из которых соединен с управляющими входом соответствукзщего сегмента друго ,го накопителя и соответствующим выходом дешифратора 9. При этом все сегменты, кроме последнего, хранят рабочую информацию, а последний предназначается для хранения результата поразрядного су мирования по модулю для информашш по совпадающим адресам из остальных (рабочих) сегментов. Устройство работает следующим обра- зом. В исходном состоянии накопители 4 исправны и обрабатывают одну и ту же, информацию в виде адреса на вход 7. БЛОК 6 поразрядного сравнения вьщает сигнал об отсутстви-и неисправности в блок I управления. Бпок I выдает сигнал разрешения использования информации с одного из накопителей на коммутатор 2, который подсоединяет к выходу устройств 3 один из накопителей 4. Блок 5 и гене ратор 10 участия в работе не принимают поскольку блокированы управляющим сигналом с выхода блока 1 управления. Сче чик 8 в этом случае выполняет роль тистра старших разрядов адреса, поступа юших по входу 7, производя выборку соответствующего сегмента 12 внутри накопителя 4 с помощью дешифратора 9. Выбор контактной ячейки внутри сегмент определяют младшие разряды адреса, пос тупающие по входу 7 на вход накопител } 4. При возникновении ошибки любой кратности в одном иэ накопителей блок .6 обнаруживает наличие отказа в поступи ще{{информа«ии и выдает соответствующий v сигнал на вход блока l управления. По этсму сигналу блок I блокирует про-:; хождение информации от ншсопителей 4 на выход 3 через коммутатор 2. На выходе блока t управления появляется сиг13484 нал, разрешающ1Й работу блоков 5 и прохождение счетных lainynbcoB от генератора 1О через элемент ИИ на счетный вход счетч1гка 8. Этот же сигнал из блока I управлеН1ш поступает в ЦВМ и производит приостанов вычислений до выделения достоверной информации. При этом счетчик 8 перево.дится в режим счета импульсов от генератора 10. Счетчик 8 производит подсчет числа импульсов, равного числу сегментов t2, При этом . происходит выборка из каждого сегмента по адресу в соответствии ic информацией на входо 7. Так как тТЬследний сегмент содержит результат поразрядного суммировппия вьтодулюдпа , информации, находящейся п остальных: сегментах по совпадающим дц{5есаь, в результате такой последовательной выбор,кй в блоке 5, производившем свертку информаци, поступающей от исправного накопителя 4, содержится нулевая информа ция, в другом блоке 5, производившем свертку информации, поступающей от неисправного накопителя 4, содержится информация, отличная от нулевой. По этим сигналам от блоков 5, поступающим на входы блока I управления, последний выдает сигнал на вход коммутатора 2| для присоединения к выходу 3 устройства исправного нак,опителя 4. Одновремйсно с другого выхода блока 1 выдается сигнал, I прекращающий прохождение счетных импульсов от генератора 10 через элемент И И на счетный вход счетчика 8 и снимается сигнал Приостанов вычислений ЦЕМ. Таким образом производится обнаружение к локализация неисправностей. Предлагаемое устройство обла,дает повыщенной на.дежностью по-сравнению с известным. Кратностьисправляемой ошибки К и число накопителей Р в известном устройстве связаны отношением К 2{Р - I), т. е. для исгфавления 4-кратной ошибки требуется тринакопителя, а для исправления 8-кратной ошибки требуется пять накопителей, тогда как в предлагаемом устройстве для выдачи правильной информации независимо от кратности ошибок требуется.два накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1095240A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1381597A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1089627A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Резервированное оперативное запоминащее устройство | 1975 |

|

SU589623A1 |

РЕЗЕРВИРОВАННОЕ ЗАПОМИ НАЮШЕЕ УСТРОЙСТВО, содержащее блоки свертки по модулю два, блок поразрадного сравнения, блок управления, коммутатор и накопители информации, одни из входов которых соответственно объединены и являются адресными входами устройства, а выходы подключены к информационным входам блоков свертки по модулюдва, блока поразрццного сравнения и ком СЕ€ОШ1 Д | мутатора, выход которого является выходом устройства, выходы блока поразpsi,nHoro сравнения и блоков свертки по модулю два подключены к входам блока управления, первый выход которого соединен с управляющим входом коммутатора, отличают ееся тем, что, с целью повышения надежности устройства в него введены счетчик импульсов, дешифратор, элемент И и генератор импульсов, выход которого подключен к одному из входов элемента И, выход которо-г го соединен с одним из входов счетчика импульсов, другие входы которого подключены к адресным входам устройства, а выходы - к входам деиофратора, выходы i которого соединены с другими входами накопителей информации, второй выход Л блока управления подключен к другому входу И и управляющим входам блоков свертки по модулю два. О :о vj :о Jlib эо

| I | |||

| Резервированное запоминающее устройство | 1977 |

|

SU710076A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Резервированное оперативное запоминащее устройство | 1975 |

|

SU589623A1 |

| Солесос | 1922 |

|

SU29A1 |

| (прототип). | |||

Авторы

Даты

1983-08-23—Публикация

1982-04-16—Подача