Изобретение относится к вычислительной технике, может быть использовано в дублированных запоминающих устройствах с коррекцией ошибок и является усовершенствованием изобретения по авт. СБ. № 972600.

Целью изобретения является повышение надежности устройства.

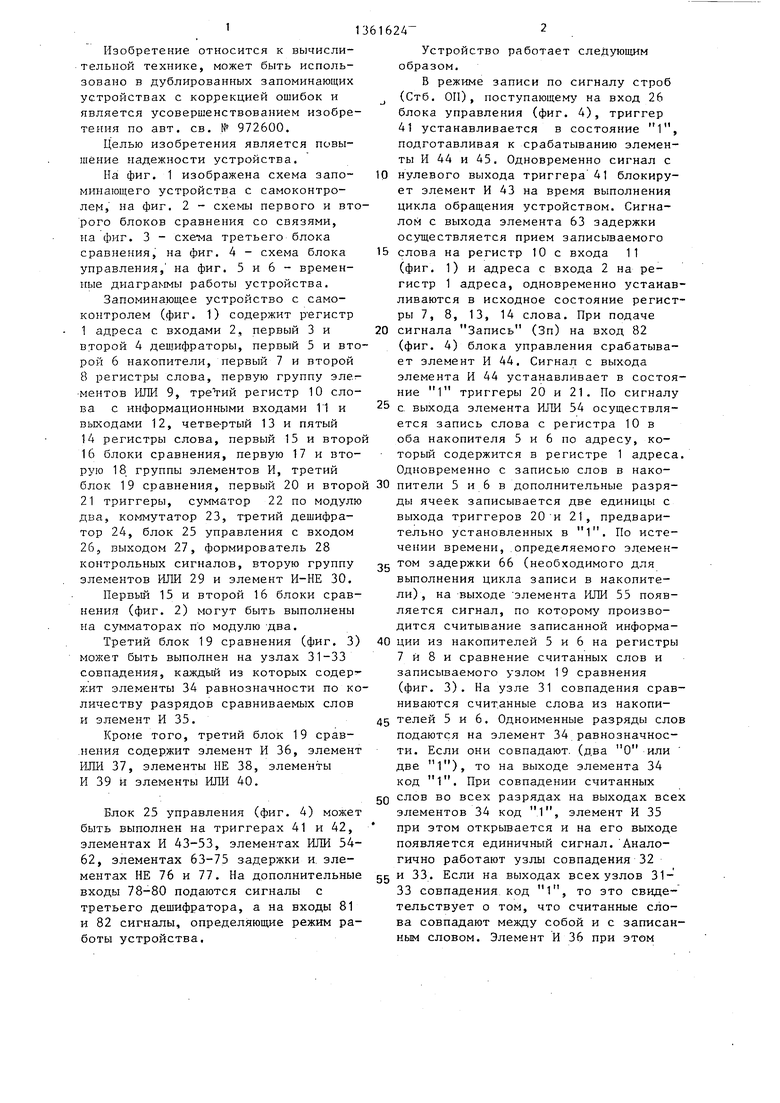

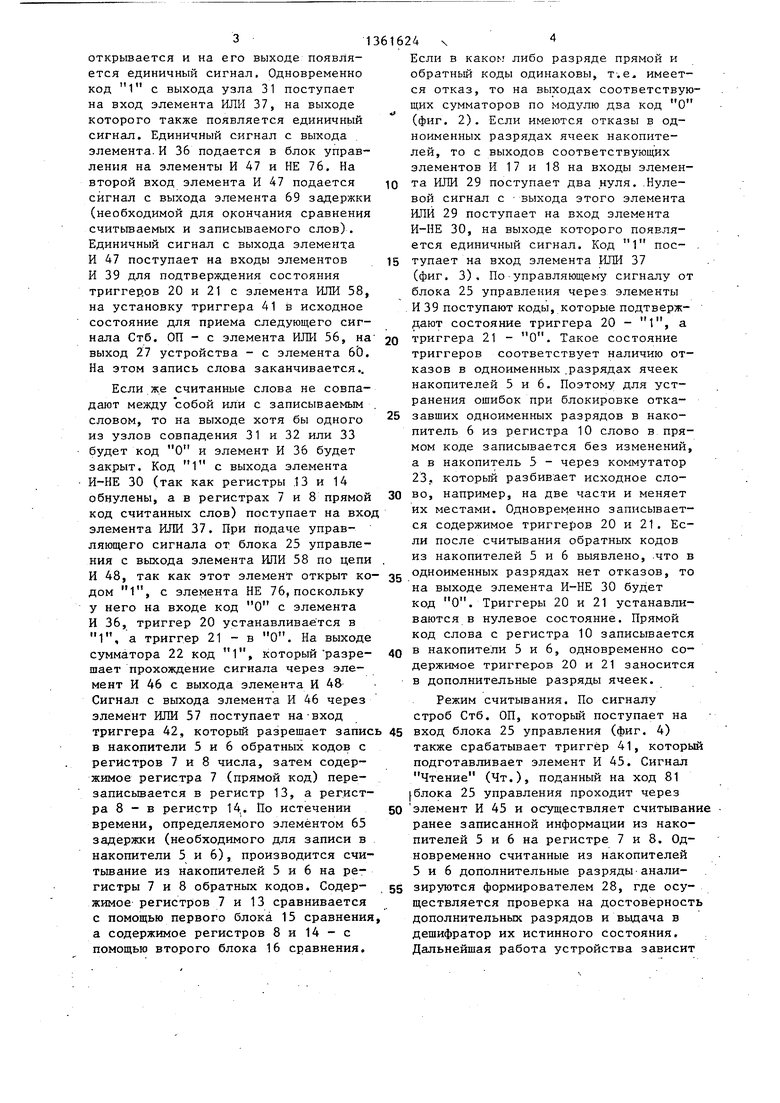

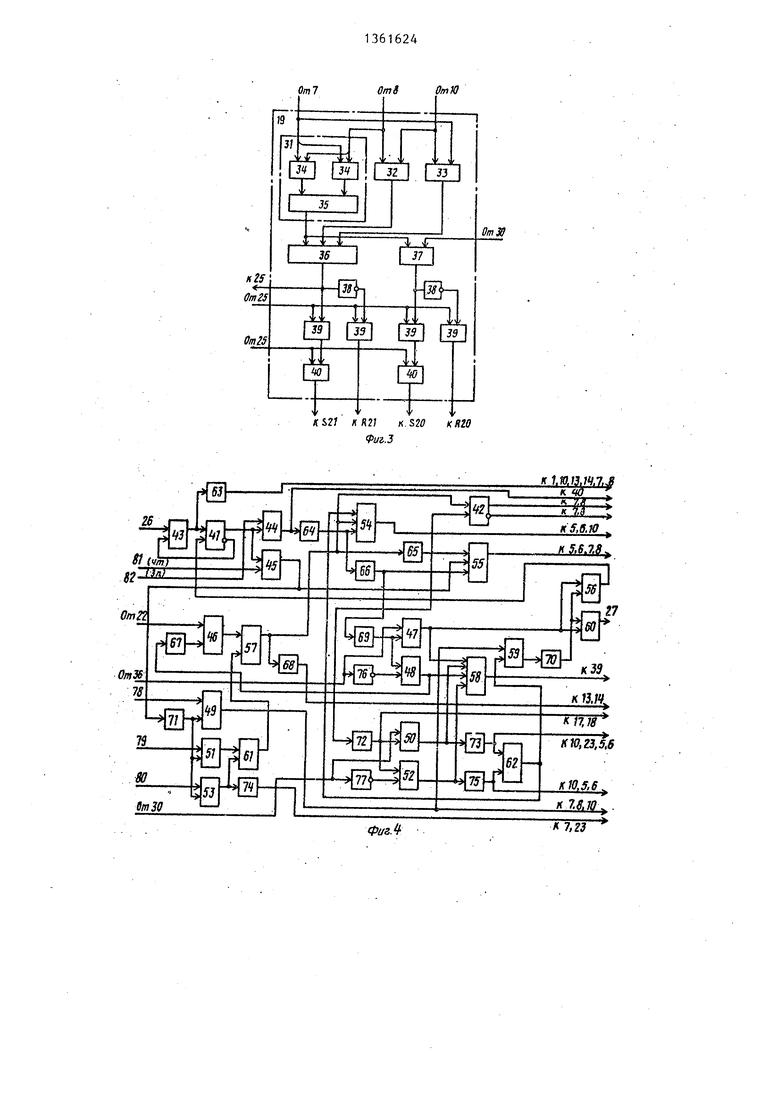

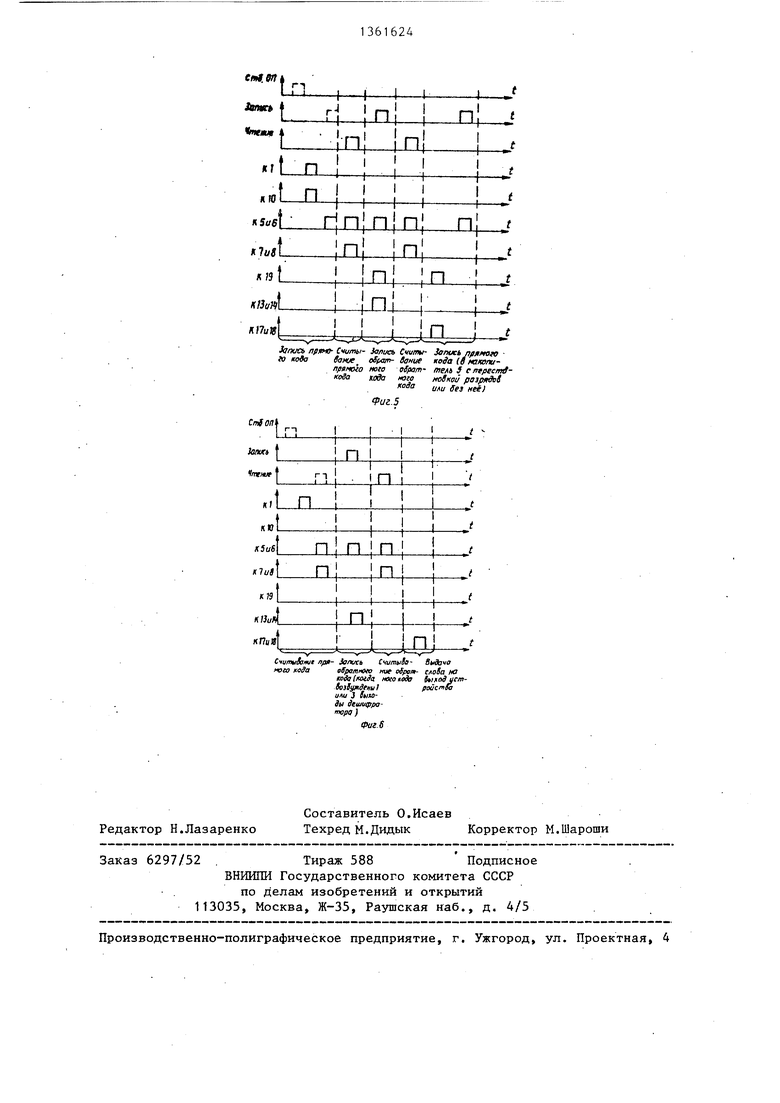

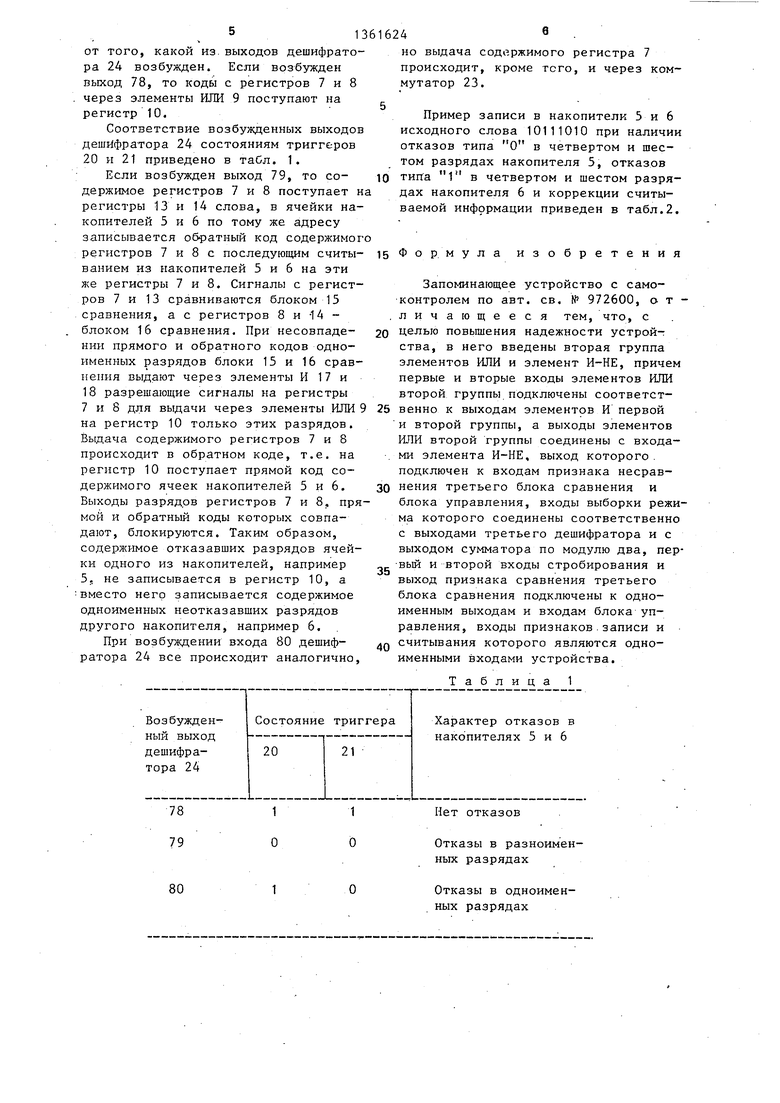

На фиг. 1 изображена схема запоминающего устройства с самоконтролен, на фиг. 2 - схемы первого и второго блоков сравнения со связями, на фиг. 3 - схе-ма третьего блока сравнения, на фиг. 4 - схема блока управления, на фиг. 5 и 6 - временные диаграммы работы устройства.

Запоминающее устройство с самоконтролем (фиг. 1) содержит р егистр 1 адреса с входами 2, первый 3 и второй А дешифраторы, первый 5 и второй 6 накопители, первый 7 и второй 8 регистры слова, первую группу элег- ментов ИЛИ 9, третий регистр 10 слова с информационными входами 11 и выходами 12, четвертый 13 и пятый 14 регистры слова, первый 15 и второ 16 блоки сравнения, первую 17 и вторую 18 группы элементов И, третий

блок 19 сравнения, первый 20 и второй 30 пители 5 и 6 в дополнительные разря21 триггеры, сумматор 22 по модулю два, коммутатор 23, третий дешифратор 24, блок 25 управления с входом 26, выходом 27, формирователь 28 контрольных сигналов, вторую группу элементов ИЛИ 29 и элемент И-НЕ 30.

Первый 15 и второй 16 блоки сравнения (фиг. 2) могут быть выполнены на сумматорах по модулю два.

Третий блок 19 сравнения (фиг. 3) может быть выполнен на узлах 31-33 совпадения, каждый из которых содер жит элементы 34 равнозначности по количеству разрядов сравниваемых слов и элемент И 35.

Кроме того, третий блок 19 срав- .нения содержит элемент И 36, элемент ИЛИ 37, элементы НЕ 38, элементы И 39 и элементы ИЛИ 40.

Блок 25 управления (фиг. 4) может быть выполнен на триггерах 41 и 42, элементах И 43-53, элементах ИЛИ 54- 62, элементах 63-75 задержки и. элементах НЕ 76 и 77. На дополнительные входы 78-80 подаются сигналы с третьего дешифратора, а на входы 81 и 82 сигналы, определяющие режим работы устройства.

10

36162Д 2

Устройство работает следующим образом.

В режиме записи по сигналу строб , (Стб. Oil), поступающему на вход 26 блока управления (фиг. 4), триггер 41 устанавливается в состояние 1, подготавливая к срабатыванию элементы И 44 и 45. Одновременно сигнал с нулевого выхода триггера 41 блокирует элемент И 43 на время выполнения цикла обращения устройством. Сигналом с выхода элемента 63 задержки осуществляется прием записываемого слова на регистр 10 с входа 11 (фиг. 1) и адреса с входа 2 на регистр 1 адреса, одновременно устанавливаются в исходное состояние регистры 7, 8, 13, 14 слова. При подаче сигнала Запись (Зп) на вход 82 (фиг. 4) блока управления срабатывает элемент И 44. Сигнал с выхода элемента И 44 устанавливает в состояние 1 триггеры 20 и 21. По сигналу с выхода элемента ИЛИ 54 осуществляется запись слова с регистра 10 в оба накопителя 5 и 6 по адресу, ко- торьм содержится в регистре 1 адреса. Одновременно с записью слов в нако15

20

25

ды ячеек записывается две единицы с выхода триггеров 20 и 21, предварительно установленных в 1. По истечении времени, .определяемого элемен22 том задержки 66 (необходимого для выполнения цикла записи в накопители), на выходе элемента ИЛИ 55 появляется сигнал, по которому производится считывание записанной информа40 ции из накопителей 5 и 6 на регистры 7 И 8 и сравнение считанных слов и записываемого узлом 19 сравнения (фиг. 3). На узле 31 совпадения сравниваются считанные слова из накопи45 телей 5 и 6. Одноименные разряды слов подаются на элемент 34 равнозначности. Если они совпадают, (два О или две 1), то на выходе элемента 34 код 1. При совпадении считанных

5Q слов во всех разрядах на выходах всех

элементов 34 код 1, элемент И 35 при этом открывается и на его выходе появляется единичный сигнал. Аналогично работают узлы совпадения 32

55 и 33. Если на выходах всех узлов 31- 33 совпадения код 1, то это свидетельствует о том, что считанные слова совпадают между собой и с записанным словом. Элемент И 36 при этом

открывается и на его выходе появляется единичный сигнал. Одновременно код 1 с выхода узла 31 поступает на вход элемента ИЛИ 37, на выходе которого также появляется единичный сигнал. Единичный сигнал с выхода элемента. И 36 подается в блок управления на элементы И 47 и НЕ 76. На второй вход элемента И 47 подается сигнал с выхода элемента 69 задержки (необходимой для окончания сравнения считьшаемых и записываемого слов). Единичный сигнал с выхода элемента И 47 поступает на входы элементов И 39 для подтверждения состояния триггеров 20 и 21 с элемента ИЛИ 58, на установку триггера 41 в исходное состояние для приема следующего сигнала Стб. ОП - с элемента ИЛИ 56, на выход 27 устройства - с элемента бЬ. На этом запись слова заканчивается..

Если же считанные слова не совпадают между собой или с записываемым словом, то на выходе хотя бы одного из узлов совпадения 31 и 32 или 33 будет код О и элемент И 36 будет закрыт. Код 1 с выхода элемента И-НЕ 30 (так как регистры .13 и 14 обнулены, а в регистрах 7 и 8 прямой код считанных слов) поступает на вхо элемента ИЛИ 37. При подаче управляющего сигнала от блока 25 управления с выхода элемента ИЛИ 58 по цепи

И 48, так как этот элемент открыт ко- 35 . разрядах нет отказов, то

дом 1,

с элемента НЕ 76,поскольку у него на входе код О с элемента И 36, триггер 20 устанавливается в 1, а триггер 21 - в О. На выходе сумматора 22 код 1, который разрешает прохождение сигнала через элемент И 46 с выхода элемента И 48 Сигнал с выхода элемента И 46 через элемент ИЛИ 57 поступает на-вход

на выходе элемента И-НЕ 30 будет код О. Триггеры 20 и 21 устанавливаются в нулевое состояние. Прямой код слова с регистра 10 записывается 40 в накопители 5 и 6, одновременно содержимое триггеров 20 и 21 заносится в дополнительные разряды ячеек.

Режим считывания. По сигналу строб Стб. ОП, который поступает на

триггера 42, который разрешает запись 45 вход блока 25 управления (фиг. 4)

в накопители 5 и 6 обратных кодов с регистров 7 и 8 числа, затем содержимое регистра 7 (прямой код) пере- записьтается в регистр 13, а регистра 8 - в регистр 14. По истечении времени, определяемого элементом 65 задержки (необходимого для записи в накопители 5 и 6), производится счи- тьшание из накопителей 5 и 6 на регистры 7 и 8 обратных кодов. Содержимое регистров 7 и 13 сравнивается с помощью первого блока 15 сравнения а содержимое регистров 8 и 14 - с помощью второго блока 16 сравнения.

s

0

0

5

Если в каком либо разряде прямой и обратный коды одинаковы, т-.е имеется отказ, то на выходах соответствующих сумматоров по модулю два код О (фиг. 2). Если имеются отказы в одноименных разрядах ячеек накопителей, то с выходов соответствующих элементов И 17 и 18 на входы элемента ИЛИ 29 поступает два нуля. .Нулевой сигнал с выхода этого элемента ИЛИ 29 поступает на вход элемента И-НЕ 30, на выходе которого появляется единичный сигнал. Код 1 пос- , тупает на вход элемента ИЛИ 37 (фиг. 3). По-управляющеьгу сигналу от блока 25 управления через элементы И 39 поступают коды, которые подтверждают состояние триггера 20 - 1, а триггера 21 - О. Такое состояние триггеров соответствует наличию отказов в одноименных .разрядах ячеек накопителей 5 и 6. Поэтому для устранения ошибок при блокировке отказавших одноименных разрядов в накопитель 6 из регистра 10 слово в прямом коде записывается без изменений, а в накопитель 5 - через коммутатор 23. который разбивает исходное слово, например, на две части и меняет их местами. Одновременно записывается содержимое триггеров 20 и 21. Если после считывания обратных кодов из накопителей 5 и 6 выявлено, .что в

разрядах нет отказов, то

на выходе элемента И-НЕ 30 будет код О. Триггеры 20 и 21 устанавливаются в нулевое состояние. Прямой код слова с регистра 10 записывается в накопители 5 и 6, одновременно содержимое триггеров 20 и 21 заносится в дополнительные разряды ячеек.

Режим считывания. По сигналу строб Стб. ОП, который поступает на

также срабатывает триггер 41, который подготавливает элемент И 45. Сигнал Чтение (Чт.), поданный на ход 81 блока 25 управления проходит через

50 элемент И 45 и осуществляет считывание ранее записанной информации из накопителей 5 и 6 на регистре 7 и 8. Одновременно считанные из накопителей 5 и 6 дополнительные разряды-анали55 зируются формирователем 28, где осуществляется проверка на достоверность дополнительных разрядов и выдача в дешифратор их истинного состояния. Дальнейшая работа устройства зависит

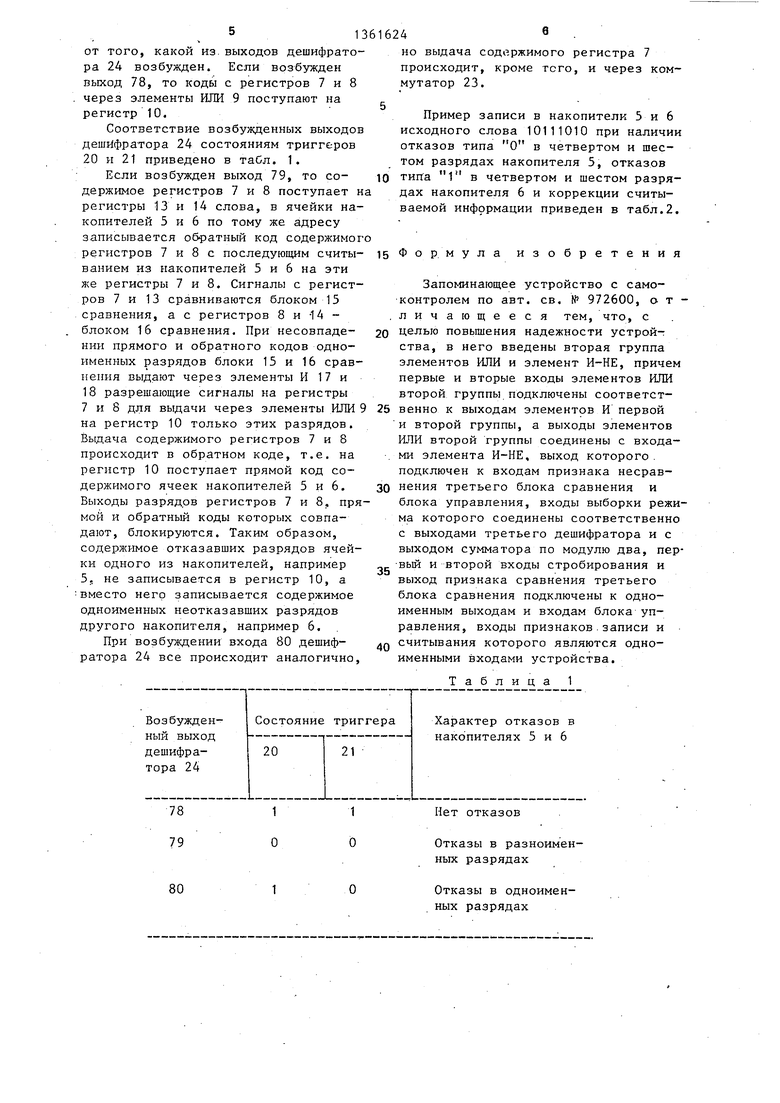

от того, какой из. выходов дешифратора 24 возбужден. Если возбужден выход 78, то коды с регистров 7 и 8 через элементы ИЛИ 9 поступают на регистр 10.

Соответствие возбужденных выходов дешифратора 24 состояниям триггеров 20 и 21 приведено в таСл. 1.

Если возбужден выход 79, то содержимое регистров 7 и 8 поступает н регистры 13 и 14 слова, в ячейки накопителей 5 и 6 по тому же адресу записывается обратный код содержимог регистров 7 и 8 с последующим считыванием из накопителей 5 и 6 на эти же регистры 7 и 8. Сигналы с регистров 7 и 13 сравниваются блоком 15 сравнения, а с регистров 8 и -14 - блоком 16 сравнения. При несовпадении прямого и обратного кодов одноименных разрядов блоки 15 и 16 сравнения выдают через элементы И 17 и 18 разрешающие сигналы на регистры

7 и В для выдачи через элементы ИЛИ 9 25 венно к выходам элементов И первой

на регистр 10 только этих разрядов. Выдача содержимого регистров 7 и В происходит в обратном коде, т.е. на регистр 10 поступает прямой код содержимого ячеек накопителей 5 и 6. Выходы разрядов регистров 7 и 8, прямой и обратный коды которых совпадают, блокируются. Таким образом, содержимое отказавших разрядов ячейки одного из накопителей, например 5., не записывается в регистр 10, а вместо негр записывается содержимое одноименных неотказавших разрядов другого накопителя, например 6.

При возбуждении входа 80 дешиф- ратора 24 все происходит аналогично

80

но выдача содержимого регистра 7 происходит, кроме того, и через коммутатор 23.

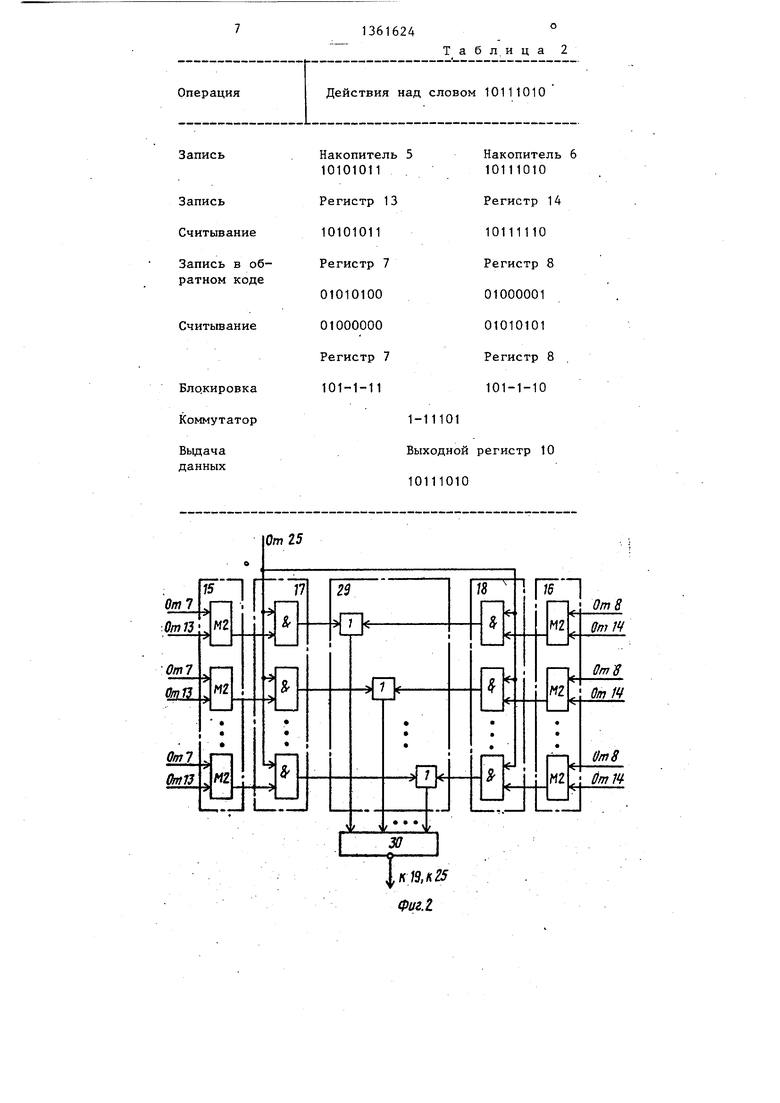

Пример записи в накопители 5 и 6 исходного слова 10111010 при наличии отказов типа О в четвертом и шестом разрядах накопителя 5, отказов типа 1 в четвертом и шестом разрядах накопителя 6 и коррекции считываемой информации приведен в табл.2.

Формула изобретения

Запоминающее устройство с самоконтролем по авт. св. № 972600, о т - личающееся тем, что, с целью повьшения надежности устройства, в него введены вторая группа элементов ИЛИ и элемент И-НЕ, причем первые и вторые входы элементов ИЛИ второй группы.подключены соответстО

Q

5

и второй группы, а выходы элементов ИЛИ второй группы соединены с входами элемента И-НЕ, выход которого . подключен к входам признака несравнения третьего блока сравнения и блока управления, входы выборки режима которого соединены соответственно с выходами третьего дешифратора и с выходом сумматора по модулю два, пер- вый и второй входы стробирования и выход признака сравнения третьего блока сравнения подключены к одноименным выходам и входам блока управления, входы признаков.записи и считывания которого являются одноименными входами устройства.

Таблица 1

ных разрядах

Отказы в одноименных разрядах

Операция

Действия над словом 10111010

Накопитель 5 10101011

Накопитель 6 10111010

Регистр 13Регистр 14

1010101110111110

Регистр 7Регистр 8

0101010001000001

0100000001010101

Регистр 7Регистр 8

101-1-11101-1-10

1-11101

Выходнойрегистр 10

10111010

Накопитель 6 10111010

От

к,21 яяг; K.S20 кяго

Фиг.З

OmSОтЮ

25 J-1

(vmj Ш5Г

OmZ2

ОтХ

к 1МШЧ.7,

ФигЛ

A7,W

Запиа пряма- Считы- Запал Cvumi-Запись ыямога

го кода faitje olpam- баниеч ва (в ттпиifffnoio нога elpam-тем } с nrpscmiKoSa иода юганойкой разрядов

ши Set неё

Фиг.5

C4umtieftai при- Запль fvi//n /fo- flwbva veo кодаoSpamHOto иие oSpon- елоЗа но

кода ( наго яодо htifodjfcmhjlymimulpauc St

али 3 ouutды deututfrfloтра)

Фиг.б

Редактор Н.Лазаренко

Составитель О.Исаев

Техред М.Дидык Корректор М.Шароши

Заказ 6297/52 . Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1075312A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Запоминающее устройство с автономным контролем | 1978 |

|

SU780049A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

Изобретение относится к вычислительной технике и может быть использовано в дублированных запоми-. нающих устройствах с коррекцией ошибок. Целью изобретения является повышение надежности устройства. Устройство содержит регистр 1 адреса, первый и в.торой накопители 5, 6с дешифраторами 3, 4 адреса, регистры слова 7, 8, 10, 13, 14 с первого по пятый, первый, второй и третий блоки 15, 16, 19 сравнения, первую и вторую группы 29 элементов ЮТИ, первую и вторую группы 17, 18 элементов И, первый и второй триггеры 20, 21, сумматор 22 по модулю два, коммутатор 29, третий дешифратор 24, блок 25 управления, формирователь 28 контрольных сигналов, элемент И-НЕ 30. Запоминающее устройство сохраняет работоспособность при всех возможных комбинациях отказавших одноименных разрядов двух накопителей. 6 ил, 2 табл. UmlS (Л От 25 1Ч (риг.}

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-31—Подача