1

Изобретение относится к области запоминающих устройств.

Известно устройство для контроля магнитных запоминающих элементов тонкоплепочных матрин, содержащее генератор тактовых импульсов, подключенный ко входу счетчика разрушающих имнульсов, выход которого подсоединен ко входу счетчика адреса, подключенного к пересчетному триггеру, триггер контроля, нодключенный к блоку управления разрядным током, дешифратор адреса, подсоединенный к счетчику адреса, и блок контроля считанных сигналов.

Иедостатком известного устройства является 1малое быстродействие.

Описываемое устройство отличается от известного тем, что содержит триггер контроля четности адресов, вход которого иодключен к пересчетному триггеру, а выход - к триггеру коитроля, первую схему ИЛИ, входы которой подсоединеиы к последнему триггеру счетчика адреса и к лересчетному триггеру, блок управления коэффициентом пересчета, вход которого подключен к первой схеме ИЛИ, а выход - к счетчику разрушающих импульсов. Блок инвертирования содержит две схемы И, входы которых связаны с выходами последнего триггера счетчика адреса и триггера контроля четности адресов, и вторую схему ИЛИ, входы которой соединены с

выходами схем И, а выход - со входом пс)вого разряда дещифратора адреса, остальные входы которого подключены к соответствующим выходам триггеров счетчика адреса.

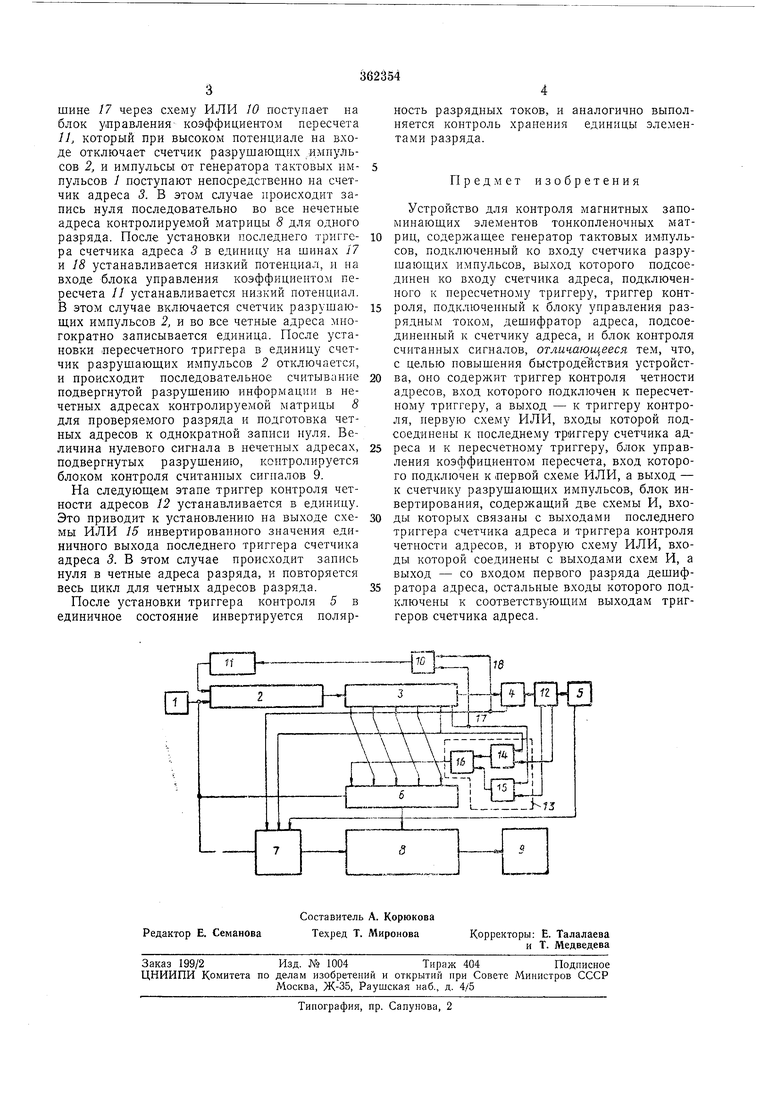

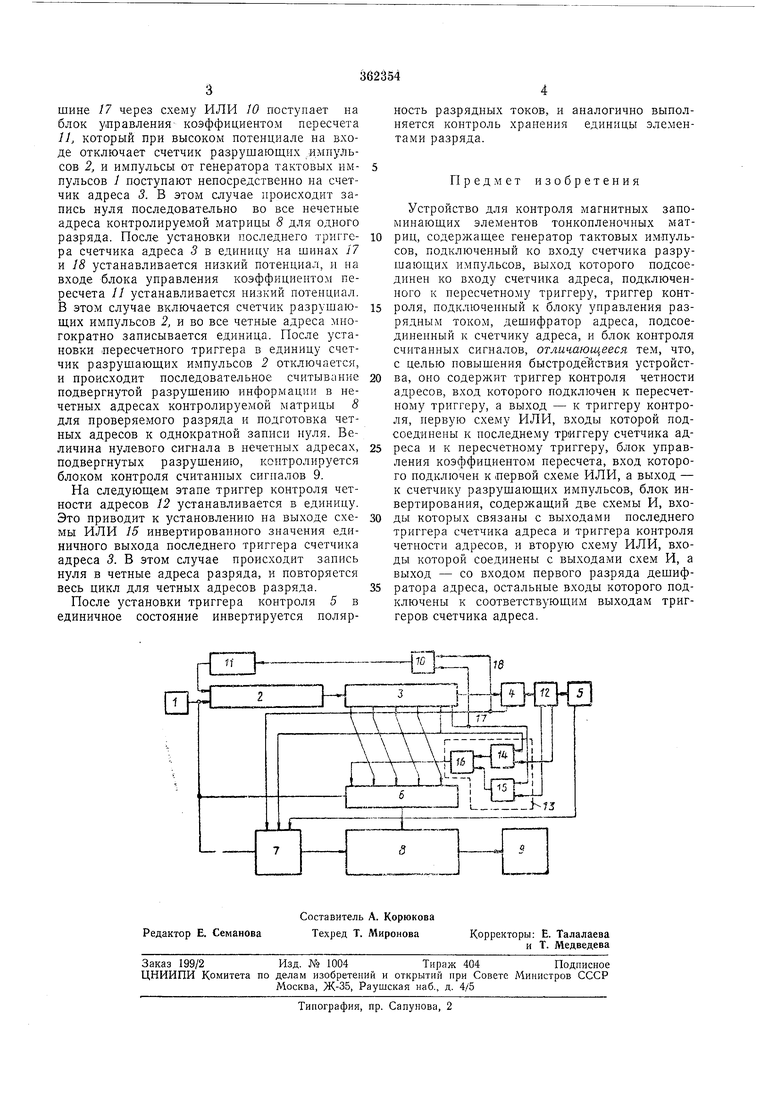

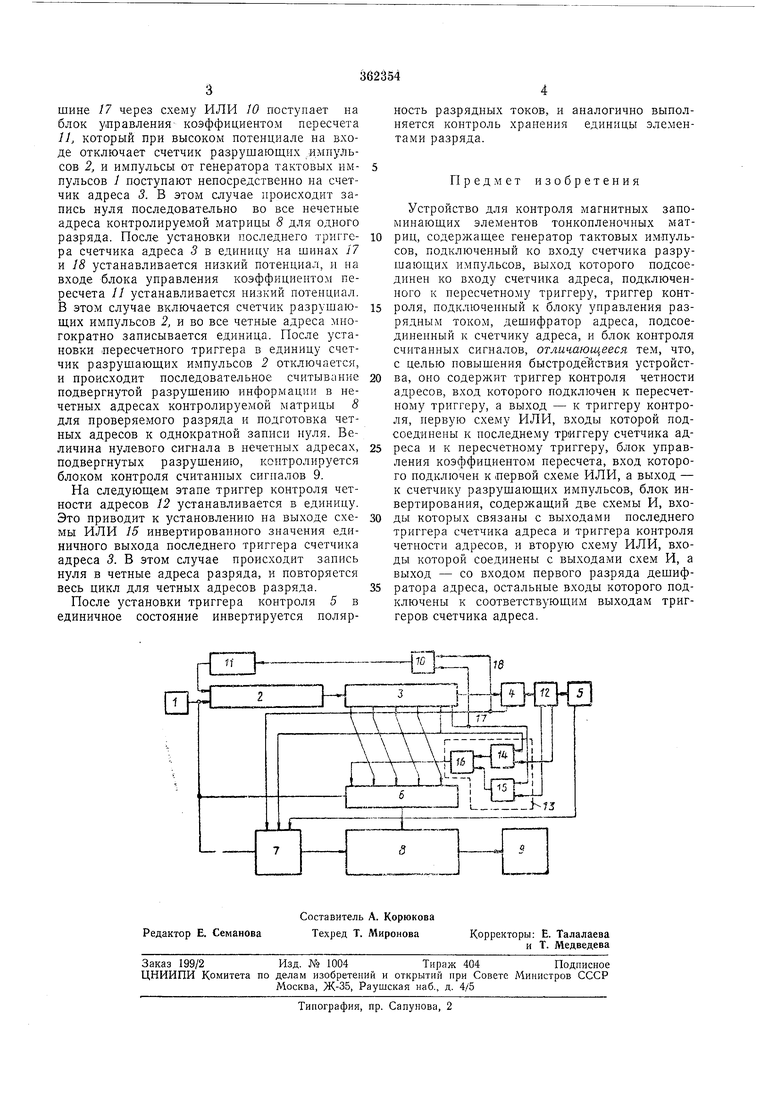

На чертеже изображена блок-схема устройства для контроля магнитных запоминающих элементов тонкопленочных матриц.

Устройство содержит генератор тактовых имнульсов /, счетчик разрушающих импульсов 2, счетчик адреса 3, нересчетный триггер 4, триггер контроля 5, дещнфратор адреса 6, блок управлення разрядным током 7, контролируемую матрицу 8, блок контроля считанных сигналов 9, нервую схему ИЛИ 10, блок унравления коэффициентом иересчета //, триггер коитроля четности адресов 12, блок инвертирования 13, содержащий схему И 14. схему И 15 и вторую схему ИЛИ 16. Кроме того, устройство содержит щину 17, связывающую нулевой выход носледнего трнггера счетчика адреса 3 со схемой И 15 и со схемой ИЛИ 10, щину 18, связывающую единичный выход пересчетпого триггера 4 со схелшй ИЛИ W п блоком управления разрядным током 7.

Устройство работает следующим образом.

В псходном положении все триггеры устройства находятся в нулевом состоянни, поэтому высокий потенциал на нулевом выходе носледнего триггера счетчика адреса 3 но

шине 17 через схему ИЛИ 10 поступает на блок управления коэффициентом пересчета 11, который при высоком потенциале на входе отключает счетчик разрушающих импульсов 2, и импульсы от генератора тактовых импульсов 1 поступают непосредственно на счетчик адреса 5. В этом случае происходит запись нуля последовательно во все нечетные адреса контролируемой матрицы 8 для одного разряда. После установки последнего триггера счетчика адреса 3 в единицу на шинах 17 и 18 устанавливается низкий потенциал, и на входе блока управления коэффициентом пересчета 11 устанавливается низкий потенциал. В этом случае включается счетчик разрушающих импульсов 2, и во все четные адреса многократно записывается единица. После установки пересчетного триггера в единицу счетчик разрушающих импульсов 2 отключается, и происходит последовательное считывание подвергнутой разрушению информации в нечетных адресах контролируемой матрицы 8 для проверяемого разряда и подготовка четных адресов к однократной записи нуля. Величина нулевого сигнала в нечетных адресах, подвергнутых разрушению, контролируется блоком контроля считанных сигналов 9.

На следующем этапе триггер контроля четности адресов 12 устанавливается в единицу. Это приводит к установлению на выходе схемы ИЛИ 15 инвертированного значения единичного выхода последнего триггера счетчика адреса 3. В этом случае происходит запись нуля в четные адреса разряда, и повторяется весь цикл для четных адресов разряда.

После установки триггера контроля 5 в единичное состояние инвертируется полярность разрядных токов, и аналогично выполняется контроль хранения единицы элементами разряда.

Предмет изобретения

Устройство для контроля магнитных запоминающих элементов тонкопленочных матриц, содержащее генератор тактовых импульсов, подключенный ко входу счетчика разрушающих импульсов, выход которого подсоединен ко входу счетчика адреса, подключенного к пересчетному триггеру, триггер контроля, подключенный к блоку управления разрядным током, дешифратор адреса, подсоединенный к счетчику адреса, и блок контроля считанных сигналов, отличаюш ееся тем, что, с целью повышения быстродействия устройства, оно содержит триггер контроля четности адресов, вход которого подключен к пересчетному триггеру, а выход - к триггеру контроля, первую схему ИЛИ, входы которой подсоединены к последнему триггеру счетчика адреса и к пересчетному триггеру, блок управления коэффициентом пересчета, вход которого подключен к первой схеме ИЛИ, а выход - к счетчику разрушающих импульсов, блок инвертирования, содержащий две схемы И, входы которых связаны с выходами последнего триггера счетчика адреса и триггера контроля четности адресов, и вторую схему ИЛИ, входы которой соединены с выходами схем И, а выход - со входом первого разряда дешифратора адреса, остальные входы которого подключены к соответствующим выходам триггеров счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема команд телеуправления | 1988 |

|

SU1667135A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Счетчик с контролем | 1983 |

|

SU1123106A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| УСТРОЙСТВО ДЛЯ НАКОПЛЕНИЯ И ОБРАБОТКИ ИНФОРМАЦИИ | 1973 |

|

SU384131A1 |

| ВСЕСОЮЗНАЯ Л. А. Шойхет, А. С. Белима, А. Г. Мелик-Аскаров, }j^,..^,..,.. ^^^,,,,.,.^^В. М. Гаврилюк, Б. И. Семеняк и А. А. Казьмина р^"—"!Н1'~1':ХН'''-;5\?{ЛЯ | 1970 |

|

SU287550A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

Авторы

Даты

1973-01-01—Публикация