1

Изобретение относится к дискретным элементам автоматики и вычислительной техники и предназначено для систем, выполненных на потенциальных элементах.

Известен триггер со счетным входом, который содержит основной и вспомогательный триггеры с раздельными входами, элементы И-НЕ « схему обнаружения ошибки, состоящую из дополнительного триггера и трех элементов И-НЕ, образующих полусумматор.

Недостатком известного счетного триггера является невозможность обнаружения неисправностей элемента И-НЕ, приводящих к появлению на его выходе нулевого сигнала. Причиной возможности появления необнаруживаемых неисправностей элементов триггера является наличие на их выходах в процессе работы устройства постоянных сигналов.

Таким образом, схема обнаружения ощибки прекращает выполнять функцию контроля при появлении отказов в трех элементах из четырех, что свидетельствует о ее малоэффективности.

Целью изобретения является повыщение достоверности обнаружения неисправностей элементов устройства.

Указанная цель достигается путем выполнения узла обнаружения ошибки в виде трех последовательно соединенных элементов сложения по mod 2, входы первого из которых соединены с источником контрольной последовательности импульсов и прямым выходом основного триггера, а вторые входы двух других элементов сложения соединены соответственно с инверсным выходом вспомогательного триггера и с шиной входного сигнала.

При таком выполнении узла обнаружения ошибки обеспечивается контроль входящих в его состав элементов за счет наличия на их

входах полного набора контрольных тестов (т. е. всех воз мольных комбинаций сигналов: 1 - 1,0-0, 0-1 и 1-0).

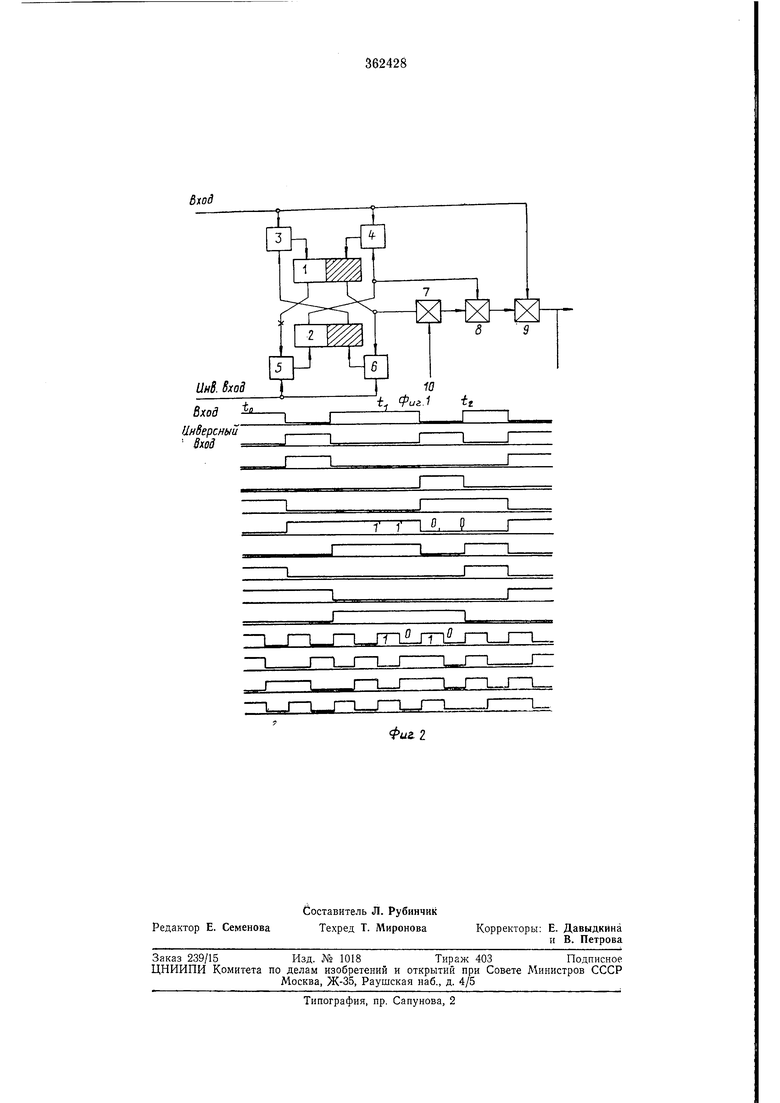

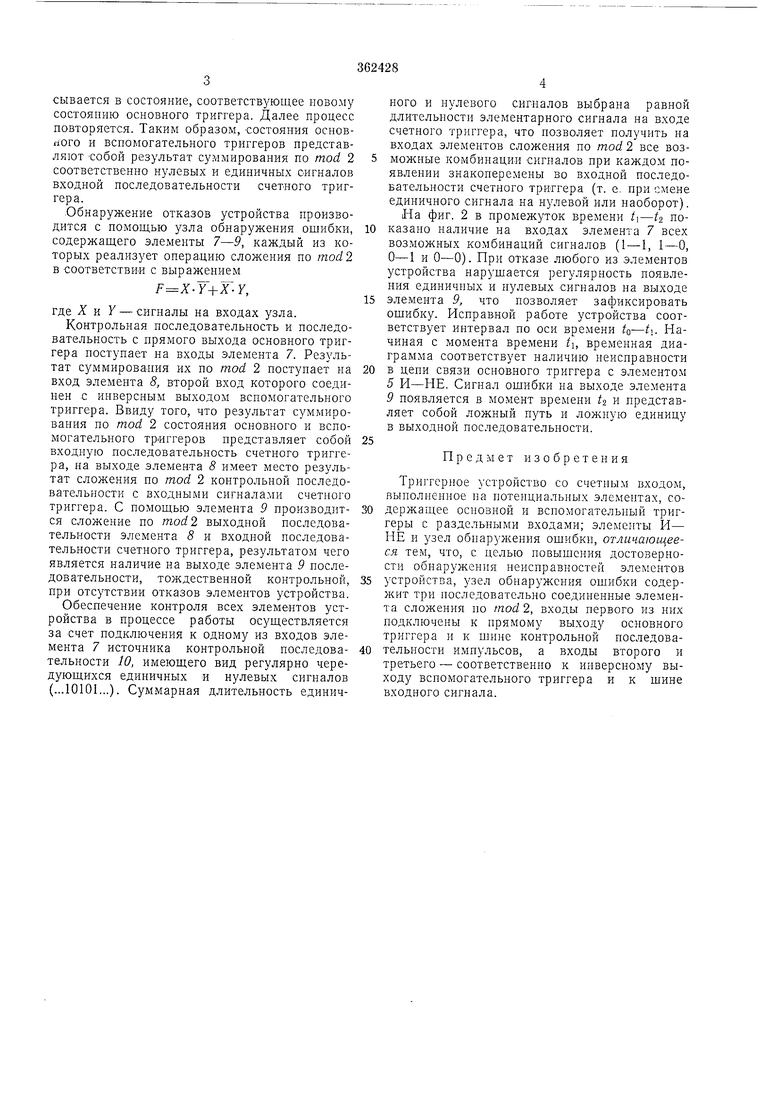

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 - временная диаграмма.

Устройство содержит соответственно основной и вспомогательный триггеры / и 2 с раздельными входами (элементами И-НЕ) 3-6 для переключения триггеров и элементы 7-9 сложения по mod 2, образующие узел обнаружения ощибки.

Работа устройства происходит следующим образом.

Основной триггер изменяет свое предыдущее состояние на противоположное при появлении нулевого сигнала на входе счетноготриггера (вспомогательный триггер в это время находится в прежнем состоянии). При появлении на входе счетного триггера единичного сигнала состояние основного триггера не

меняется, а вспомогательный триггер перебрасывается в состояние, соответствующее новому состоянию основного триггера. Далее процесс повторяется. Таким образом, состояния основного и вспомогательного триггеров представляют собой результат суммирования по mod 2 соответственно нулевых и единичных сигналов входной последовательности счетного триггера.

Обнаружение отказов устройства производится с помощью узла обнаружения ошибки, содержащего элементы 7-9, каждый из которых реализует операцию сложения по mod2 в соответствии с выражением

F X-Y+X-Y,

где X и Y - сигналы на входах узла.

Контрольная последовательность и последовательность с прямого выхода основного триггера поступает на входы элемента 7. Результат суммирования их по mod 2 поступает на вход элемента 8, второй вход которого соединен с инверсным выходом всномогательного триггера. Ввиду того, что результат суммирования по mod 2 состояния основного и вспомогательного триггеров представляет собой входную последовательность счетного триггера, на выходе элемента 8 имеет место результат слол ;ения по mod 2 контрольной последовательности с входными сигналами счетного триггера. С помощью элемента 9 производится сложение по mod 2 выходной последовательности элемента 5 и входной последовательности счетного триггера, результатом чего является наличие на выходе элемента 9 последовательности, тождественной контрольной, при отсутствии отказов элементов устройства.

Обеспечение контроля всех элементов устройства в процессе работы осуществляется за счет подключения к одному из входов элемента 7 источника контрольной последовательности 10, имеющего вид регулярно чередующихся единичных и нулевых сигналов (...10101...). Суммарная длительность единичного и нулевого сигналов выбрана равной длительности элементарного сигнала на входе счетного триггера, что позволяет получить на входах элементов сложения по mod 2 все воз5 можные комбинации сигналов при каждом появлении знакоперемены во входной последовательности счетного триггера (т. е. при смене единичного сигнала на нулевой или наоборот). На фиг. 2 в промежуток времени ti-t показано наличие на входах элемента 7 всех возможных комбинаций сигналов (1 - 1, 1-О, О-1 и О-0). При отказе любого из элементов устройства нарушается регулярность появления единичных и нулевых сигналов на выходе

5 элемента 9, что позволяет зафиксировать ошибку. Исправной работе устройства соответствует интервал по оси времени to-1. Начиная с момента времени /ь временная диаграмма соответствует наличию неисправности

0 в цепи связи основного триггера с элементом 5 Н-НЕ. Сигнал ошибки на выходе элемента 9 появляется в момент времени tz и представляет собой ложный путь и ложную единицу в выходной последовательности.

Нредмет изобретения

Триггерное устройство со счетным входом, выполненное на потенциальных элементах, содержащее основной и вспомогательный триггеры с раздельными входами; элементы Н- НЕ и узел обнаружения ошибки, отличающееся тем, что, с целью повышения достоверности обнаружения неисправностей элементов

устройства, узел обнаружения ошибки содержит три последовательно соединенные элемента сложения по mod 2, входы первого из них подключены к прямому выходу основного триггера и к шине контрольной последовательности импульсов, а входы второго и третьего - соответственно к инверсному выходу вспомогательного триггера и к щине входного сигнала.

Вход

Инверсный Sxod

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕР СО СЧЕТНЫМ ВХОДОМ | 1969 |

|

SU255986A1 |

| Триггерное устройство со счетнымВХОдОМ | 1979 |

|

SU805480A1 |

| Дешифратор с коррекцией ошибок | 1981 |

|

SU1012262A1 |

| Парафазное триггерное устройство со счетным входом | 1980 |

|

SU921048A1 |

| Устройство для вычисления контрольного элемента и обнаружения ошибок | 1986 |

|

SU1325483A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Адаптивный мажоритарный блок элементов "3 из 5" | 2021 |

|

RU2764839C1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для приема команд | 1973 |

|

SU458852A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

1 1 I О, Р

Авторы

Даты

1973-01-01—Публикация