1

Известны цифровые устройства для воспроизведения фазовых сдвигов, содержащие задающий генератор, связанный с делителем частоты, выходы которого соединены с одними входами блока сравнения, другие входы которого подключены к выходам блока установки кода фазового сдвига, счетный триггер, фильтры и схемы совпадения.

Однако известные устройства не обеспечивают требуемого диапазона преобразуемых частот.

С целью расщирения диапазона преобразуемых частот в предлагаемое устройство введены схема однозначности и схема неоднозначности и триггер с раздельным управлением, при этом выход счетного триггера соединен с первыми входами схем однозначности и неоднозначности, вторые входы которых подключены к выходу старщего разряда блока установки кода фазового сдвига, а выходы схем однозначности и неоднозначности соединены с одними входами схем совпадений, другие входы которых подключены к выходу блока сравнения, а выходы схем совпадения соединены с соответствующими входами триггера с раздельным управлением.

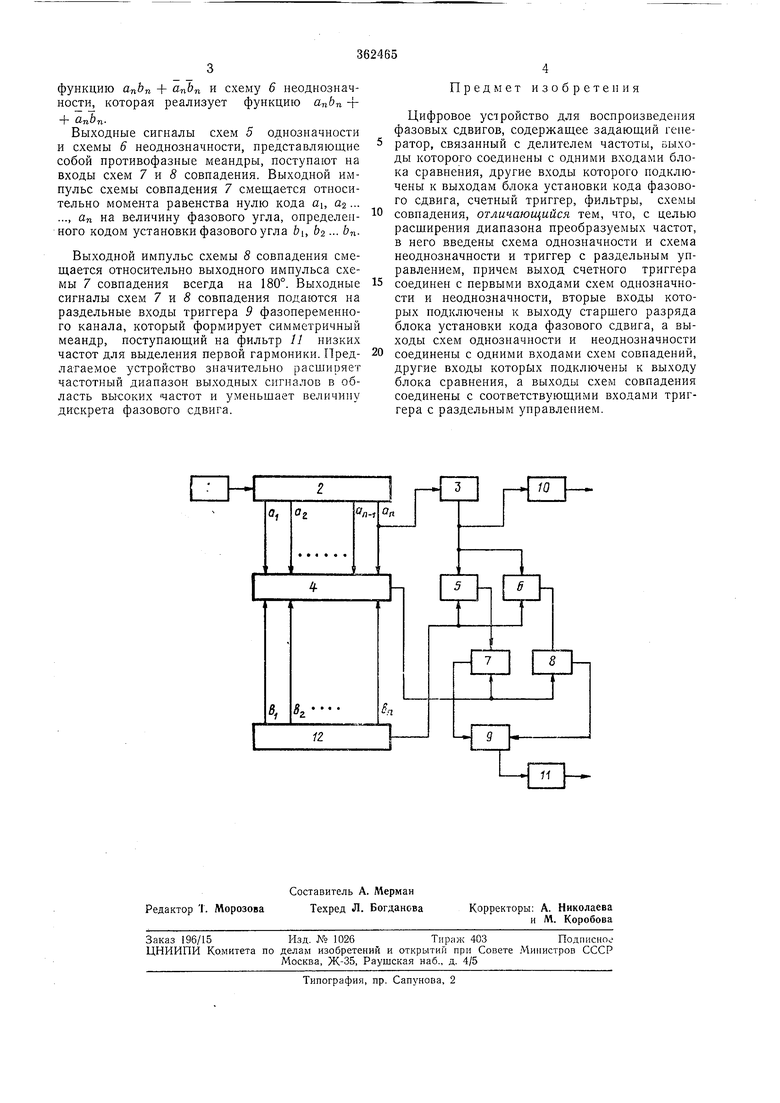

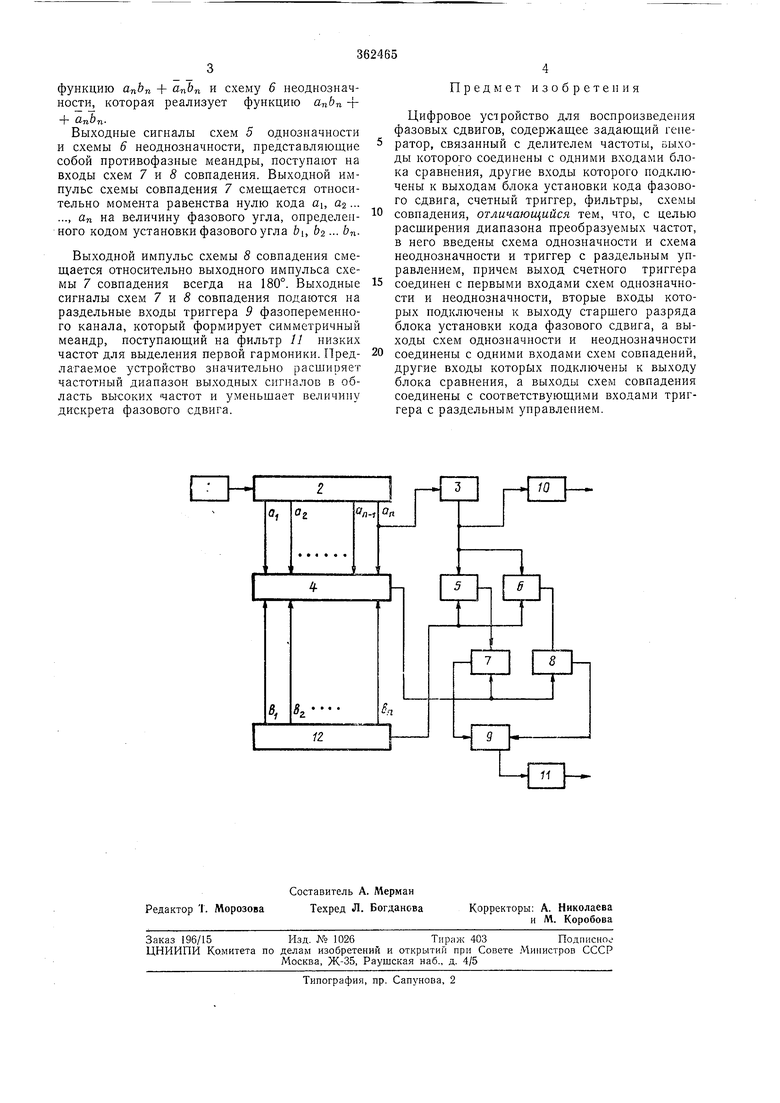

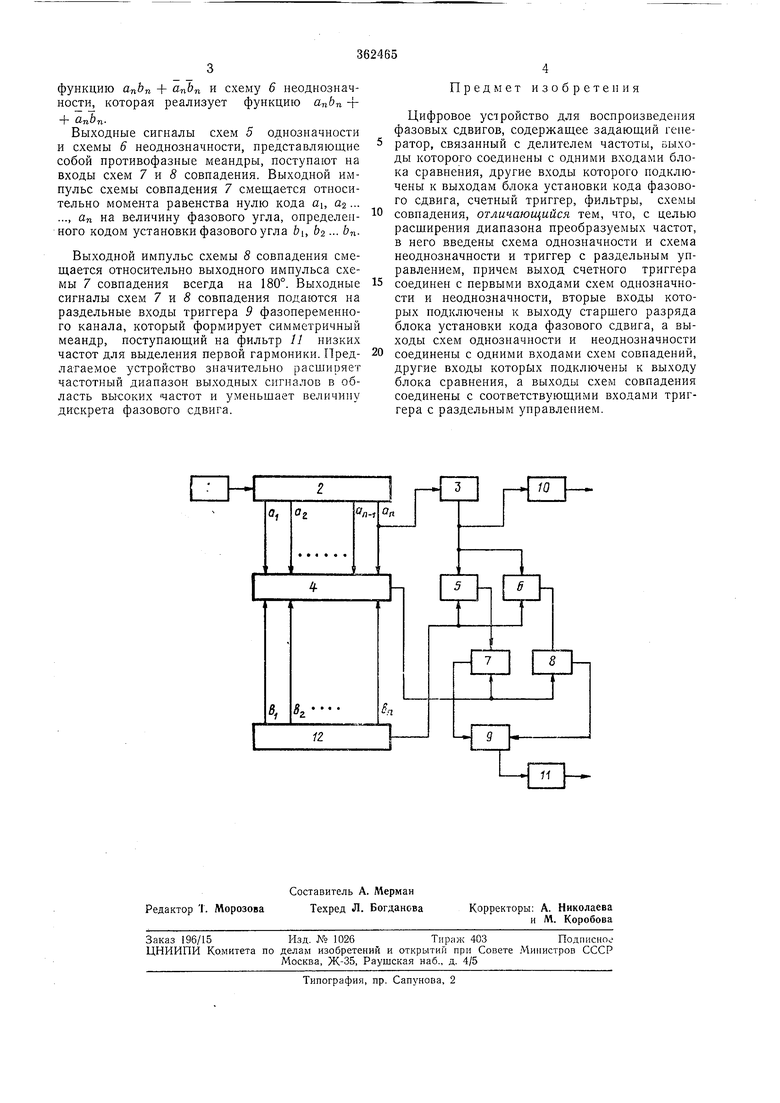

На чертеже приведена блок-схема предлагаемого устройства.

Предлагаемое цифровое устройство содержит задающий генератор /, делитель 2 частоТЫ, счетный триггер , блок 4 сравнения кодов, схему 5 однозначности, схему 6 неоднозначности, схемы 7 и S совпадения, триггер 9 с раздельными входами, фильтры 10 и 11 низких частот и блок 12 установки кода фазового сдвига.

Выходные импульсы задающего генератора / поступают на вход делителя 2 частоты, имеющего п - 1 разряд.

Выходной сигнал делителя 2 частоты поступает на счетный триггер 5, выход которого связан с фильтром 10 низкой частоты, с последнего снимается опорное напряжение.

Выходные сигналы разрядов делителя 2 частоты (переменный код Ci ... fln-i) поступают на блок 4 сравнения кодов, на другие входы которого заводятся все разряды, кроме старщего, кода bi... bn установки, поступающие с блока 12 установки кода фазового сдвига.

В моменты равенства кодов блок 4 сравнения кодов вырабатывает импульс, поступающий на схемы совпадения 7 и S. Со счетного триггера 3 вы.ходной сигнал кода а„ и старщий разряд кода Ьп с блока 12 установки кода фазового сдвига заведены на схему 5 однозначности, реализующую логическую

функцию unbn + cinbn и схему 6 неоднозначности, которая реализует функцию апЬп +

+ аиЬпВыходные сигналы схем 5 однозначности и схемы 6 неоднозначности, представляющие собой противофазные меандры, поступают на входы схем 7 и S совпадения. Выходной импульс схемы совпадения 7 смещается относительно момента равенства нулю кода а, а... ..., а-п на величину фазового угла, определенного кодом установки фазового угла bi, &2 пВыходной импульс схемы 8 совпадения смещается относительно выходного импульса схемы 7 совпадения всегда на 180°. Выходные сигналы схем 7 и S совпадения подаются на раздельные входы триггера 9 фазопеременного канала, который формирует симметричный меандр, поступающий на фильтр 11 низких частот для выделения первой гармоники. Предлагаемое устройство значительно расширяет частотный диапазон выходных сигналов в область высоких частот и уменьшает величину дискрета фазового сдвига.

Предмет изобретения

Цифровое устройство для воспроизведе}1ия фазовых сдвигов, содержащее задающий генератор, связанный с делителем частоты, выходы которого соединены с одними входами блока сравнения, другие входы которого подключены к выходам блока установки кода фазового сдвига, счетный триггер, фильтры, схемы совпадения, отличающийся тем, что, с целью расширения диапазона преобразуемых частот, в него введены схема однозначности и схема неоднозначности и триггер с раздельным управлением, причем выход счетного триггера соединен с первыми входами схем однозначности и неоднозначности, вторые входы которых подключены к выходу старшего разряда блока установки кода фазового сдвига, а выходы схем однозначности и неоднозначности соединены с однимн входами схем совпадений, другие входы которых подключены к выходу блока сравнення, а выходы схем совпадения соединены с соответствующими входами триггера с раздельным унравлеанем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для воспроизведения фазовых сдвигов | 1978 |

|

SU746322A1 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

| Преобразователь код-фаза | 1978 |

|

SU744973A1 |

| Многоканальный анализатор импульсов | 1974 |

|

SU476568A2 |

| Цифровой фазовращатель | 1978 |

|

SU748840A1 |

| Цифровой фазовращатель | 1984 |

|

SU1262712A1 |

| Автокорреляционный приемник сигналов с относительной фазовой модуляцией | 1981 |

|

SU1021015A1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1969 |

|

SU243281A1 |

| Многоотсчетный преобразователь перемещение-код | 1973 |

|

SU442501A1 |

W

/2

Авторы

Даты

1973-01-01—Публикация