1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в качестве выносного прибора для осциллографирования электрических сигналов.

Известны устройства для индикации электрических сигналов, содержащие блок квантования сигнала по уровню и времени, блок управления, блок памяти и индикаторное табло.

Предложенное устройство отличается от известных тем, что в его блок управления введены сдвигающий регистр, схемы совпадения, блок задержки, триггер, переключатель и коммутатор, причем вход сдвигающего регистра связан с щиной тактовых импульсов, а его выходы через схемы совпадения, соединенные с управляющими щинами, подключены к выходным шинам блока управления. Выход последней ячейки сдвигающего регистра через блок задержки нодсоединен к первым входам триггера и переключателя, вторые входы которых связаны соответственно с щиной установки и с щиной разрешения, причем выход триггера через коммутатор соединен со всеми ячейками сдвигающего регистра, а выход переключателя подключен к первой ячейке сдвигающего регистра.

Такое выполнение позволяет упростить устройство и повысить точность отсчета данных.

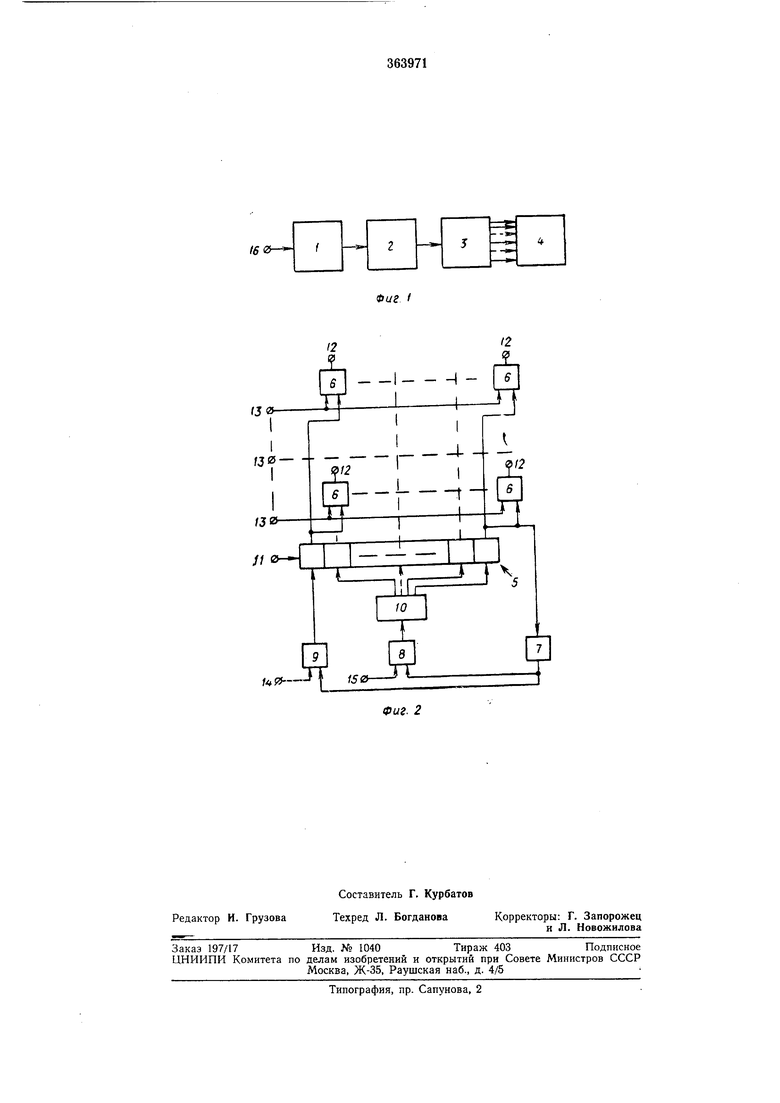

На фиг. 1 показана блок-схема устройства

для индикации электрических сигналов; на фиг. 2 - его блок управления.

Устройство содержит блок / квантования сигнала по уровню и времени, блок 2 управления, блок 5 памяти, индикаторное табло 4, сдвигающий регистр 5, схемы 6 совпадения, блок 7 задержки, триггер 8, переключатель 9, ком.мутатор 10, шину 11 тактовых импульсов, выходные щины 12 блока управления, управляющие щины 13, щину 14 разрешения, шину

15 установки и входную шину 16.

Устройство работает следующим образом.

Исследуемый сигнал по входной щине 16

подается на блок / квантования сигнала по

уровню и времени, с выхода которого в такты времени, соответствующие частоте квантования по времени, снимаются импульсы уровня сигнала, соответствующие дискретному отсчету исследуемого сигнала в данном такте

(фиг. 1). Частота квантования по времени и щаг дискретизации по уровню могут быть переменными и соответствовать частоте и амплитуде сигнала и требуемой точности осциллографирования.

Импульсы уровня сигнала с помощью блока 2 управления, осуществляющего распределение их по ячейкам блока 3 памяти, по выходным щинам 12 (фиг. 2), записываются в блок памяти. Каждая из ячеек блока памяти

управляет одним из элементов индикаторного

табло 4, расположенных в виде прямоугольной решетки, так что каждому такту времени соответствуют элементы определенного столбца, а каждому дискретному уровню сигнала- элементы определенной строки. Таким образом, записанный в блоке памяти сигнал (или его часть) индицируется на табло в виде прерывистой линии, изображающей зависимость величины сигнала от времени. В качестве индикаторных элементов могут быть использоваиы любые элементы, изменение состояния которых можно наблюдать.

Блок унравления обеснечивает не только управление записью и стнранием отсчетов сигнала, но и синхронизацию изображения сигнала на табло.

На вход сдвигающего регистра 5 (фиг. 2) по щине 11 тактовых импульсов подаются импульсы с частотой, равной частоте квантования сигнала. После срабатывания последней ячейки сдвигающего регистра, происходит сброс всех его ячеек в состояние «О и через блок 7 задержки и переключатель 9 вновь срабатывает первая ячейка сдвигающего регистра, т. е. обеспечивается цикличность его работы.

В режиме ждущей развертки включается первая ячейка сдвигающего регистра под действием сигнала определенного уровня, подаваемого с блока квантования сигналов но уровню и времени через шину 14 разрещения на один вход переключателя 9. Переключатель нронускает его в том случае, если неред ним имел место импульс с выхода блока 7 задержки. Регулируя задержку начала цикла развертки с помощью этого блока, можно обеспечить синхронизацию изображения сигнала на табло.

Запись импульсов, соответствующих дискретным уровням сигнала, в ячейки блока 5 памяти осуществляется с помощью схем 6 совпадения. В каждом такте срабатывает та схема совпадения, один вход которой подключен к возбужденной в этом такте ячейке сдвигающего регистра, а другой вход - к той управляющей шине 13, которой соответствует уровень сигнала в этом такте.

Импульсы с выхода схем совпадений через выходные щины 12 занисываются в соответствующие ячейки блока 3 памяти. В качестве ячеек блока памяти в описываемом варианте

можно использовать любые элементы с двумя устойчивыми состояниями (триггеры и т. д.). В каждом такте времени, наряду с записью, происходит стирание информации в тех ячейках блока паямти, которые соответствуют следующему такту времени. Для этого используют импульс с возбужденной ячейки сдвигающего регистра. Для сдвига изображения сигнала по оси

времени предусмотрен триггер 8, выход которого с помощью коммутатора 10 можно подсоединить к входу любой ячейки сдвигающего регистра. Триггер подготавливается к срабатыванию

«вручную с номощью кнопки (на чертеже не показана), нодключенной к одному входу триггера через шину 15 установки, и срабатывает от импульса с выхода блока задержки. При этом очередной цикл начинается с той ячейки

регистра, вход которой подключен к выходу триггера. Если изображение сигнала было предварительно синхронизировано, оно сдвигается на число тактов, равное норядковому номеру ячейки, подключенной к триггеру.

Предмет изобретения

Устройство для индикации электрических

сигналов, содержащее последовательно соединенные блок квантования сигнала по уровню и времени, блок управления, блок памяти и индикаторное табло, отличающееся тем, что, с целью упрощения устройства и повышения

точности отсчета данных, в нем блок управления содержит сдвигающий регистр, схемы совпадения, блок задержки, триггер, переключатель, коммутатор, причем вход сдвигающего регистра соединен с шиной тактовых имнульсов, а его выходы через схемы совпадения, связанные с управляющими шинами, подключены к выходным шинам, выход последней ячейки сдвигающего регистра через блок задержки подключен к первым входам триггера и переключателя, вторые входы которых соединены соответственно с шиной установки и с шиной разрешения, причем выход триггера через коммутатор связан с ячейками сдвигающего регистра, а выход переключателя

подключен к первой ячейке сдвигающего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ЦИЛИНДРИЧЕСКИХ МАГНИТНЫХ ПЛЕНКАХ | 1968 |

|

SU231224A1 |

| Устройство для отображения информации | 1974 |

|

SU493780A2 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для воспроизведения изображения на матричном экране | 1987 |

|

SU1596487A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР С ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ НА МАГНИТНОМ БАРАБАНЕ | 1966 |

|

SU182414A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

Авторы

Даты

1973-01-01—Публикация