Изобретение относится к радиотехнике и измерительной технике и может быть использовано для определения разности фаз двух сиг налов.

Цель изобретения - упрощение путем исключения операции логического инвертирования.

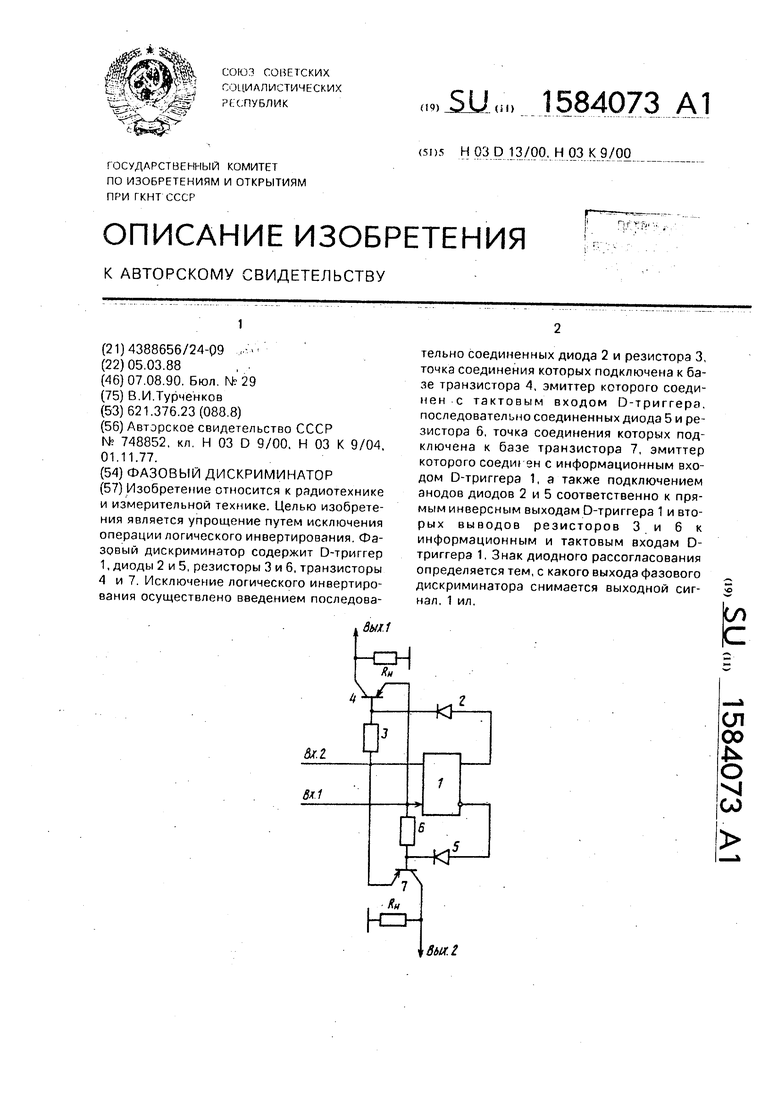

На чертеже представлена принципиальная электрическая схема предлагаемого фазового дискриминатора.

Фазовый дискриминатор содержит D- триггер 1, первый диод 2, первый резистор

3,первый транзистор 4, второй диод 5, второй резистор 6 и второй транзистор 7.

Фазовый дискриминатор работает еле- дующим образом.

Пусть сигнал на первом входе дискри минатора опережает по фазе сигнал на его втором входе. Тогда на прямом выходе D- триггера 1 удерживается сигнал логическо- го О, а на инверсном выходе - сигнал логической 1. Сигнал логической 1 через второй диод 5 поступает на базу второго транзистора 7 и запирает его. Появляющийся на первом входе фазового дискриминато- ра положительный импульс напряжения поступает на эмиттер первого транзистора

4,насыщает его током, протекающим через переход эмиттер-базу, первый резистор 3 и выходную часть источника сигнала по вто- рому входу. При этом на коллекторе первого транзистора 4 формируется передний фронт выходного напряжения.

В момент появления переднего фронта положительного импульса напряжения на втором входе дискриминатора первый транзистор 4 запирается и на его коллекторе формируется задний фронт выходного импульса. Длительность выходного импульса равна сдвигу фаз входных сигналов, опреде- ляемых по передним фронтам входных импульсов. В результате первый транзистор 4 находится в открытом состоянии только тогда, когда на первом входе фазового дискриминатора есть импульс, а на втором входе фазового дискриминатора его нет. При рассмотренном порядке поступления входных сигналов транзистор 7 постоянно находится в закрытом состоянии и на этом выходе дискриминатора импульсов нет В случае опережения импульса на втором входе фазового дискриминатора постоянно запертым является 1 ранзистор 4, а транзистор 7 отпирается на время, пропорциональное разности фаз входных сигналов. Знак фазового рассогласования определяется тем, с какого выхода фазового дискриминатора снимается выходной сигнал

Предлагаемый фазовый дискриминатор отличается уменьшенным расходом электроэнергии, поскольку питание должно подаваться только на один D-триггер. Упрощение устройства обеспечивается выполнением его только на одном D-триггере и шести элементарных элементах.

Формула изобретения Фазовый дискриминатор, содержащий D-триггер, тактовый и информационный входы которого являются первым и вторым входами фазового дискриминатора, отличающийся тем, что с целью упрощения путем исключения операции логического инвертирования, введены последовательно соединенные первый диод и первый резистор, точка соединения которых подключена к базе первого транзистора, эмиттер которого соединен с тактовым входом D- триггера. последовательно соединенные второй диод и второй резистор, точка соединения которых подключена к базе второго транзистора, эмиттер которого соединен с информационным входом D-триггера, при этом аноды первого и второго диодов соединены соответственно с прямым и инверсным выходами D-триггера, вторые выводы первого и второго резисторов соединены соответственно с информационным и тактовым входами D-триггера, причем коллекторы первого и второго транзисторов являются соответственно первым и вторым выходами фазового дискриминатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала | 1991 |

|

SU1770985A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1210215A1 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| Преобразователь последовательности импульсов | 1990 |

|

SU1813230A3 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1999 |

|

RU2211529C2 |

| Частотно-фазовый детектор | 1980 |

|

SU921043A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Дискриминатор-формирователь импульсов наносекундной длительности | 1983 |

|

SU1115212A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

Изобретение относится к радиотехнике и измерительной технике. Целью изобретения является упрощение путем исключения операции логического инвертирования. Фазовый дискриминатор содержит D-триггер 1, диоды 2 и 5, резисторы 3 и 6, транзисторы 4 и 7. Исключение логического инвертирования осуществлено введением последовательно соединенных диода 5 и резистора 6, точка соединения которых подключена к базе транзистора 7, эмиттер которого соединен с информационным входом D-триггера 1, а также подключением анодов диодов 2 и 5 соответственно к прямым и инверсным выходам D-триггера 1 и вторых выводов резисторов 3 и 6 к информационным и тактовым входам D-триггера 1. Знак диодного рассогласования определяется тем, с какого выхода фазового дискриминатора снимается выходной сигнал. 1 ил.

| Временной дискриминатор | 1977 |

|

SU748852A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-08-07—Публикация

1988-03-05—Подача