Изобретение относится к вычислительной технике, в частности к устройствам для передачи быстродействующих сигналов по длинным линиям связи в системах, использующих интегральные схемы транзисторно-транзисторной логики (ТТЛ).

Известны интегральные логические элементы, содержащие транзисторно-транзисторную схему «И-11Е с фазоинвертирующим транзисторо.м.

Иредлагаемый интегральный логический элемент для возбуждения длинных линий отличается от известных тем, что в него введены узел смещения, содержащий два транзистора и источник опорного напряжения, и узел защиты от коротких замыканий на двух транзисторах, в котором э.миттер первого и база второго транзисторов через резистор подключены к выходной шине и эмиттеру второго транзистора, а коллекторы транзисторов узла защиты от коротких замыканий соединены с коллектором фазоинвертирующего транзистора, подключенного эмиттером к базе первого транзистора узла смещения, в котором коллекторы транзисторов подключены к базе второго транзистора узла смещения и к базе первого транзистора узла защиты от коротких замыканий. Это позволяет повысить «адежность элемента яри возбуждении длинных линий.

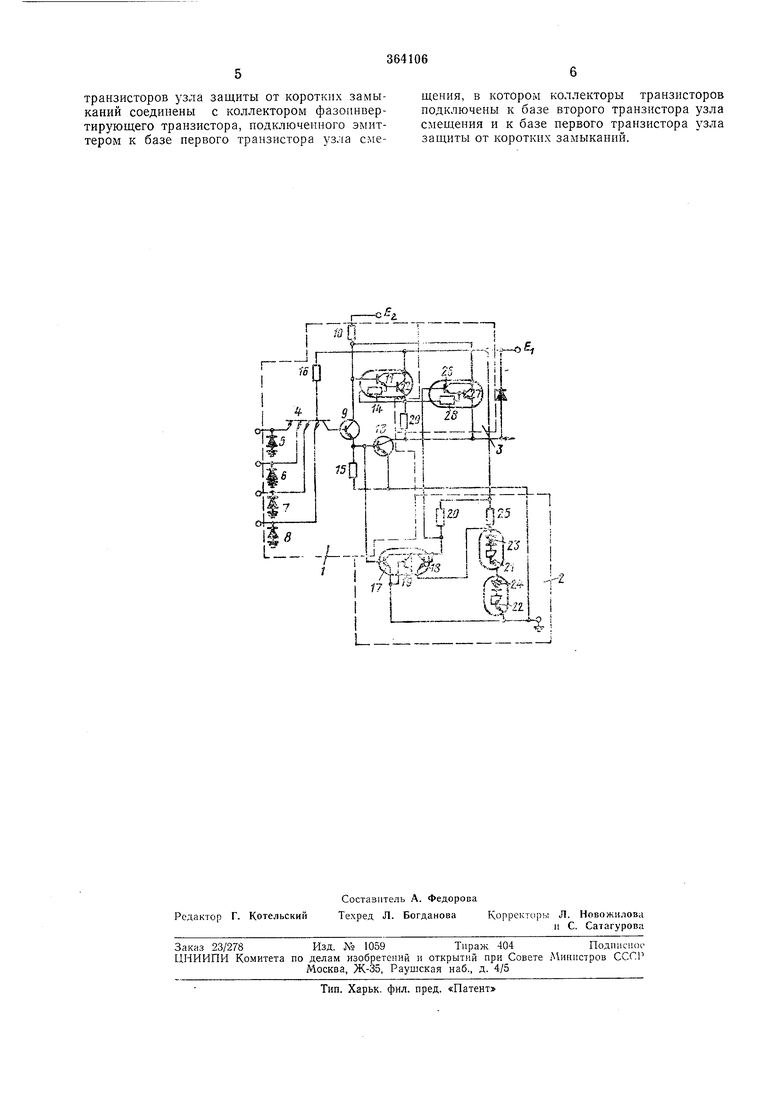

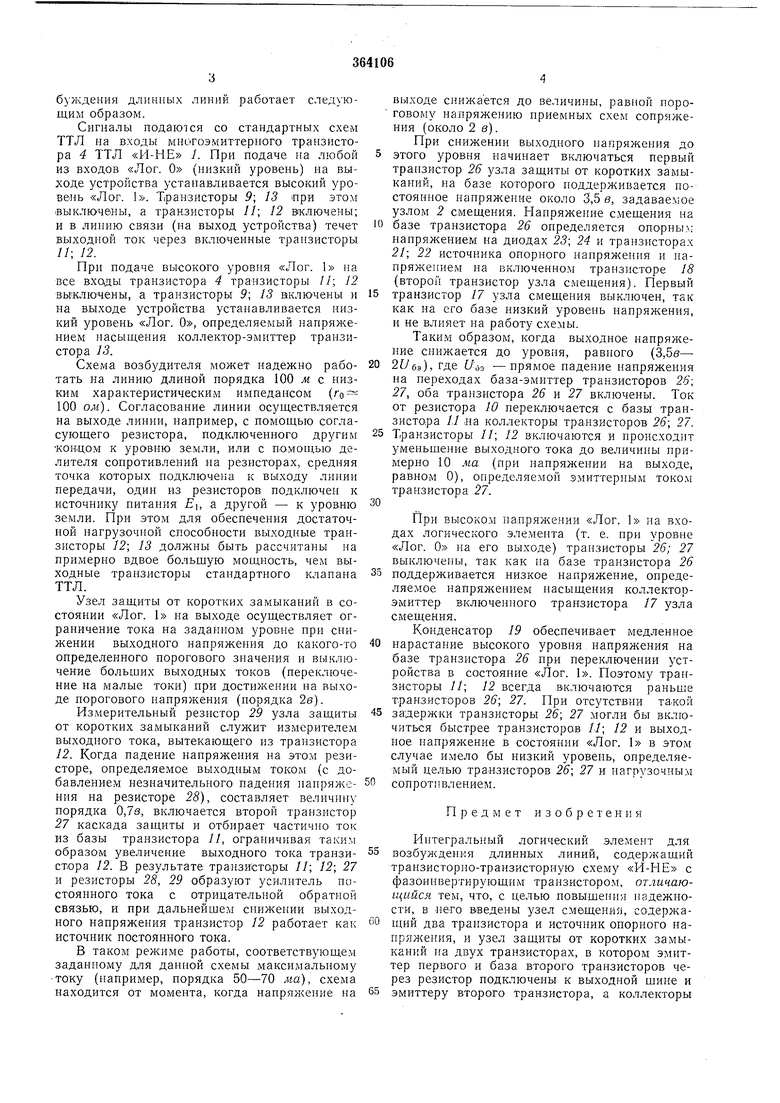

На чертеже показана нринциниальная схема предложенного интегрального логического элемента для возбуждения длинных линий.

Он содержит транзисторно-транзисторную схему «И-НЕ /, узел 2 смещения н узел о заи.1,иты от коротких замыканий.

Транзисторио-транзнсторная схема «И-ИЕ (ТТЛ «И-НЕ) / содержит .многоэмиттерный т-ранзистор (МЭТ) 4, на входах которого включены фикспрующне диоды 5-8 для ограничения искажений нз-за отражений в соединительных линиях; нсточник нитания /Гь фазоинвертнрующий транзистор 9, коллекторный резистор 10 которого подключен к донолнительному 1 сточн1 ку питания Е-2, причем для повьинения уровня «Лог. 1 выходных сигналов; транзисторы //; /2; 13; резисторы .

Узел 2 смещения содержит транзисторы 17; 18, ко;аденсатор /9 (выполнен на л)1тегральной схеме как транзистор), резистор 20, источник опорного напряжения на транзисторах 21; 22, диодах 23; 24 и резисторе 25.

Узел 3 защиты от коротких замыканий содержит транзисторы 26; 27, резисторы 28; 29.

Группы компонентов интегральной схемы

//; /2 и 14; 26; 27 и 28; 17; 18 и 19; 21 и 23;

22 и 24 выполнены каждая в одном обн1ем

изолированно.м кармане.

Интегральный логический элемент для возбуждения длинных линий работает следующим образом.

Сигналы подаются со стандартных схем ТТЛ на входы многоэмиттерного транзистора 4 ТТЛ «И-НЕ /. При подаче на любой из входов «Лог. О (низкий уровень) на выходе устройства устанавливается высокий уровень «Лог. 1. Транзисторы 9; 13 при этом сыклЕОЧбНы, а транзисторы 11; 12 включены; и в лииию связи (на выход устройства) течет выходной ток через включенные транзисторы //; 12.

При нодаче высокого уровня «Лог. 1 на все входы транзистора 4 транзисторы //; 12 выключены, а транзисторы 9; 13 вклЮчены и на выходе устройства устанавливается низкий уровень «Лог. О, определяемый напряжением насыщения коллектор-эмиттер транзистора 13.

Схема возбудителя может надежно работать на линию длиной порядка 100 м с низким характеристическим импедансом (го 100 ом). Согласование линии осуществляется на выходе линии, например, с помощью согласующего резистора, подключенного другим концом к уровню земли, или с п.омоп.ью делителя сопротивлений на резисторах, средняя точка которых подключена к выходу линии передачи, один из резисторов подключен к источнику питания Е, а другой - к уровню земли. При этом для обеспечения достаточной нагрузочной способности выходные транзисторы 12; 13 должны быть рассчитаны на примерно вдвое большую мощность, чем выходные транзисторы стандартного клапана ТТЛ.

Узел защиты от коротких замыканий в состоянии «Лог. 1 на выходе осуществляет ограничение тока на заданном уровне при снижении выходного напряжения до какого-то определенного порогового значения н выключение больщих выходных токов (переключение на малые токи) при достижении на выходе порогового напряжения (порядка 20).

Измерительный резистор 29 узла защиты от коротких замыканий служит измерителем выходного тока, вытекающего из транзистора 12. Когда падение напряжения на этом резисторе, определяемое выходным током (с добавлением незначительного падения напряжения на резисторе 28, составляет величину норядка 0,78, включается второй транзистор 27 каскада защиты и отбирает частично ток из базы транзистора //, ограничивая таким образом увеличение выходного тока транзистора 12. В результате транзи1сто,ры 11; 12; 27 и резисторы 28, 29 образуют усилитель постоянного тока с отрицательной обратной связью, и при дальнейшем снижении выходного напряжения транзистор 12 работает как источник постоянного тока.

В таком режиме работы, соответствующем

заданному для данной схемы максимальному

току (например, порядка 50-70 ма), схема

находится от момента, когда напряжение на

выходе снижается до величины, равной пороговому напряжению нриемных схем сопряжения (около 2 в).

При снижении выходного напряжения до 5 этого уровня начинает включаться первый транзистор 26 узла защиты от коротких замыканий, на базе которого ноддерживается постоянное напряжение около 3,5 в, задаваемое узлом 2 смещения. Напряжение смещения на 10 базе транзистора 26 определяется опорным напряжением на днодах 23; 24 и транзисторах 21; 22 источника опорного нанряжения и напряжением на включенном транзисторе 13 (второй транзистор узла смещения). Первый

5 транзистор 17 узла смещения выключен, так как на его базе низкий уровень напряжения, и не влияет на работу схемы.

Таким образом, когда выходное напряжение снижается до уровня, равного (3,5б-

0 и&а), где f/оэ -прямое падение напряжения на переходах база-эмиттер транзисторов 26; 27, оба транзистора 26 и 27 включены. Ток от резистора 10 переключается с базы транзистора 11 на коллекторы транзисторов 26; 27. 5 Транзисторы //; 12 включаются и происходит уменьшение выходного тока до величины примерно 10 ма (при напряжении на выходе, равном 0), определяемой эмиттерным током транзистора 27.

При высоком напряжении «Лог. 1 на входах логического элемента (т. е. нри уровне «Лог. О на его выходе) транзисторы 26; 27 выключены, так как на базе транзистора 26

а поддерживается низкое напряжение, определяемое напряжением иасыщения коллекторэмиттер включенного транзистора 17 узла смещения.

Конденсатор 19 обеспечивает медленное

0 нарастание высокого уровня нанряжения на базе транзистора 26 при переключении устройства в состояние «Лог. 1. Поэтому транзисторы 11; 12 всегда включаются раньн1е транзисторов 26; 27. При отсутствии такой

5 задержки транзисторы 26; 27 могли бы включиться быстрее транзисторо,в /./; 12 и выходное напряжение в состоянии «Лог. 1 в этом случае имело бы низкий уровень, определяемый целью транзисторов 26; 27 и нагрузочным сопротивлением.

Предмет изобретения

Интегральный логический элемент для 5 возбуждения длинных линий, содержащий транзисторно-транзисторную схему «И-НЕ с фазоннвертирующим транзистором, отличающийся тем, что, с целью повышения надежности, в него введены узел смещения, содержа0 щий два транзистора и источник опорного нанряжения, и узел защиты от коротких замыканий на двух транзисторах, в котором эмиттер первого и база второго транзисторов через резистор подключены к выходной шине и 5 эмиттеру второго транзистора, а коллекторы

транзисторов узла защиты от коротких замыканий соединены с коллектором фазоннвертирующего транзистора, подключенного эмиттером к базе первого транзистора узла смещения, в котором коллекторы транзисторов подключены к базе второго транзистора узла смещения и к базе первого транзистора узла защиты от коротких замыканий.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1983 |

|

SU1125765A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| Стабилизированный источник питания | 1985 |

|

SU1265745A1 |

| Устройство для защиты преобразователя | 1984 |

|

SU1160502A1 |

| Стабилизатор постоянного напряжения с защитой | 1983 |

|

SU1140107A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| ПЕРЕДАТЧИК МУЛЬТИПЛЕКСНОЙ МАНЧЕСТЕРСКОЙ ЛИНИИ СВЯЗИ | 2002 |

|

RU2229769C2 |

8

/j.:rr7,-:.J

Щ2-.

Авторы

Даты

1973-01-01—Публикация